# **CprE 281: Digital Logic**

**Instructor: Alexander Stoytchev**

http://www.ece.iastate.edu/~alexs/classes/

# **Multiplexers**

CprE 281: Digital Logic Iowa State University, Ames, IA Copyright © Alexander Stoytchev

#### **Administrative Stuff**

HW 6 is due on Monday

#### **Administrative Stuff**

• HW 7 is out

It is due on Monday Oct 19 @ 4pm

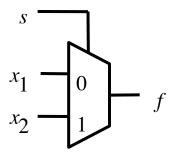

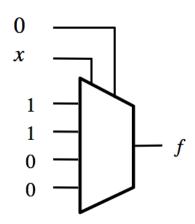

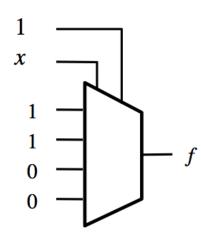

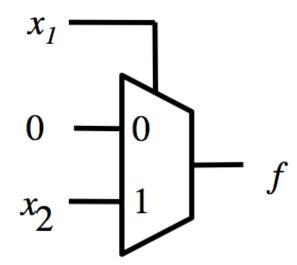

# 2-1 Multiplexer (Definition)

- Has two inputs: x<sub>1</sub> and x<sub>2</sub>

- Also has another input line s

- If s=0, then the output is equal to x<sub>1</sub>

- If s=1, then the output is equal to x<sub>2</sub>

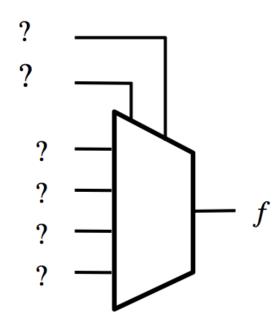

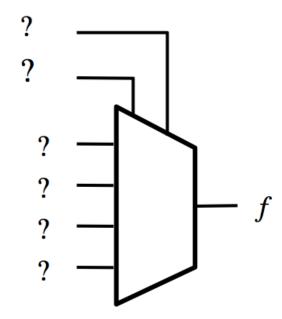

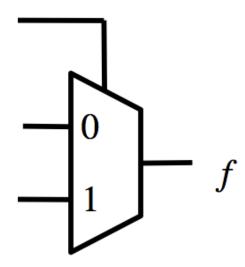

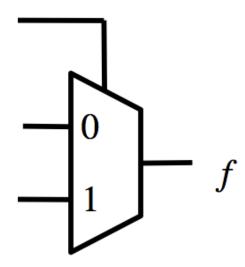

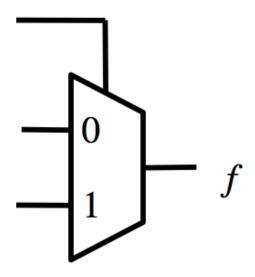

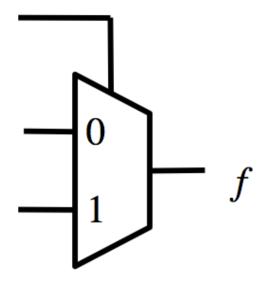

## **Graphical Symbol for a 2-1 Multiplexer**

# Truth Table for a 2-1 Multiplexer

| $s x_1 x_2$ | $f(s, x_1, x_2)$ |

|-------------|------------------|

| 000         | 0                |

| 001         | 0                |

| 010         | 1                |

| 0 1 1       | 1                |

| 100         | 0                |

| 101         | 1                |

| 110         | 0                |

| 111         | 1                |

| $s x_1 x_2$ | $f(s, x_1, x_2)$ |

|-------------|------------------|

| 000         | 0                |

| 0 0 1       | 0                |

| 010         | 1                |

| 0 1 1       | 1                |

| 100         | 0                |

| 101         | 1                |

| 110         | 0                |

| 111         | 1                |

| $s x_1 x_2$ | $f(s, x_1, x_2)$ |

|-------------|------------------|

| 000         | 0                |

| 001         | 0                |

| 010         | 1                |

| 0 1 1       | 1                |

| 100         | 0                |

| 101         | 1                |

| 110         | 0                |

| 111         | 1                |

| $s x_1 x_2$ | $f(s, x_1, x_2)$ |

|-------------|------------------|

| 000         | 0                |

| 001         | 0                |

| 010         | 1                |

| 0 1 1       | 1                |

| 100         | 0                |

| 101         | 1                |

| 110         | 0                |

| 111         | 1                |

Where should we put the negation signs?

$$s x_1 x_2$$

$$s x_1 x_2$$

$$s x_1 x_2$$

$$s x_1 x_2$$

| $s x_1 x_2$ | $f(s, x_1, x_2)$ |                                   |

|-------------|------------------|-----------------------------------|

| 000         | 0                |                                   |

| 001         | 0                |                                   |

| 010         | 1                | $\overline{s} x_1 \overline{x}_2$ |

| 0 1 1       | 1                | $\overline{s} x_1 x_2$            |

| 100         | 0                |                                   |

| 101         | 1                | $s \overline{x_1} x_2$            |

| 110         | 0                |                                   |

| 111         | 1                | $s x_1 x_2$                       |

| $s x_1 x_2$ | $f(s, x_1, x_2)$ |                                   |

|-------------|------------------|-----------------------------------|

| 000         | 0                |                                   |

| 0 0 1       | 0                |                                   |

| 010         | 1                | $\overline{s} x_1 \overline{x}_2$ |

| 0 1 1       | 1                | $\overline{s} x_1 x_2$            |

| 100         | 0                |                                   |

| 101         | 1                | $s \overline{x_1} x_2$            |

| 110         | 0                |                                   |

| 111         | 1                | $s x_1 x_2$                       |

$$f(s, x_1, x_2) = \overline{s} x_1 \overline{x_2} + \overline{s} x_1 x_2 + s \overline{x_1} x_2 + s x_1 x_2$$

## Let's simplify this expression

$$f(s, x_1, x_2) = \overline{s} x_1 \overline{x}_2 + \overline{s} x_1 x_2 + s \overline{x}_1 x_2 + s x_1 x_2$$

### Let's simplify this expression

$$f(s, x_1, x_2) = \overline{s} x_1 \overline{x_2} + \overline{s} x_1 x_2 + s \overline{x_1} x_2 + s x_1 x_2$$

$$f(s, x_1, x_2) = \overline{s} x_1 (\overline{x_2} + x_2) + s (\overline{x_1} + x_1) x_2$$

### Let's simplify this expression

$$f(s, x_1, x_2) = \overline{s} x_1 \overline{x}_2 + \overline{s} x_1 x_2 + s \overline{x}_1 x_2 + s x_1 x_2$$

$$f(s, x_1, x_2) = \overline{s} x_1 (\overline{x_2} + x_2) + s (\overline{x_1} + x_1) x_2$$

$$f(s, x_1, x_2) = \overline{s} x_1 + s x_2$$

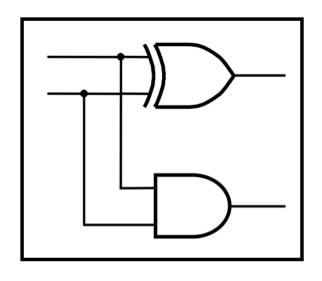

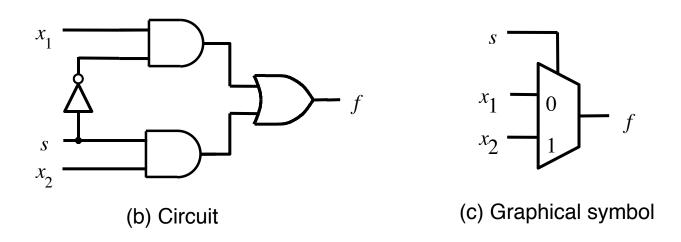

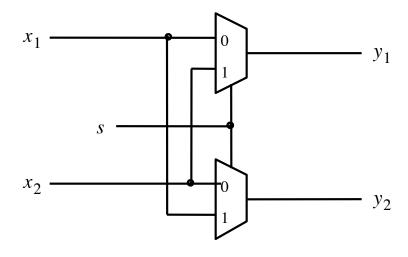

## Circuit for 2-1 Multiplexer

$$f(s, x_1, x_2) = \overline{s} x_1 + s x_2$$

## More Compact Truth-Table Representation

| $s x_1 x_2$ | $f(s, x_1, x_2)$ |

|-------------|------------------|

| 0 0 0       | 0                |

| 0 0 1       | 0                |

| 010         | 1                |

| 0 1 1       | 1                |

| 100         | 0                |

| 101         | 1                |

| 110         | 0                |

| 111         | 1                |

(a)Truth table

| S | $f(s, x_1, x_2)$ |

|---|------------------|

| 0 | $x_1$            |

| 1 | $x_2$            |

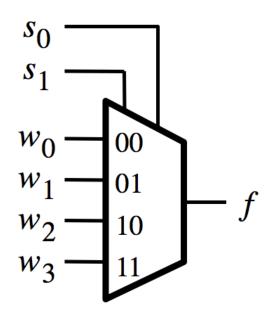

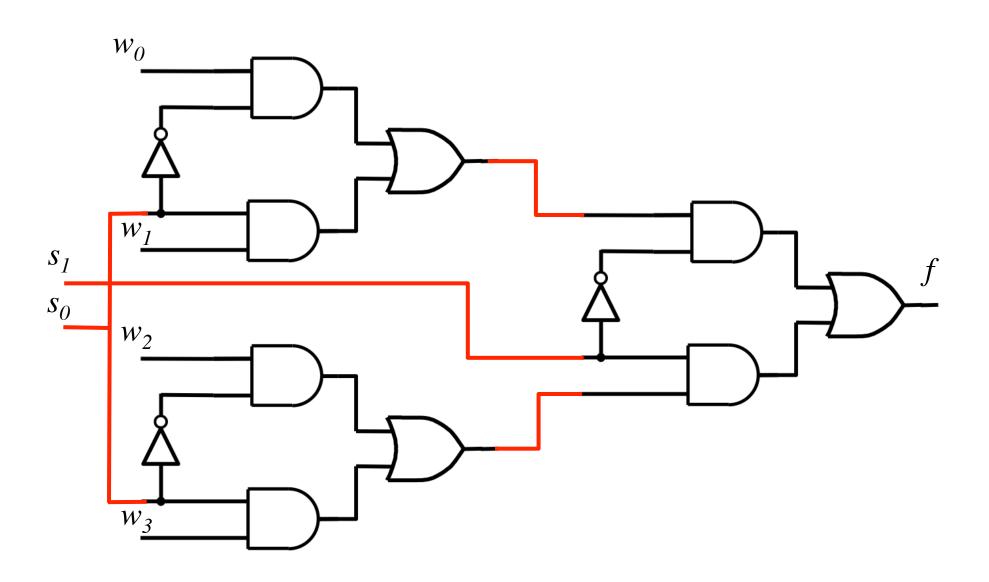

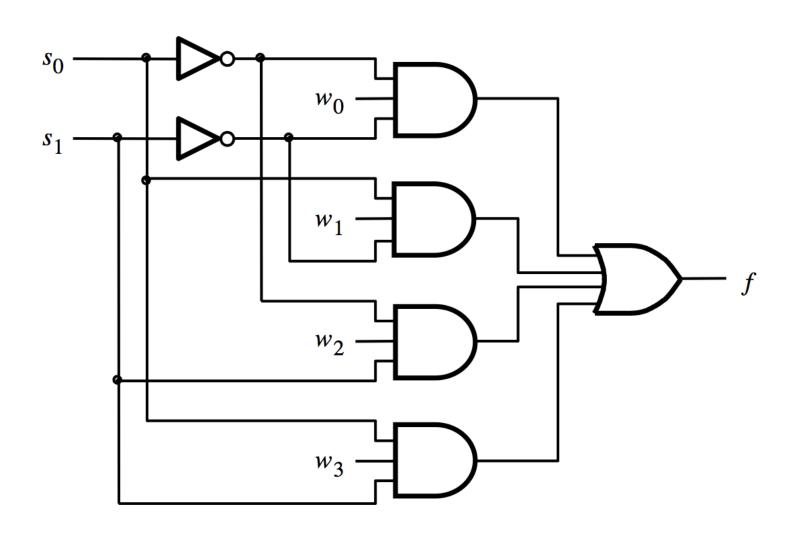

# 4-1 Multiplexer (Definition)

- Has four inputs:  $w_0$ ,  $w_1$ ,  $w_2$ ,  $w_3$

- Also has two select lines: s<sub>1</sub> and s<sub>0</sub>

- If s<sub>1</sub>=0 and s<sub>0</sub>=0, then the output f is equal to w<sub>0</sub>

- If s<sub>1</sub>=0 and s<sub>0</sub>=1, then the output f is equal to w<sub>1</sub>

- If  $s_1=1$  and  $s_0=0$ , then the output f is equal to  $w_2$

- If  $s_1=1$  and  $s_0=1$ , then the output f is equal to  $w_3$

## **Graphical Symbol and Truth Table**

(a) Graphic symbol

| <i>s</i> <sub>1</sub> | $s_0$ | f     |

|-----------------------|-------|-------|

| 0                     | 0     | $w_0$ |

| 0                     | 1     | $w_1$ |

| 1                     | 0     | $w_2$ |

| 1                     | 1     | $w_3$ |

(b) Truth table

# The long-form truth table

# The long-form truth table

| $S_1S_0$ | I <sub>3</sub> I <sub>2</sub> I <sub>1</sub> I <sub>0</sub> | F S <sub>1</sub> S <sub>0</sub> | I <sub>3</sub> I <sub>2</sub> I <sub>1</sub> I <sub>6</sub> | F S <sub>1</sub> S <sub>0</sub> | I <sub>3</sub> I <sub>2</sub> I <sub>1</sub> I <sub>0</sub> F | S <sub>1</sub> S <sub>0</sub> I <sub>3</sub> I <sub>2</sub> I <sub>1</sub> I <sub>0</sub> F |

|----------|-------------------------------------------------------------|---------------------------------|-------------------------------------------------------------|---------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 0 0      | 0 0 0 0                                                     | 0 0 1                           | 0 0 0 0                                                     | 0 1 0                           | 0 0 0 0 0                                                     | 1 1 0 0 0 0 0                                                                               |

|          | 0 0 0 1                                                     | 1                               | 0 0 0 1                                                     | 0                               | 0 0 0 1 0                                                     | 0 0 0 1 0                                                                                   |

|          | 0 0 1 0                                                     | 0                               | 0 0 1 0                                                     | 1                               | 0 0 1 0 0                                                     | 0 0 1 0 0                                                                                   |

|          | 0 0 1 1                                                     | 1                               | 0 0 1 1                                                     | 1                               | 0 0 1 1 0                                                     | 0 0 1 1 0                                                                                   |

|          | 0 1 0 0                                                     | 0                               | 0 1 0 0                                                     | 0                               | 0 1 0 0 1                                                     | 0 1 0 0 0                                                                                   |

|          | 0 1 0 1                                                     | 1                               | 0 1 0 1                                                     | 0                               | 0 1 0 1 1                                                     | 0 1 0 1 0                                                                                   |

|          | 0 1 1 0                                                     | 0                               | 0 1 1 0                                                     | 1                               | 0 1 1 0 1                                                     | 0 1 1 0 0                                                                                   |

|          | 0 1 1 1                                                     | 1                               | 0 1 1 1                                                     | 1                               | 0 1 1 1 1                                                     | 0 1 1 1 0                                                                                   |

|          | 1 0 0 0                                                     | 0                               | 1 0 0 0                                                     | 0                               | 1 0 0 0 0                                                     | 1 0 0 0 1                                                                                   |

|          | 1 0 0 1                                                     | 1                               | 1 0 0 1                                                     | 0                               | 1 0 0 1 0                                                     | 1 0 0 1 1                                                                                   |

|          | 1 0 1 0                                                     | 0                               | 1 0 1 0                                                     | 1                               | 1 0 1 0 0                                                     | 1 0 1 0 1                                                                                   |

|          | 1 0 1 1                                                     | 1                               | 1 0 1 1                                                     | 1                               | 1 0 1 1 0                                                     | 1 0 1 1 1                                                                                   |

|          | 1 1 0 0                                                     | 0                               | 1 1 0 0                                                     | 0                               | 1 1 0 0 1                                                     | 1 1 0 0 1                                                                                   |

|          | 1 1 0 1                                                     | 1                               | 1 1 0 1                                                     | 0                               | 1 1 0 1 1                                                     | 1 1 0 1 1                                                                                   |

|          | 1 1 1 0                                                     | 0                               | 1 1 1 0                                                     | 1                               | 1 1 1 0 1                                                     | 1 1 1 0 1                                                                                   |

|          | 1 1 1 1                                                     | 1                               | 1 1 1 1                                                     | 1                               | 1 1 1 1 1                                                     | 1 1 1 1 1                                                                                   |

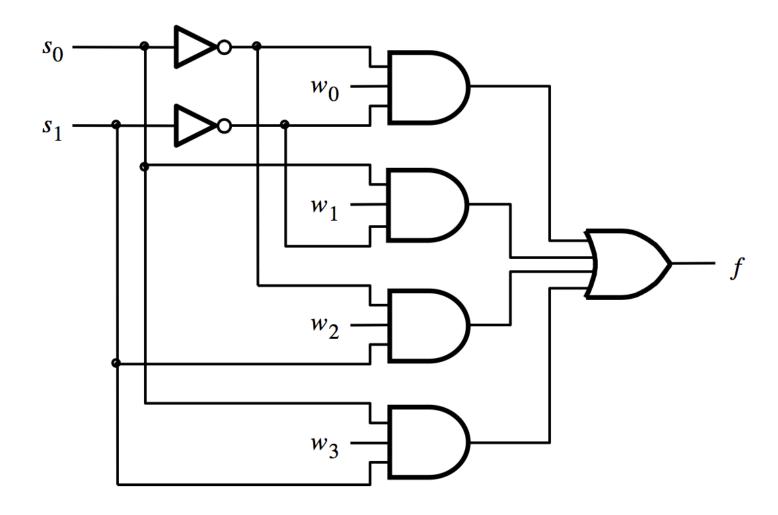

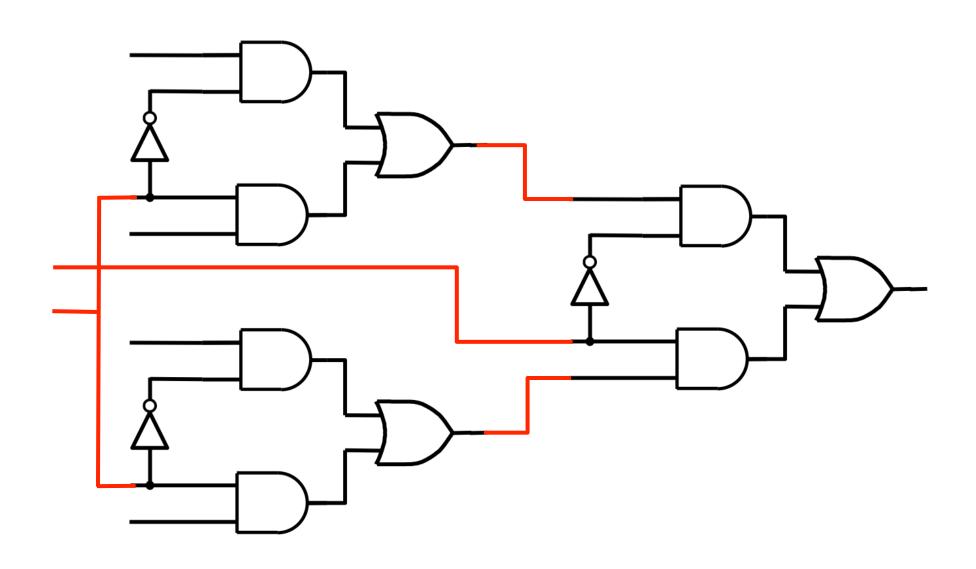

## 4-1 Multiplexer (SOP circuit)

$$f = \overline{s_1} \, \overline{s_0} \, w_0 + \overline{s_1} \, s_0 \, w_1 + s_1 \, \overline{s_0} \, w_2 + s_1 \, s_0 \, w_3$$

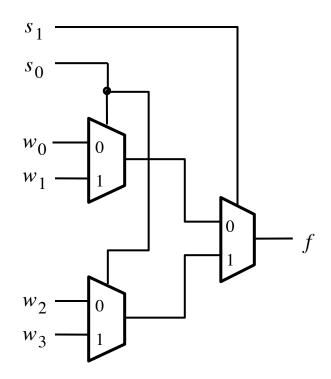

# That is different from the SOP form of the 4-1 multiplexer shown below, which uses less gates

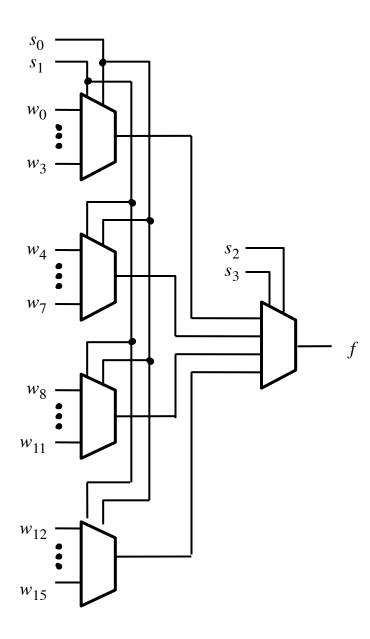

# **16-1 Multiplexer**

[ Figure 4.4 from the textbook ]

# **Multiplexers Are Special**

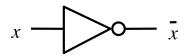

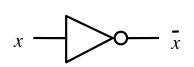

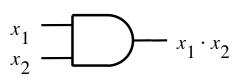

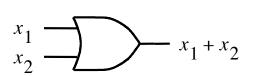

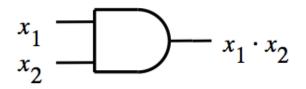

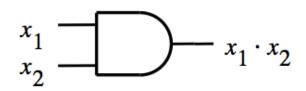

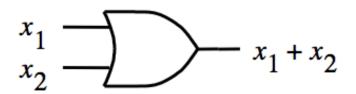

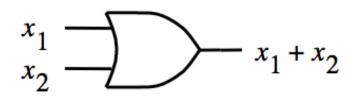

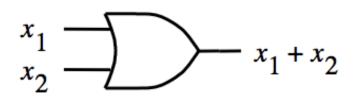

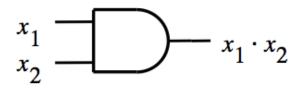

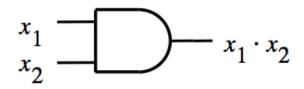

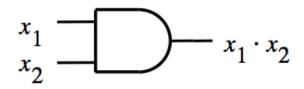

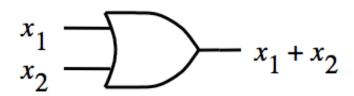

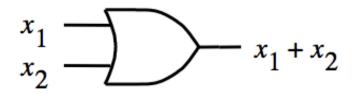

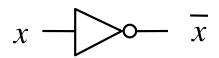

## The Three Basic Logic Gates

$$x_1$$

$x_2$

$x_1 \cdot x_2$

$$x_1$$

$x_2$

$x_1 + x_2$

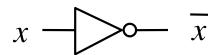

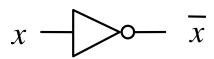

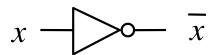

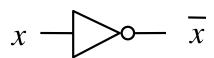

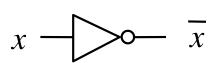

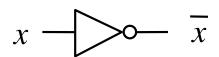

NOT gate

AND gate

OR gate

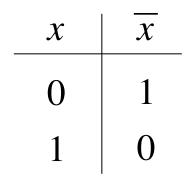

### **Truth Table for NOT**

| <i>X</i> | $\overline{x}$ |

|----------|----------------|

| 0        | 1              |

| 1        | 0              |

### **Truth Table for AND**

| $x_1$            | $x_2$       | $x_1 \cdot x_2$  |

|------------------|-------------|------------------|

| 0<br>0<br>1<br>1 | 0<br>1<br>0 | 0<br>0<br>0<br>1 |

### **Truth Table for OR**

| $x_1$ | $x_2$ | $x_1 + x_2$ |

|-------|-------|-------------|

| 0     | 0     | 0           |

| 0     | 1     | 1           |

| 1     | 0     | 1           |

| 1     | 1     | 1           |

|       |       | 1           |

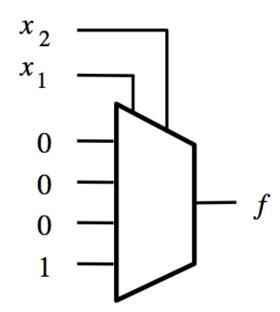

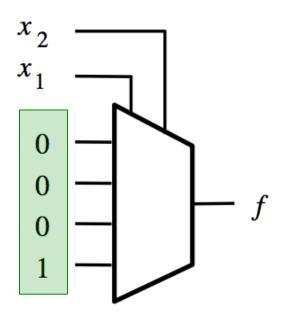

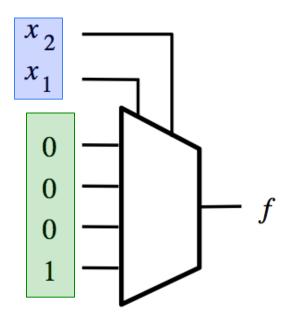

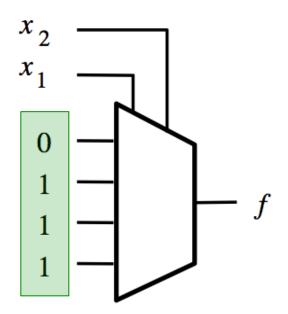

# **Building an AND Gate with 4-to-1 Mux**

| $x_1$ | $x_2$ | $x_1 \cdot x_2$ |

|-------|-------|-----------------|

| 0     | 0     | 0               |

| 0     | 1     | 0               |

| 1     | 0     | 0               |

| 1     | 1     | 1               |

## **Building an AND Gate with 4-to-1 Mux**

| $x_1$            | $x_2$       | $x_1 \cdot x_2$ | x |

|------------------|-------------|-----------------|---|

| 0<br>0<br>1<br>1 | 0<br>1<br>0 | 0<br>0<br>0     |   |

These two are the same.

| $x_1$ | $x_2$         | $x_1 \cdot x_2$                        |

|-------|---------------|----------------------------------------|

| 0     | 0             | 0                                      |

| 0 $1$ | $\frac{1}{0}$ | $\begin{bmatrix} 0 \\ 0 \end{bmatrix}$ |

| 1     | 1             | 1                                      |

These two are the same.

And so are these two.

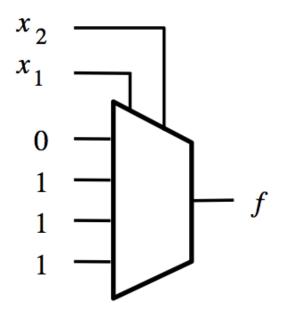

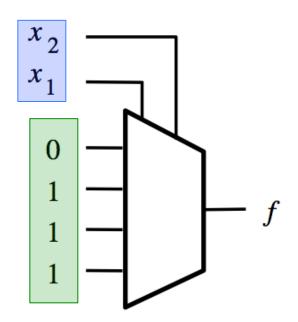

| $x_1$ | $x_2$ | $x_1 + x_2$ |

|-------|-------|-------------|

| 0     | 0     | 0           |

| 0     | 1     | 1           |

| 1     | 0     | 1           |

| 1     | 1     | 1           |

| $x_1$ | $x_2$ | $x_1 + x_2$ |

|-------|-------|-------------|

| 0     | 0     | 0           |

| 0     | 1     | 1           |

| 1     | 0     | 1           |

| 1     | 1     | 1           |

These two are the same.

| $x_1$ | $x_2$ | $x_1$ | $+ x_2$ | _ |

|-------|-------|-------|---------|---|

| 0     | 0     |       | 0       |   |

| 0     | 1     |       | 1       |   |

| 1     | 0     |       | 1       |   |

| 1     | 1     |       | 1       |   |

These two are the same.

And so are these two.

| X | $\overline{x}$ |

|---|----------------|

| 0 | 1              |

| 1 | 0              |

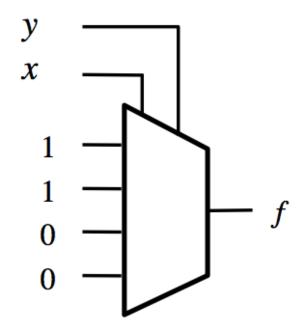

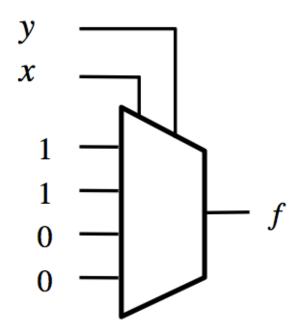

| $\boldsymbol{\mathcal{X}}$ | y | f |

|----------------------------|---|---|

| 0                          | 0 | 1 |

| 0                          | 1 | 1 |

| 1                          | 0 | 0 |

| 1                          | 1 | 0 |

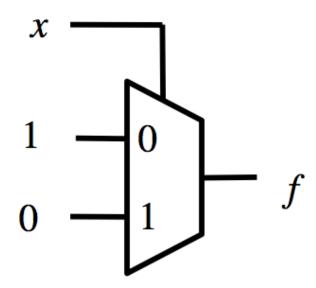

Introduce a dummy variable y.

| $\boldsymbol{\mathcal{X}}$ | y | f |

|----------------------------|---|---|

| 0                          | 0 | 1 |

| 0                          | 1 | 1 |

| 1                          | 0 | 0 |

| 1                          | 1 | 0 |

| $\mathcal{X}$ | y | f |

|---------------|---|---|

| 0             | 0 | 1 |

| 0             | 1 | 1 |

| 1             | 0 | 0 |

| 1             | 1 | 0 |

Now set y to either 0 or 1 (both will work). Why?

Two alternative solutions.

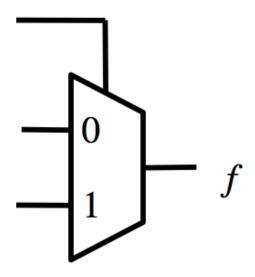

#### **Implications**

### Any Boolean function can be implemented using only 4-to-1 multiplexers!

| $x_1$ | $x_2$       | $x_1 \cdot x_2$ |

|-------|-------------|-----------------|

| 0 0   | 0<br>1<br>0 | 0<br>0<br>0     |

| 1     | 1           | 1               |

| $x_1$ | $x_2$ | $x_1 \cdot x_2$ |

|-------|-------|-----------------|

| 0     | 0     | 0               |

| 0     | 1     | 0               |

| 1     | 0     | 0               |

| 1     | 1     | 1               |

|   | $x_1$  | $x_2$  | $x_1 \cdot x_2$                              |

|---|--------|--------|----------------------------------------------|

|   | 0      | 0<br>1 | $\begin{bmatrix} 0 \\ 0 \end{bmatrix}$       |

| - | 1<br>1 | 0<br>1 | $\begin{bmatrix} 0 \\ 1 \end{bmatrix}$ $X_2$ |

| $x_1$       | $x_2$                                     | $x_1 + x_2$                                                           |

|-------------|-------------------------------------------|-----------------------------------------------------------------------|

| 0           | 0                                         | 0                                                                     |

| 0           | 1                                         | 1                                                                     |

| 1           | 0                                         | 1                                                                     |

| 1           | 1                                         | 1                                                                     |

| 0<br>1<br>1 | $\begin{matrix} 1 \\ 0 \\ 1 \end{matrix}$ | $egin{array}{cccc} & 1 & & \ & 1 & & \ & & 1 & & \ & & & \end{array}$ |

| $x_1$         | $x_2$         | $x_1 + x_2$ |

|---------------|---------------|-------------|

| 0             | 0             | 0           |

| $\frac{0}{1}$ | $\frac{1}{0}$ | 1           |

| 1             | 1             | 1           |

| $x_1$  | $x_2$ | $x_1 + x_2$                                  |

|--------|-------|----------------------------------------------|

| 0      | 0     | $\begin{bmatrix} 0 \\ 1 \end{bmatrix}$ $X_2$ |

| 1<br>1 | 0     | 1 1                                          |

| $\mathcal{X}$ | $\overline{x}$ |

|---------------|----------------|

| 0             | 1              |

| 1             | 0              |

| $\mathcal{X}$ | $\overline{x}$ |

|---------------|----------------|

| 0             | 1              |

| 1             | 0              |

#### **Implications**

### Any Boolean function can be implemented using only 2-to-1 multiplexers!

# Synthesis of Logic Circuits Using Multiplexers

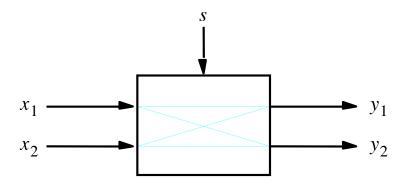

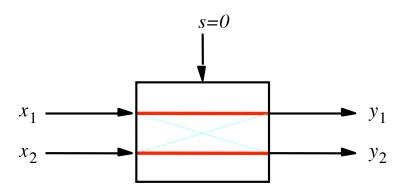

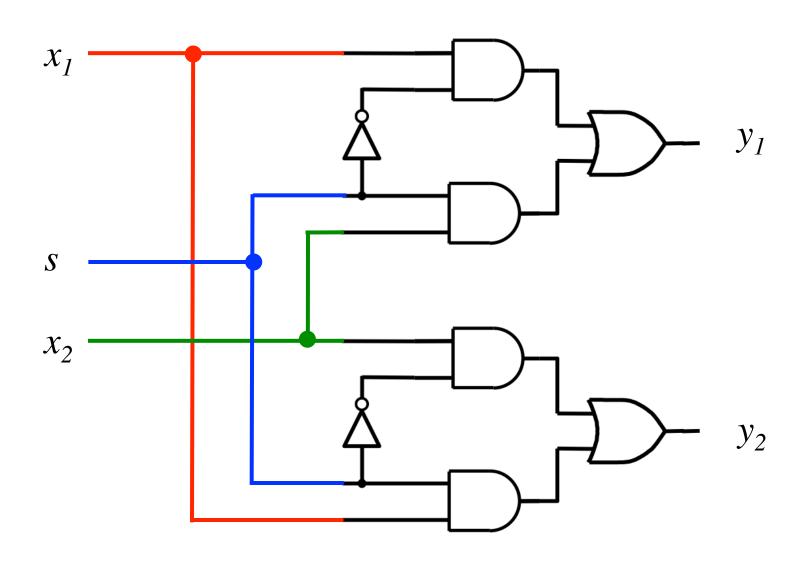

#### 2 x 2 Crossbar switch

#### 2 x 2 Crossbar switch

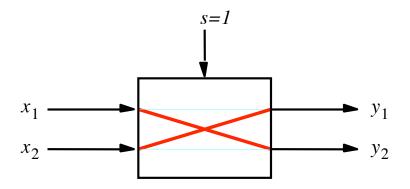

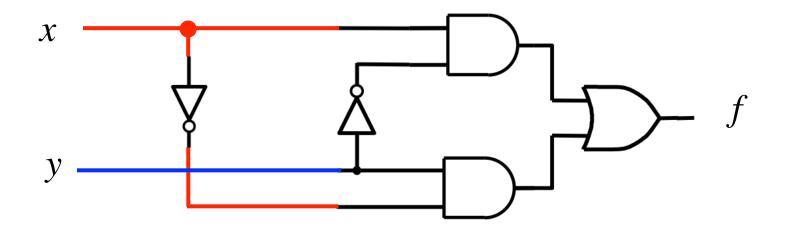

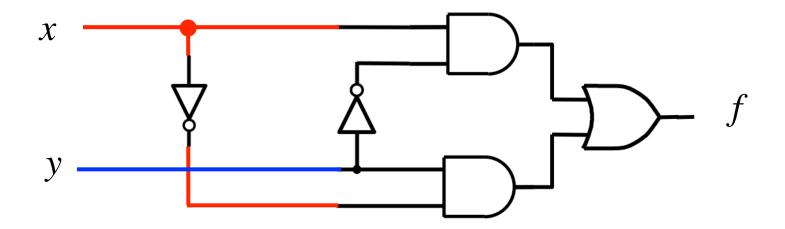

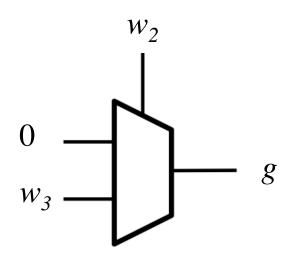

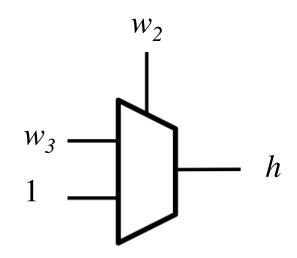

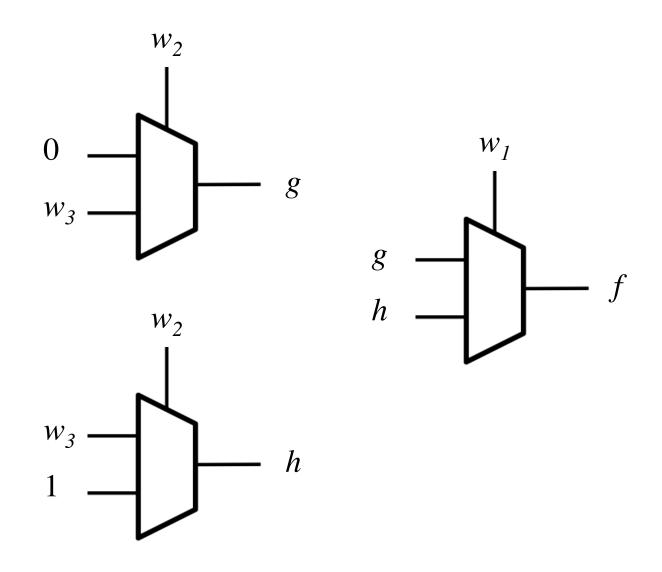

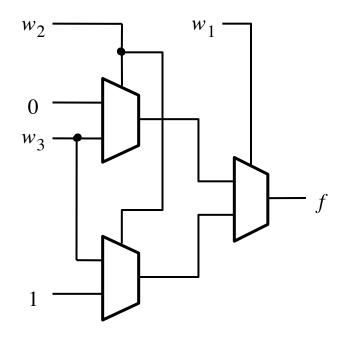

### Implementation of a 2 x 2 crossbar switch with multiplexers

## Implementation of a 2 x 2 crossbar switch with multiplexers

### Implementation of a 2 x 2 crossbar switch with multiplexers

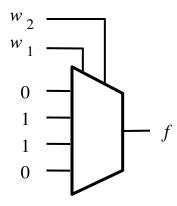

### Implementation of a logic function with a 4x1 multiplexer

| $w_{1}$ | $w_2$ | f |

|---------|-------|---|

| 0       | 0     | 0 |

| 0       | 1     | 1 |

| 1       | 0     | 1 |

| 1       | 1     | 0 |

|         |       |   |

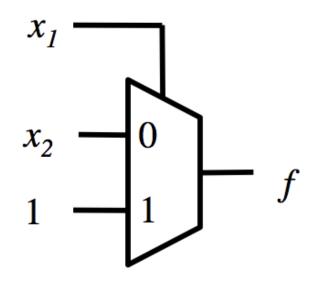

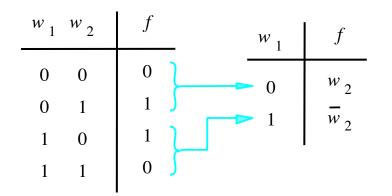

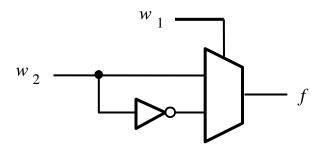

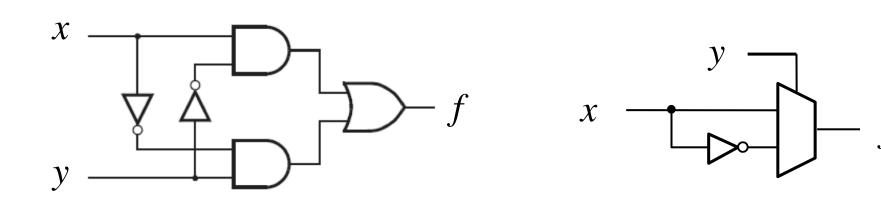

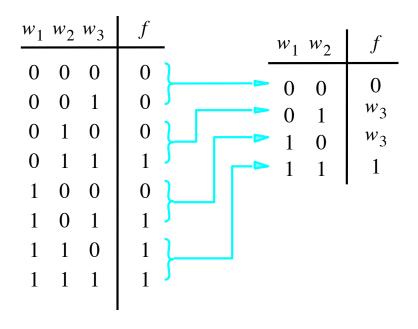

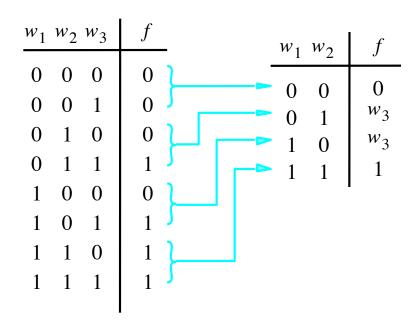

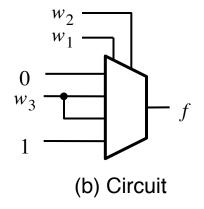

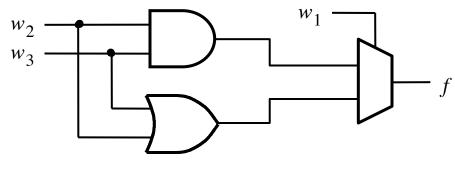

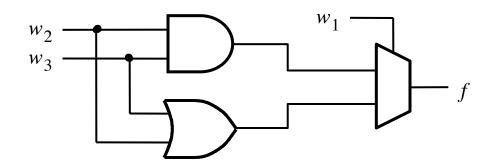

### Implementation of the same logic function with a 2x1 multiplexer

(b) Modified truth table

(c) Circuit

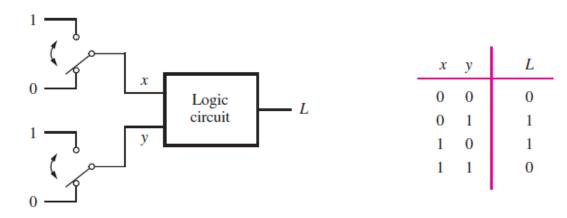

### The XOR Logic Gate

(b) Truth table

### The XOR Logic Gate

| x | у | L |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

|   |   | l |

(a) Two switches that control a light

(b) Truth table

(c) Logic network

(d) XOR gate symbol

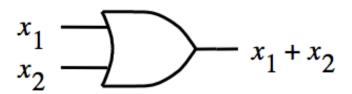

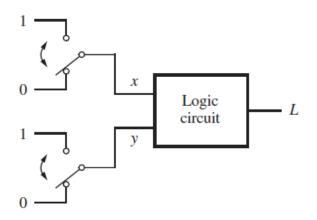

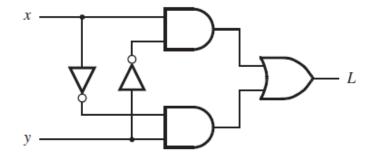

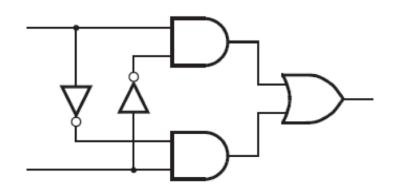

## The XOR Logic Gate Implemented with a multiplexer

## The XOR Logic Gate Implemented with a multiplexer

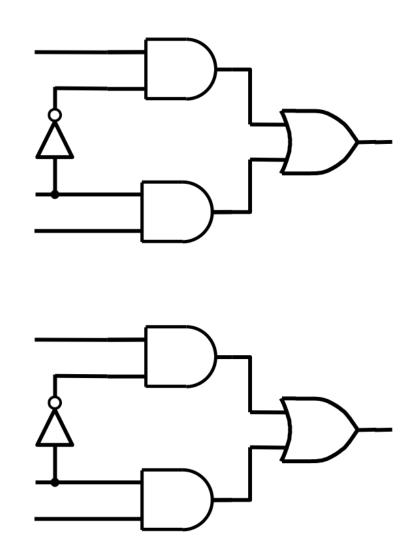

### The XOR Logic Gate Implemented with a multiplexer

These two circuits are equivalent (the wires of the bottom AND gate are flipped)

# In other words, all four of these are equivalent!

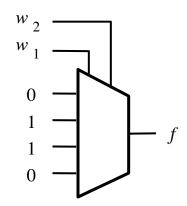

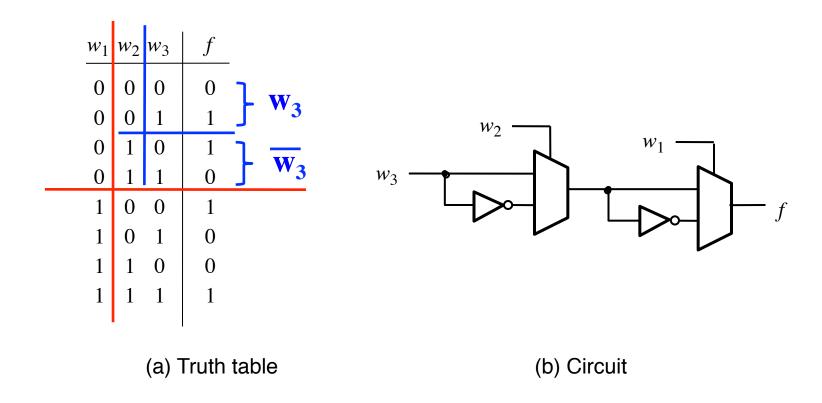

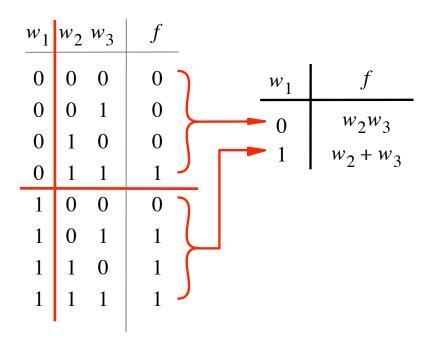

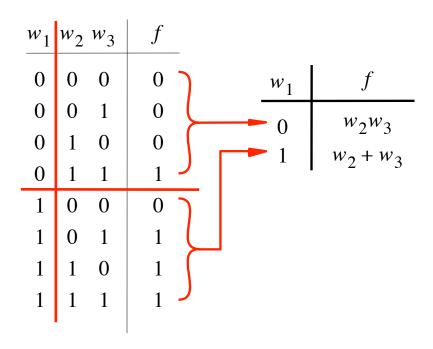

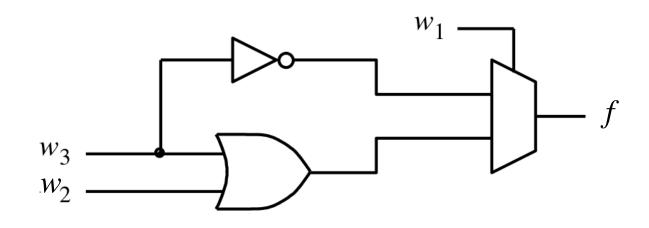

### Implementation of another logic function

| $w_1$ | $w_2$ | $w_3$ | f |

|-------|-------|-------|---|

| 0     | 0     | 0     | 0 |

| 0     | 0     | 1     | 0 |

| 0     | 1     | 0     | 0 |

| 0     | 1     | 1     | 1 |

| 1     | 0     | 0     | 0 |

| 1     | 0     | 1     | 1 |

| 1     | 1     | 0     | 1 |

| 1     | 1     | 1     | 1 |

|       |       |       |   |

#### Implementation of another logic function

### Implementation of another logic function

(a) Modified truth table

[ Figure 4.7 from the textbook ]

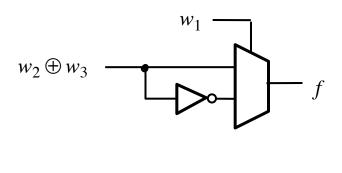

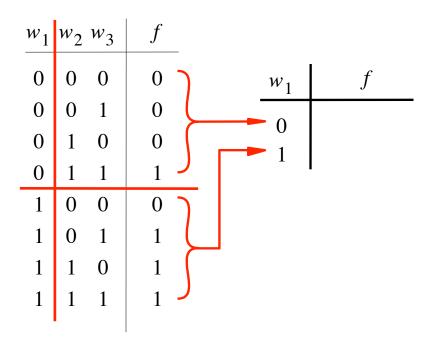

# Another Example (3-input XOR)

| $w_1$ | $w_2$ | $w_3$ | $\int$ |

|-------|-------|-------|--------|

| 0     | 0     | 0     | 0      |

| 0     | 0     | 1     | 1      |

| 0     | 1     | 0     | 1      |

| 0     | 1     | 1     | 0      |

| 1     | 0     | 0     | 1      |

| 1     | 0     | 1     | 0      |

| 1     | 1     | 0     | 0      |

| 1     | 1     | 1     | 1      |

|       |       |       |        |

|              | f                              | $w_3$ | $w_2$ | $w_1$ |

|--------------|--------------------------------|-------|-------|-------|

|              | 0                              | 0     | 0     | 0     |

| <b>4</b> 141 | $1 \downarrow \dots \subseteq$ | 1     | 0     | 0     |

| $\oplus w_3$ | $1 \int_{0}^{w_2 \cdot u}$     | 0     | 1     | 0     |

|              | 0                              | 1     | 1     | 0     |

|              | 1                              | 0     | 0     | 1     |

| $\oplus w_3$ | $0  \sqrt{{w_0}}$              | 1     | 0     | 1     |

| , • w3       | 0                              | 0     | 1     | 1     |

|              | 1                              | 1     | 1     | 1     |

|              |                                |       |       |       |

| $w_1$ | $w_2 w_3$ |                                                    |

|-------|-----------|----------------------------------------------------|

| 0     | 0 0       | 0                                                  |

| 0     | 0 1       | 1 \ w_* \ \ w_*                                    |

| 0     | 1 0       | $1  w_2 \oplus w_3$                                |

| 0     | 1 1       | 0                                                  |

| 1     | 0 0       | 1                                                  |

| 1     | 0 1       | $0 \setminus \frac{1}{w_2 \oplus w_3}$             |

| 1     | 1 0       | $0  \begin{pmatrix} w_2 \cup w_3 \\ \end{pmatrix}$ |

| 1     | 1 1       | 1                                                  |

|       |           |                                                    |

(a) Truth table

(b) Circuit

| $w_1$ | $w_2$ | $w_3$ | f |

|-------|-------|-------|---|

| 0     | 0     | 0     | 0 |

| 0     | 0     | 1     | 1 |

| 0     | 1     | 0     | 1 |

| 0     | 1     | 1     | 0 |

| 1     | 0     | 0     | 1 |

| 1     | 0     | 1     | 0 |

| 1     | 1     | 0     | 0 |

| 1     | 1     | 1     | 1 |

|       |       |       |   |

| $w_1$ | $w_2$ | $w_3$ | f |  |

|-------|-------|-------|---|--|

| 0     | 0     | 0     | 0 |  |

| 0     | 0     | 1     | 1 |  |

| 0     | 1     | 0     | 1 |  |

| 0     | 1     | 1     | 0 |  |

| 1     | 0     | 0     | 1 |  |

| 1     | 0     | 1     | 0 |  |

| 1     | 1     | 0     | 0 |  |

| 1     | 1     | 1     | 1 |  |

|       |       | •     |   |  |

|                  | _      | f | $w_3$ | $w_2$ | $w_1$ |

|------------------|--------|---|-------|-------|-------|

| 141              | _<br>[ | 0 | 0     | 0     | 0     |

| $w_3$            | 5      | 1 | 1     | 0     | 0     |

| $\overline{w}_3$ | Ì      | 1 | 0     | 1     | 0     |

| w 3              | 5      | 0 | 1     | 1     | 0     |

| $\overline{w}_3$ | ļ      | 1 | 0     | 0     | 1     |

| w 3              | J      | 0 | 1     | 0     | 1     |

| 142 -            | 1      | 0 | 0     | 1     | 1     |

| $w_3$            | J      | 1 | 1     | 1     | 1     |

|                  |        |   | ١     |       |       |

| $w_1$ | $w_2$ | $w_3$ | f                                                                   |

|-------|-------|-------|---------------------------------------------------------------------|

| 0     | 0     | 0     | 0 } ,,,                                                             |

| 0     | 0     | 1     | $\left\{\begin{array}{c}0\\1\end{array}\right\} w_3$                |

| 0     | 1     | 0     | $\left\{\begin{array}{c}1\\0\end{array}\right\}\overline{w}_3$      |

| 0     | 1     | 1     | $0$ $\sqrt{3}$                                                      |

| 1     | 0     | 0     | $\left\{\begin{array}{c}1\\0\end{array}\right\}$                    |

| 1     | 0     | 1     | $0$ $\sqrt{3}$                                                      |

| 1     | 1     | 0     | 0                                                                   |

| 1     | 1     | 1     | $\begin{cases} 0 \\ 1 \end{cases} $ $\begin{cases} w_3 \end{cases}$ |

|       |       |       |                                                                     |

(a) Truth table

(b) Circuit

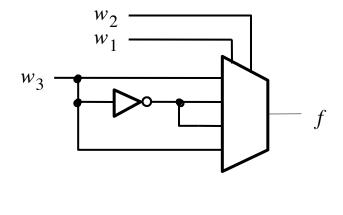

# Multiplexor Synthesis Using Shannon's Expansion

| $w_1$ | $w_2$ | $w_3$ | f |

|-------|-------|-------|---|

| 0     | 0     | 0     | 0 |

| 0     | 0     | 1     | 0 |

| 0     | 1     | 0     | 0 |

| 0     | 1     | 1     | 1 |

| 1     | 0     | 0     | 0 |

| 1     | 0     | 1     | 1 |

| 1     | 1     | 0     | 1 |

| 1     | 1     | 1     | 1 |

|       |       |       |   |

(b) Truth table

(b) Circuit

[ Figure 4.10a from the textbook ]

$$f = \overline{w}_1 w_2 w_3 + w_1 \overline{w}_2 w_3 + w_1 w_2 \overline{w}_3 + w_1 w_2 w_3$$

$$f = \overline{w}_1(w_2w_3) + w_1(\overline{w}_2w_3 + w_2\overline{w}_3 + w_2w_3)$$

=  $\overline{w}_1(w_2w_3) + w_1(w_2 + w_3)$

### **Shannon's Expansion Theorem**

Any Boolean function  $f(w_1, \ldots, w_n)$  can be rewritten in the form:

$$f(w_1, w_2, \dots, w_n) = \overline{w}_1 \cdot f(0, w_2, \dots, w_n) + w_1 \cdot f(1, w_2, \dots, w_n)$$

### **Shannon's Expansion Theorem**

Any Boolean function  $f(w_1, \ldots, w_n)$  can be rewritten in the form:

$$f(w_1, w_2, \dots, w_n) = \overline{w}_1 \cdot f(0, w_2, \dots, w_n) + w_1 \cdot f(1, w_2, \dots, w_n)$$

$$f = \overline{w}_1 f_{\overline{w}_1} + w_1 f_{w_1}$$

#### Shannon's Expansion Theorem

Any Boolean function  $f(w_1, \ldots, w_n)$  can be rewritten in the form:

$$f(w_1, w_2, \dots, w_n) = \overline{w}_1 \cdot f(0, w_2, \dots, w_n) + w_1 \cdot f(1, w_2, \dots, w_n)$$

$$f = \overline{w}_1 f_{\overline{w}_1} + w_1 f_{w_1}$$

cofactor cofactor

# Shannon's Expansion Theorem (Example)

$$f(w_1, w_2, w_3) = w_1w_2 + w_1w_3 + w_2w_3$$

# Shannon's Expansion Theorem (Example)

$$f(w_1, w_2, w_3) = w_1w_2 + w_1w_3 + w_2w_3$$

$$f(w_1, w_2, w_3) = w_1 w_2 + w_1 w_3 + w_2 w_3 (\overline{w_1} + w_1)$$

# Shannon's Expansion Theorem (Example)

$$f(w_1, w_2, w_3) = w_1w_2 + w_1w_3 + w_2w_3$$

$$f(w_1, w_2, w_3) = w_1 w_2 + w_1 w_3 + w_2 w_3 (\overline{w_1} + w_1)$$

$$f = \overline{w}_1(0 \cdot w_2 + 0 \cdot w_3 + w_2w_3) + w_1(1 \cdot w_2 + 1 \cdot w_3 + w_2w_3)$$

=  $\overline{w}_1(w_2w_3) + w_1(w_2 + w_3)$

# Shannon's Expansion Theorem (In terms of more than one variable)

$$f(w_1, \dots, w_n) = \overline{w}_1 \overline{w}_2 \cdot f(0, 0, w_3, \dots, w_n) + \overline{w}_1 w_2 \cdot f(0, 1, w_3, \dots, w_n) + w_1 \overline{w}_2 \cdot f(1, 0, w_3, \dots, w_n) + w_1 w_2 \cdot f(1, 1, w_3, \dots, w_n)$$

This form is suitable for implementation with a 4x1 multiplexer.

### **Another Example**

$$f = \overline{w}_1 \overline{w}_3 + w_1 w_2 + w_1 w_3$$

$$f = \overline{w}_1 \overline{w}_3 + w_1 w_2 + w_1 w_3$$

$$f = \overline{w}_1 f_{\overline{w}_1} + w_1 f_{w_1}$$

$$= \overline{w}_1 (\overline{w}_3) + w_1 (w_2 + w_3)$$

$$f = \overline{w}_1 f_{\overline{w}_1} + w_1 f_{w_1}$$

$$= \overline{w}_1 (\overline{w}_3) + w_1 (w_2 + w_3)$$

## Factor and implement the following function with a 4x1 multiplexer

$$f = \overline{w}_1 \overline{w}_3 + w_1 w_2 + w_1 w_3$$

## Factor and implement the following function with a 4x1 multiplexer

$$f = \overline{w}_1 \overline{w}_3 + w_1 w_2 + w_1 w_3$$

$$f = \overline{w}_1 \overline{w}_2 f_{\overline{w}_1 \overline{w}_2} + \overline{w}_1 w_2 f_{\overline{w}_1 w_2} + w_1 \overline{w}_2 f_{w_1 \overline{w}_2} + w_1 w_2 f_{w_1 w_2}$$

$$= \overline{w}_1 \overline{w}_2 (\overline{w}_3) + \overline{w}_1 w_2 (\overline{w}_3) + w_1 \overline{w}_2 (w_3) + w_1 w_2 (1)$$

## Factor and implement the following function with a 4x1 multiplexer

$$f = \overline{w}_1 \overline{w}_2 f_{\overline{w}_1 \overline{w}_2} + \overline{w}_1 w_2 f_{\overline{w}_1 w_2} + w_1 \overline{w}_2 f_{w_1 \overline{w}_2} + w_1 w_2 f_{w_1 w_2}$$

$$= \overline{w}_1 \overline{w}_2 (\overline{w}_3) + \overline{w}_1 w_2 (\overline{w}_3) + w_1 \overline{w}_2 (w_3) + w_1 w_2 (1)$$

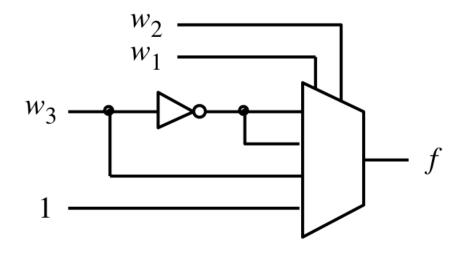

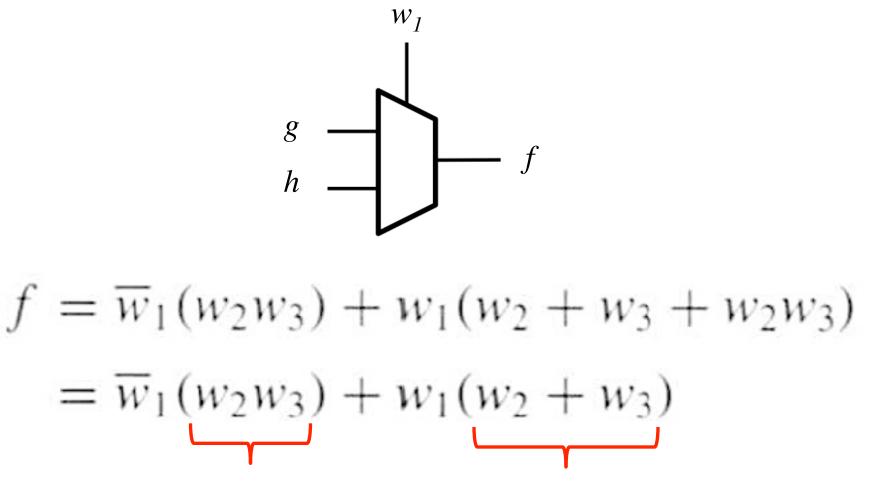

### Yet Another Example

$$f = w_1 w_2 + w_1 w_3 + w_2 w_3$$

$$f = w_1 w_2 + w_1 w_3 + w_2 w_3$$

$$f = \overline{w}_1(w_2w_3) + w_1(w_2 + w_3 + w_2w_3)$$

=  $\overline{w}_1(w_2w_3) + w_1(w_2 + w_3)$

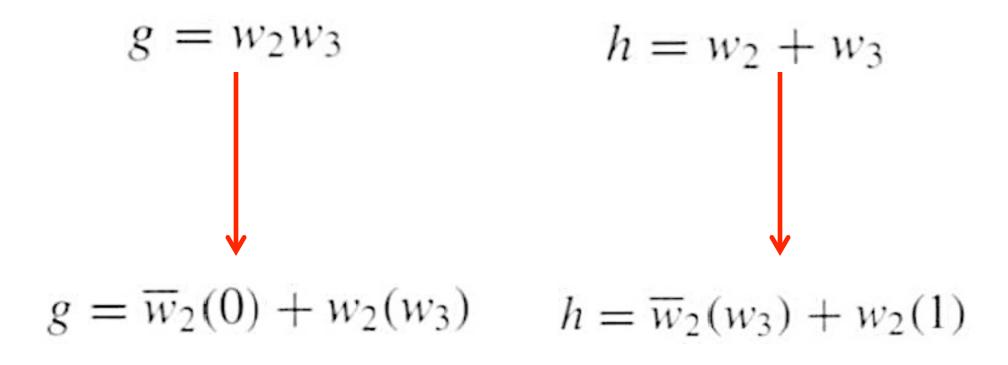

$$f = w_1 w_2 + w_1 w_3 + w_2 w_3$$

$$f = \overline{w}_1(w_2w_3) + w_1(w_2 + w_3 + w_2w_3)$$

=  $\overline{w}_1(w_2w_3) + w_1(w_2 + w_3)$

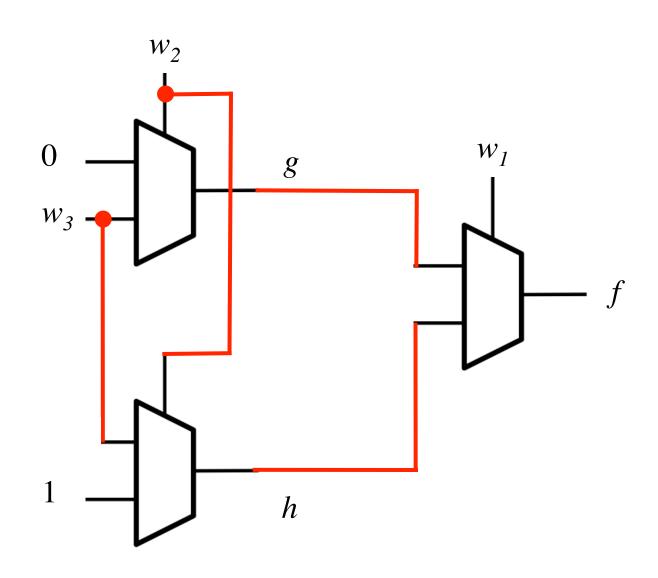

$$g = w_2w_3 \qquad h = w_2 + w_3$$

$g = w_2 w_3$   $h = w_2 + w_3$

$$g = w_2 w_3$$

$$h = w_2 + w_3$$

$$g = \overline{w}_2(0) + w_2(w_3)$$

$h = \overline{w}_2(w_3) + w_2(1)$

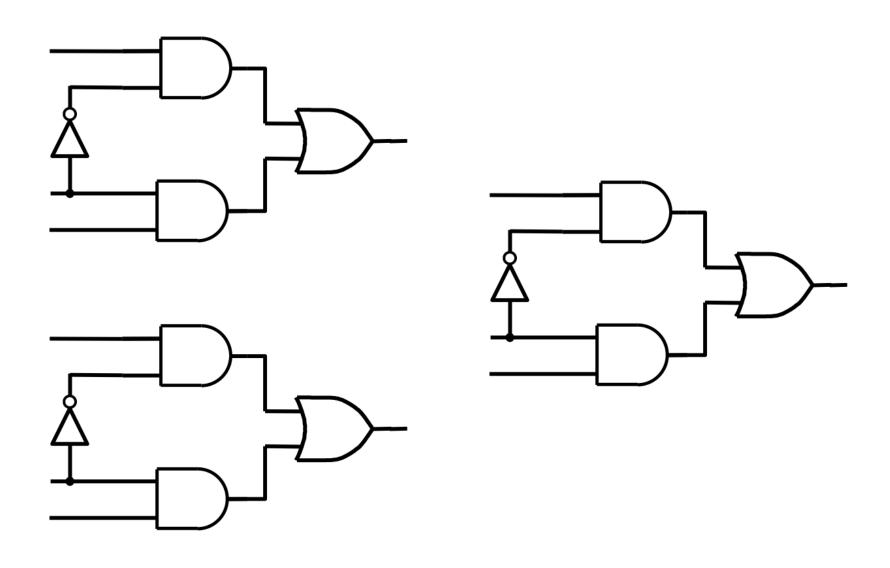

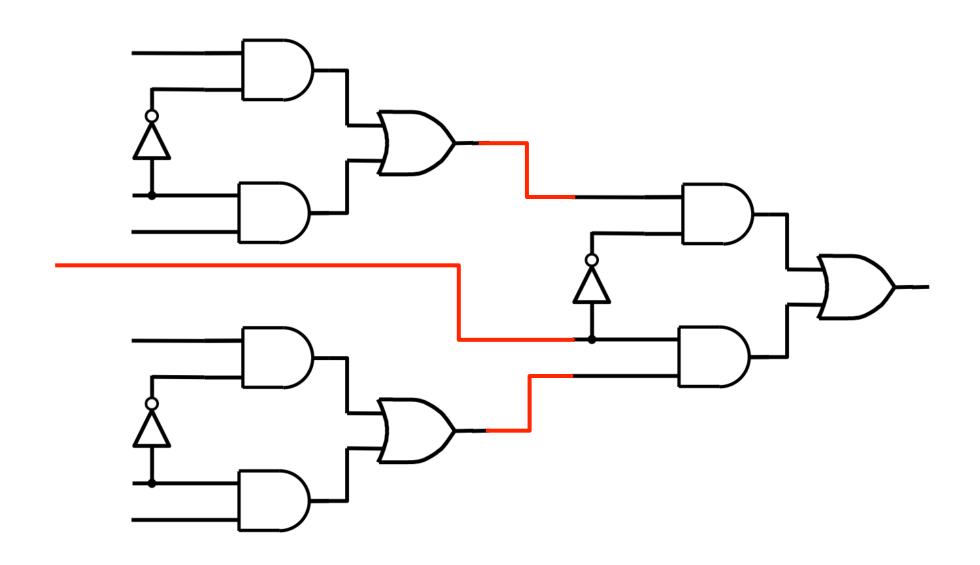

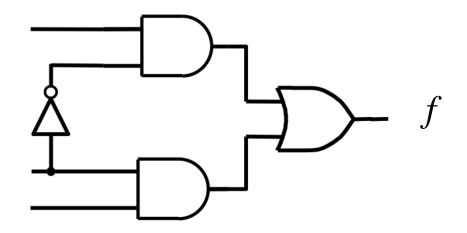

### Finally, we are ready to draw the circuit

### Finally, we are ready to draw the circuit

### Finally, we are ready to draw the circuit

**Questions?**

#### THE END