# **CprE 281: Digital Logic**

**Instructor: Alexander Stoytchev**

http://www.ece.iastate.edu/~alexs/classes/

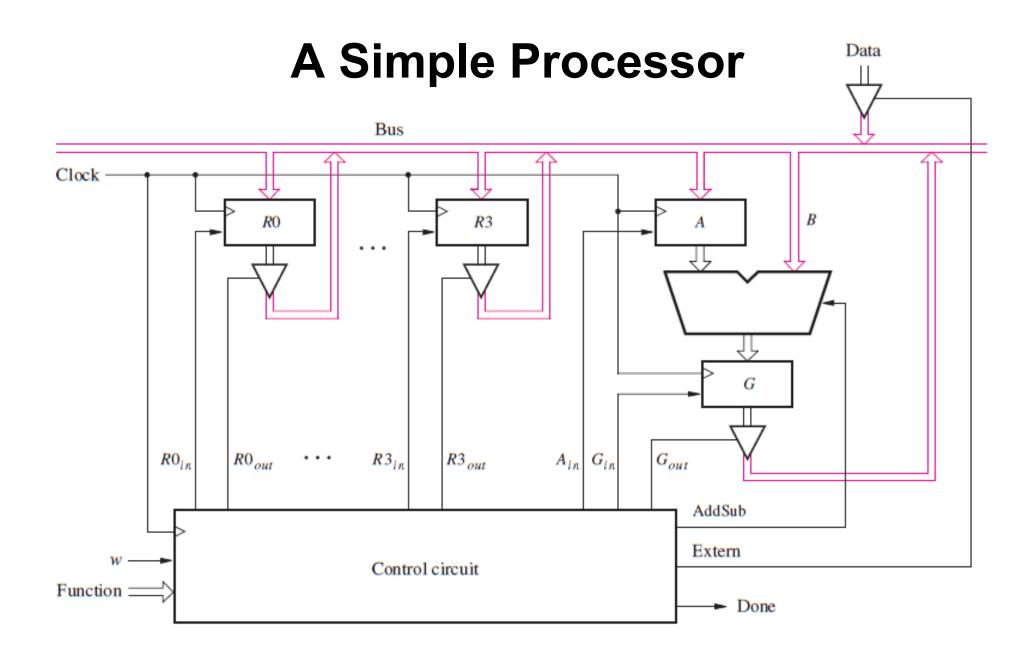

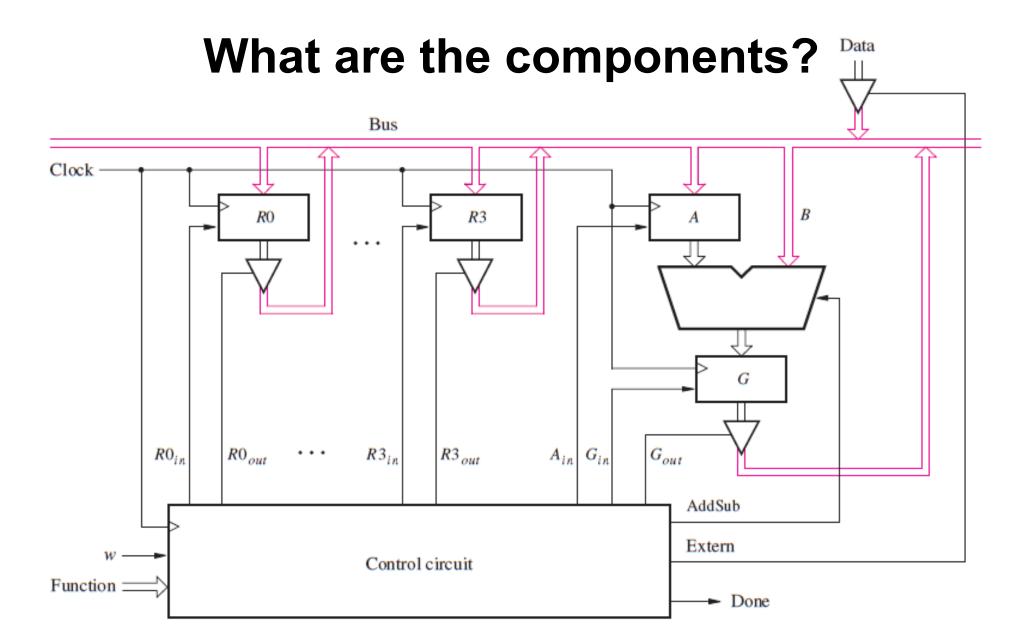

## Simple Processor

#### **Administrative Stuff**

Final Project (7% of your grade)

This is due this week (during your lab)

#### **Administrative Stuff**

- Extra Credit Homework

- Posted on the class web page

- This is due this Friday @ 4pm

#### **Digital System**

#### Datapath circuit

- To store data

- To manipulate data

- To transfer data from one part of the system to another

- Comprise building blocks such as registers, shift registers, counters, multipliers, decoders, encoders, adders, etc.

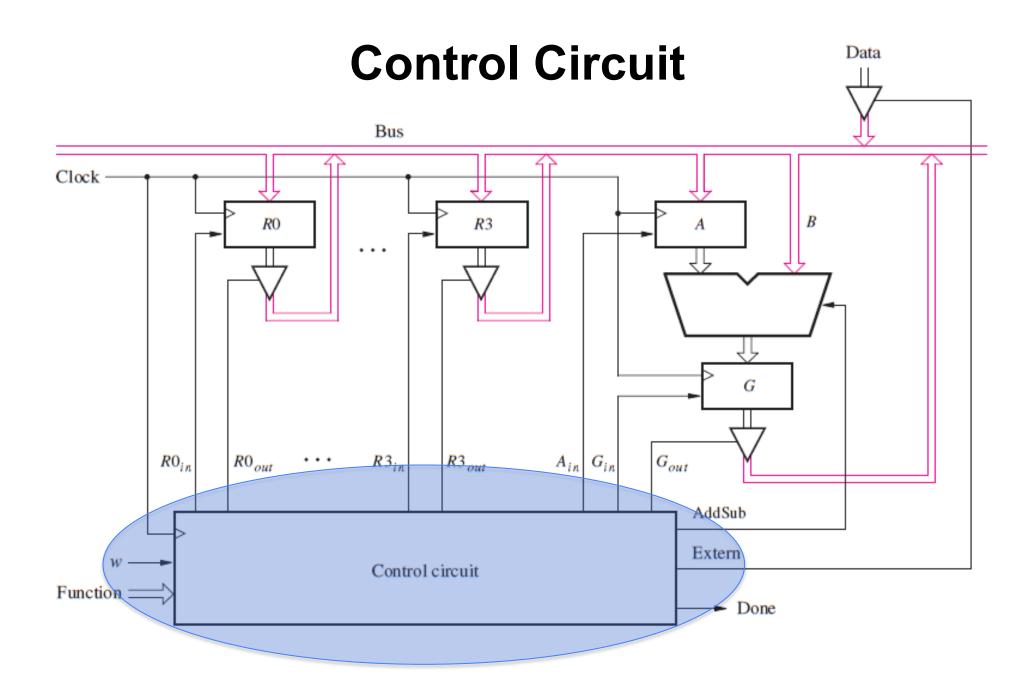

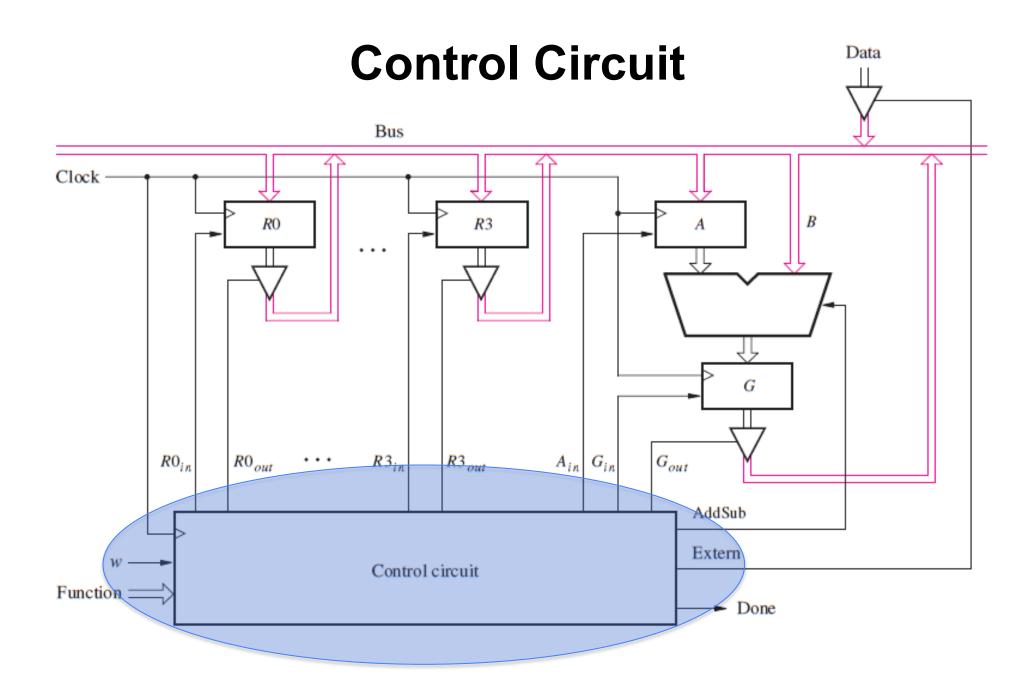

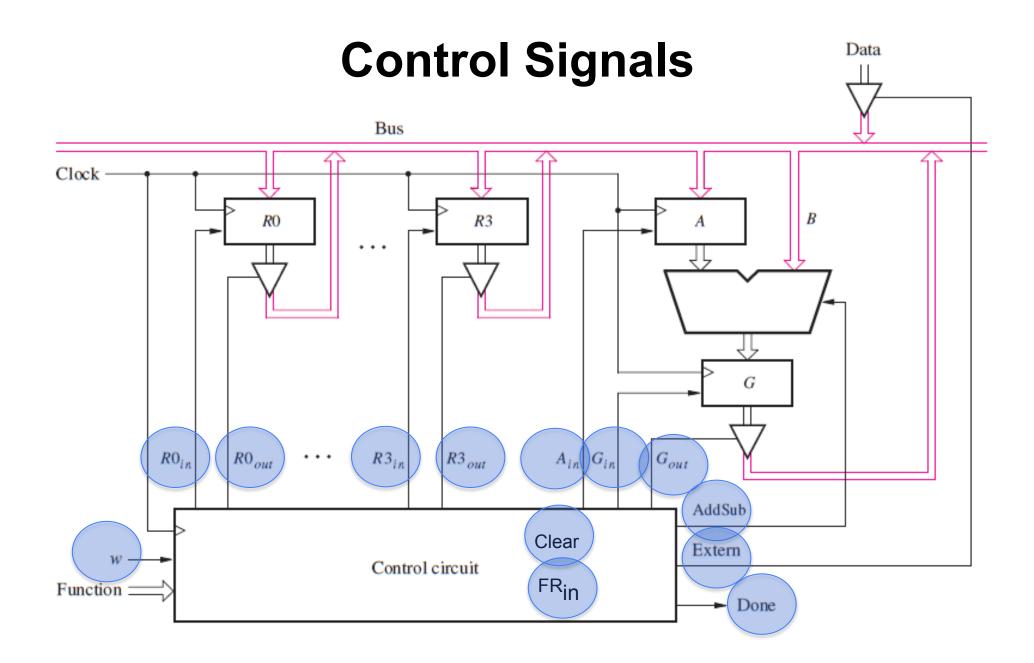

#### Control circuit

- Controls the operation of the datapath circuit

- Designed as a FSM

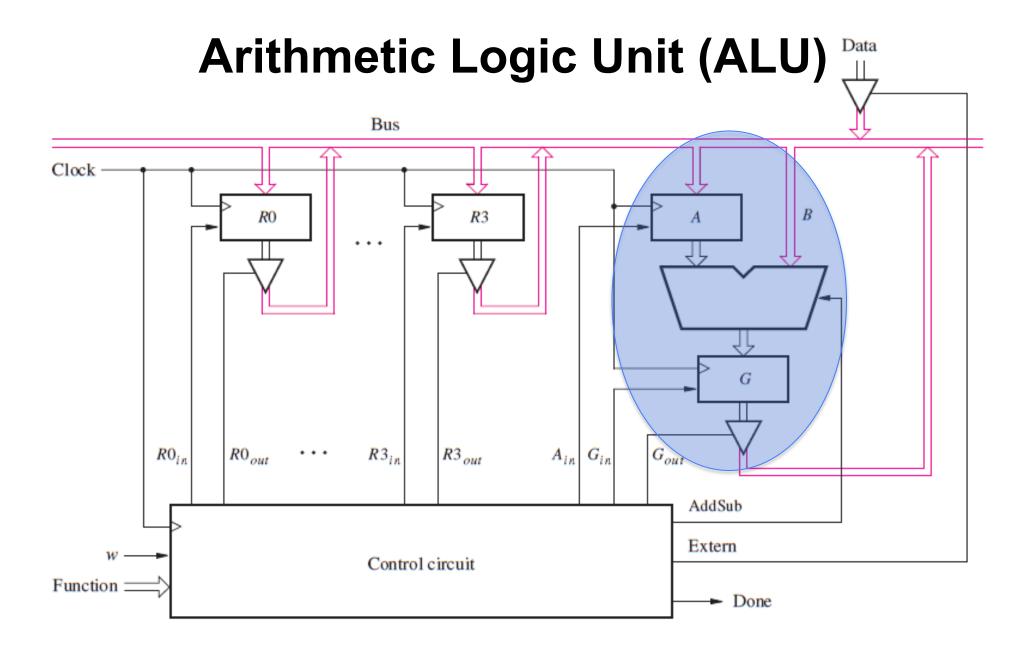

[ Figure 7.9 from the textbook ]

[ Figure 7.9 from the textbook ]

[ Figure 7.9 from the textbook ]

[ Figure 7.9 from the textbook ]

[ Figure 7.9 from the textbook ]

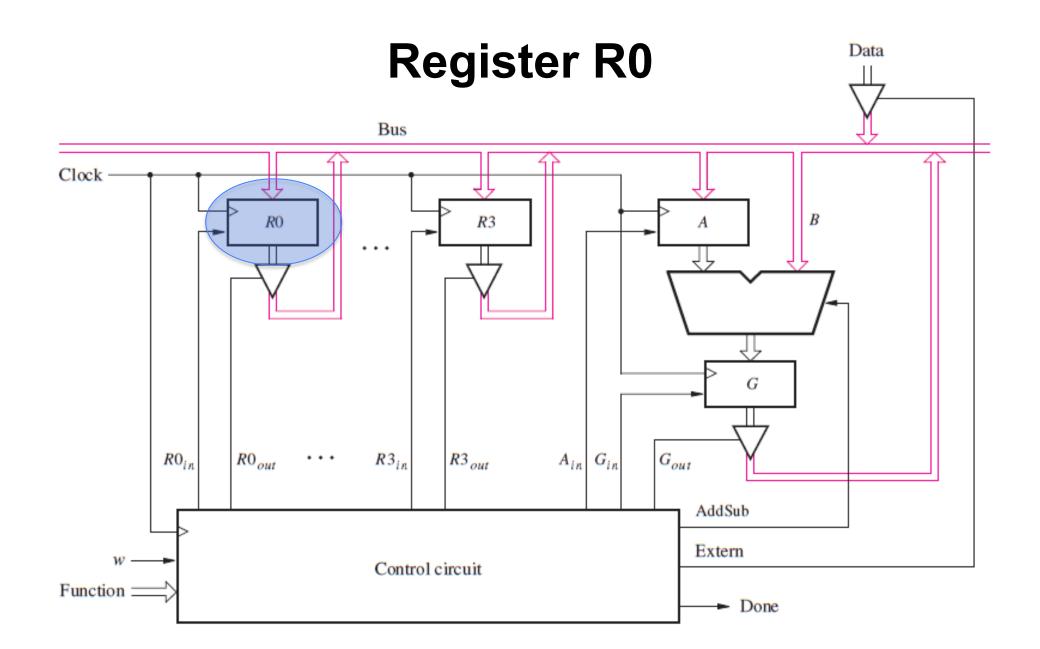

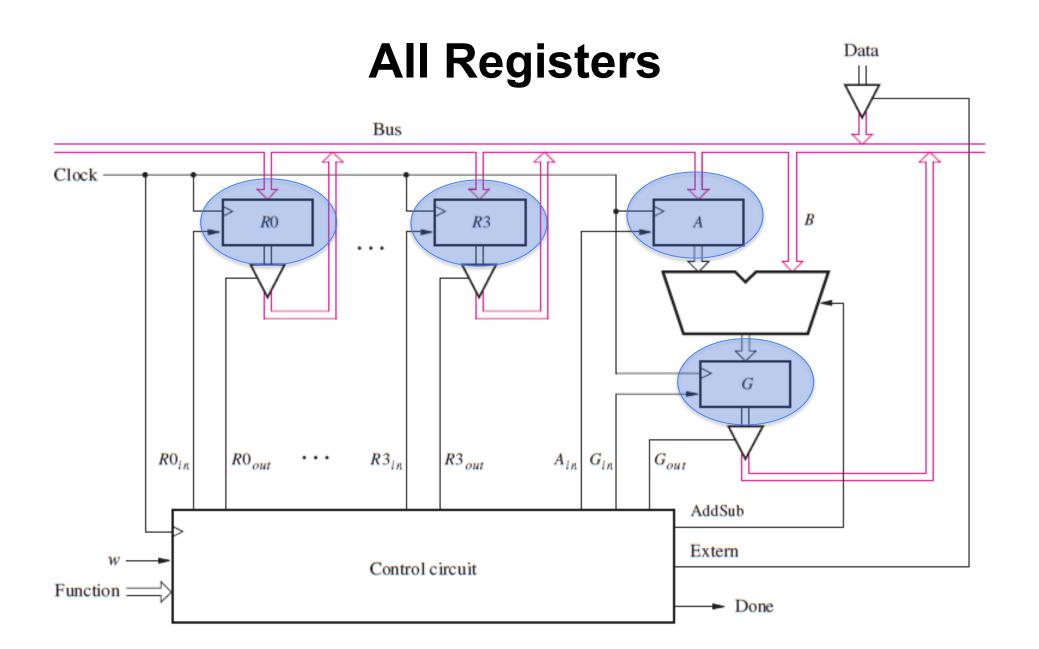

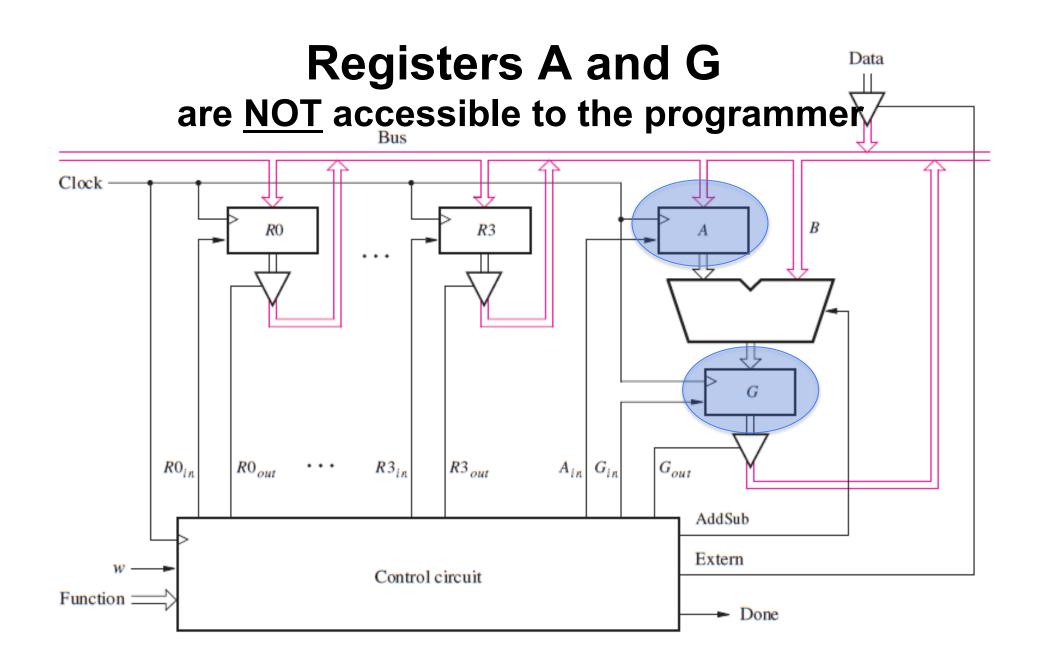

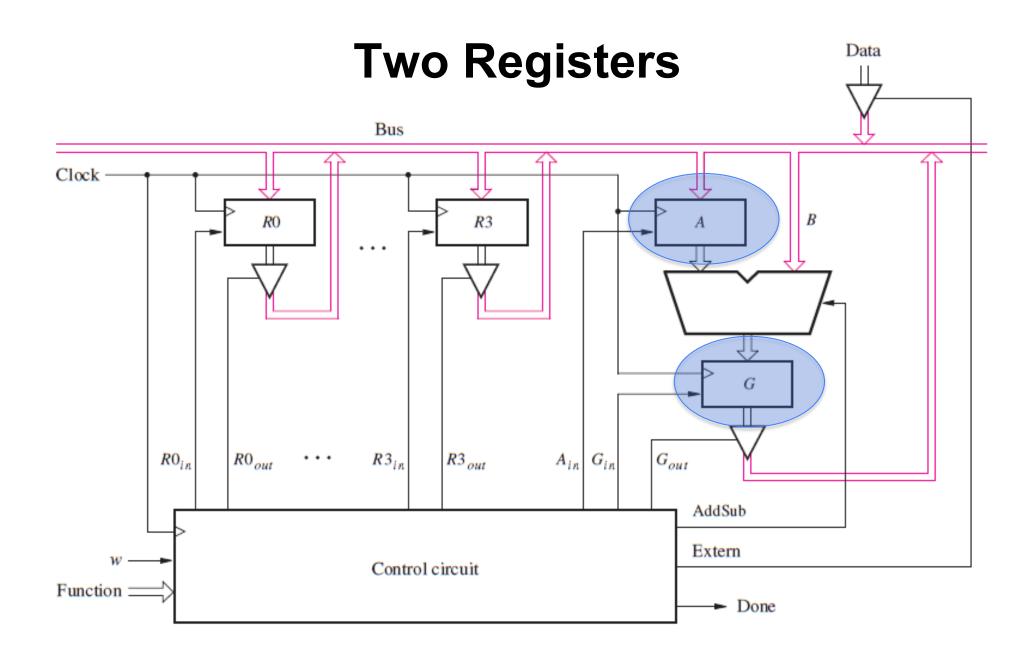

## A Closer Look at the Registers

[ Figure 7.9 from the textbook ]

[ Figure 7.9 from the textbook ]

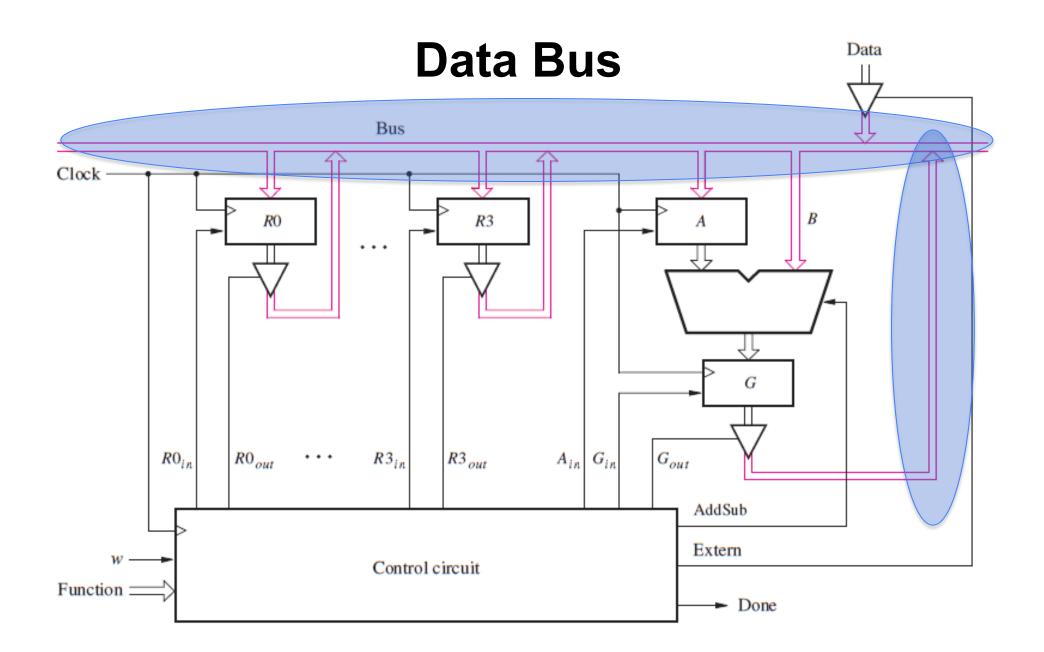

#### Registers R0, R1, R2 and R3 are accessible to the programmer Clock R0R3 $G_{out}$ $R0_{in}$ $R3_{in}$ $R0_{out}$ $R3_{out}$ $G_{in}$ AddSub Extern Control circuit Function: Done

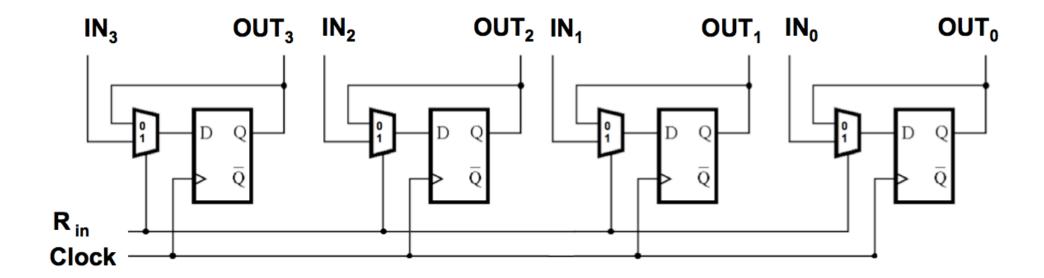

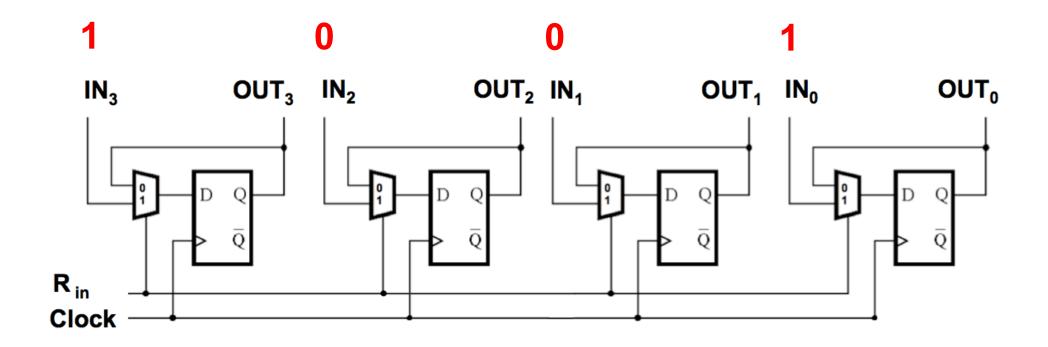

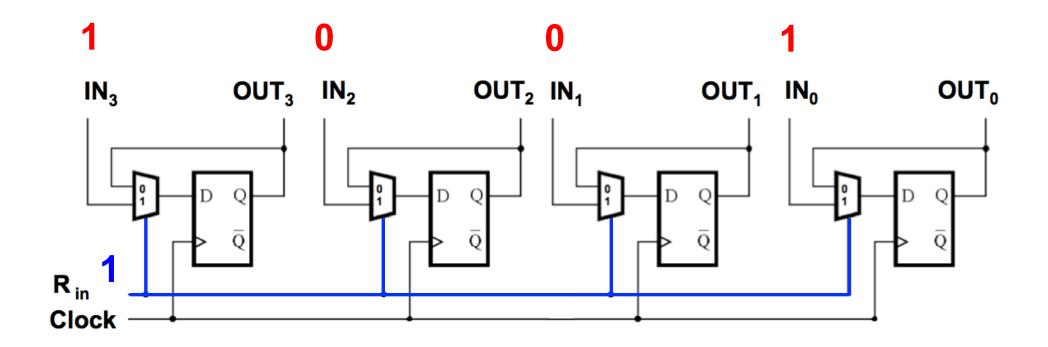

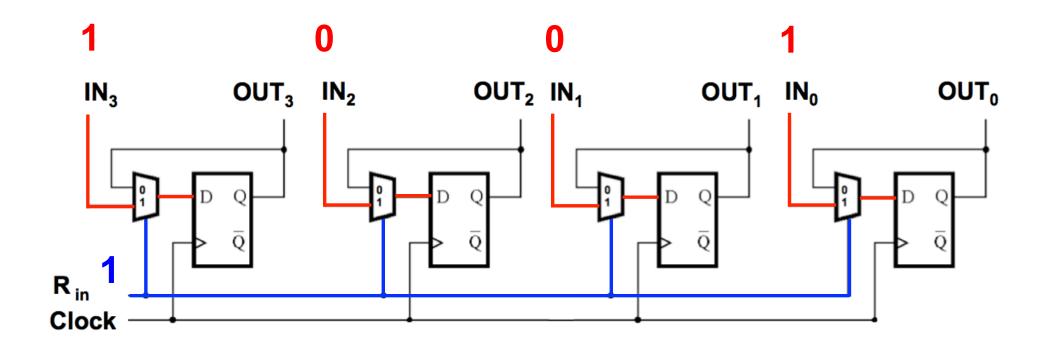

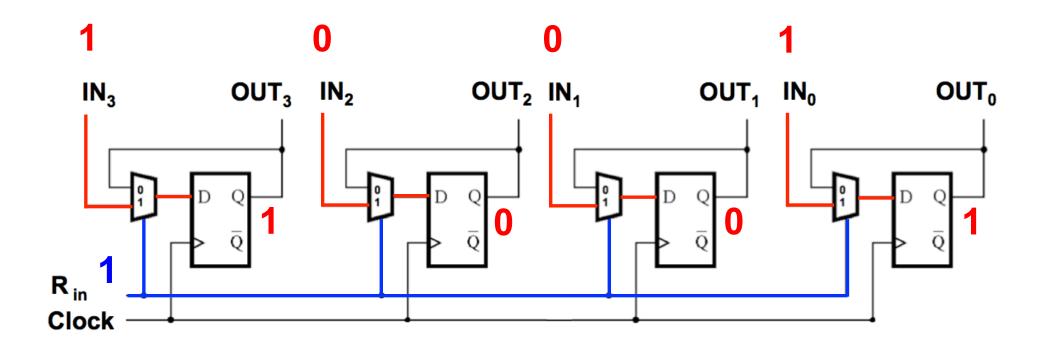

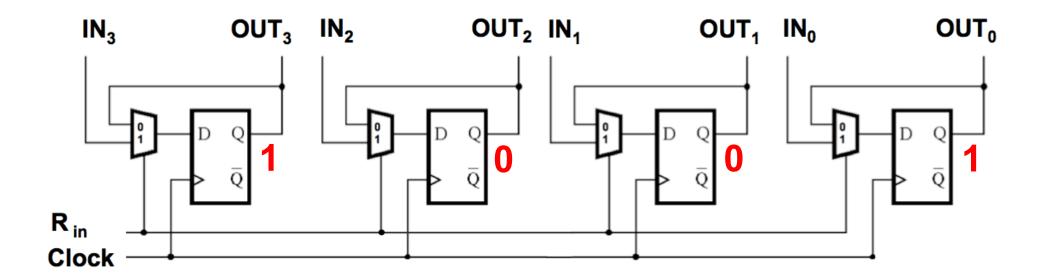

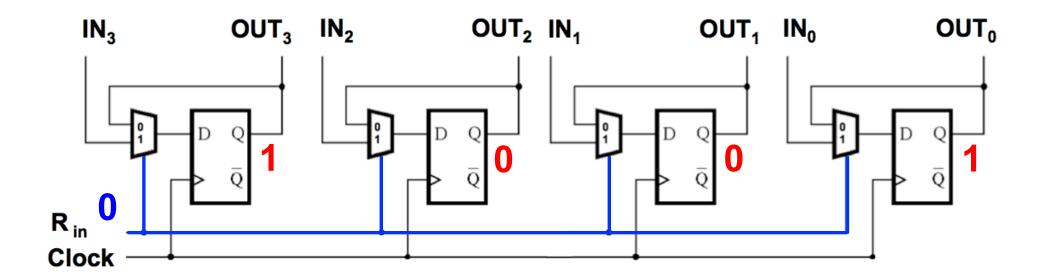

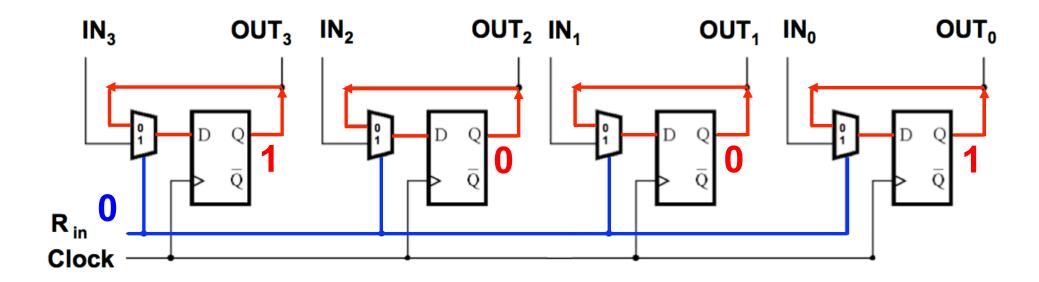

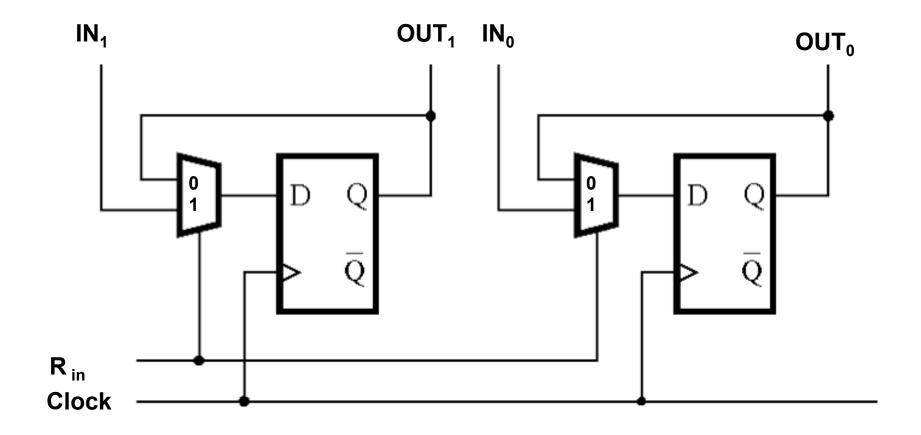

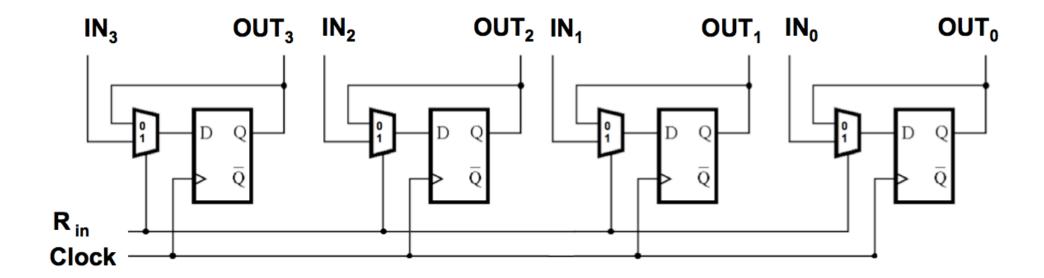

## **4-Bit Register**

## **Keeping Data into the Register**

## **Keeping Data into the Register**

## **Keeping Data into the Register**

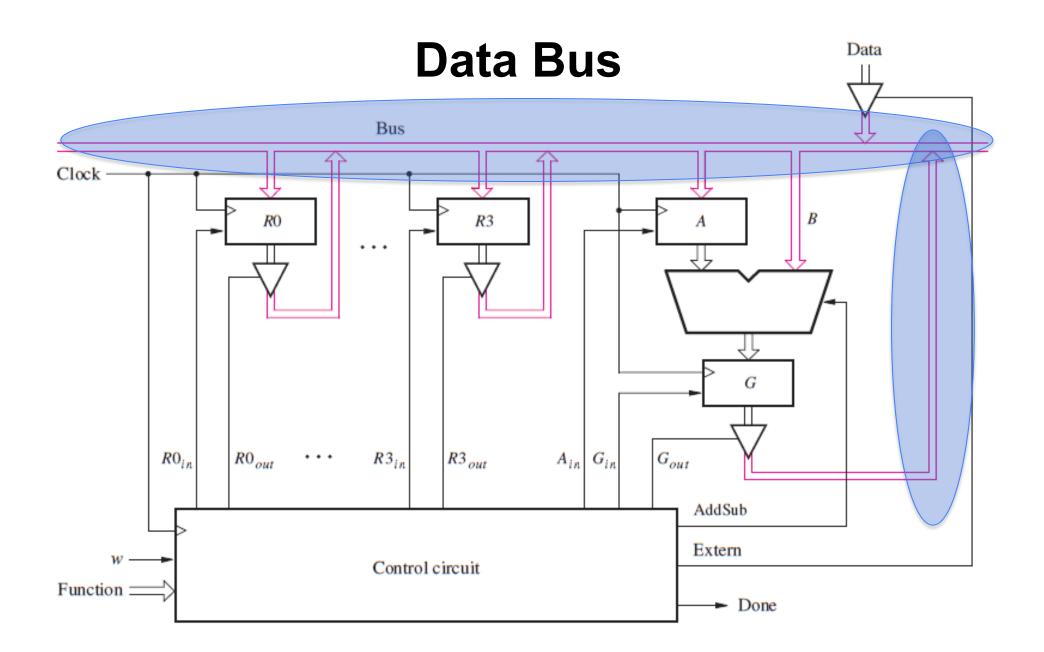

#### A Closer Look at the Data Bus

[ Figure 7.9 from the textbook ]

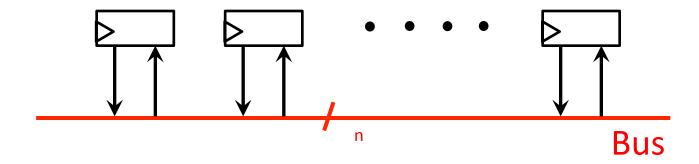

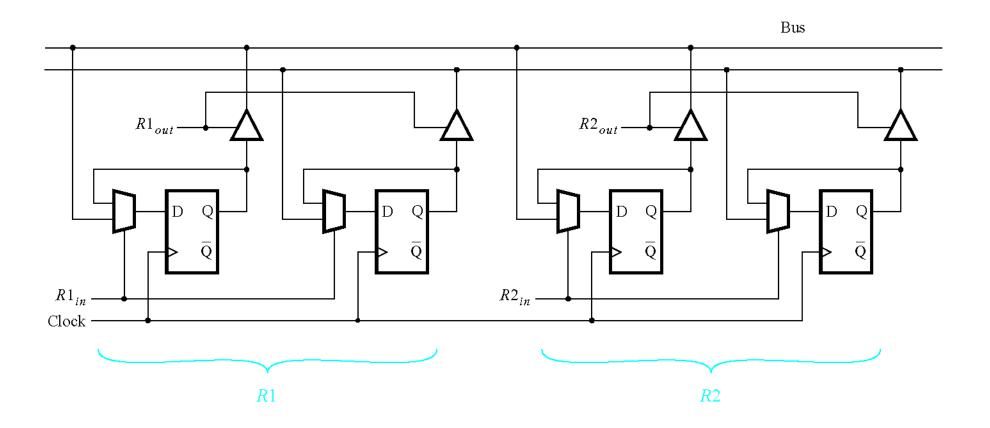

#### **Bus Structure**

- We need a way to transfer data from any register (device) to any other register (device)

- A bus is simply a set of n wires to transfer an n-bit data

What if two registers write to the bus at the same time?

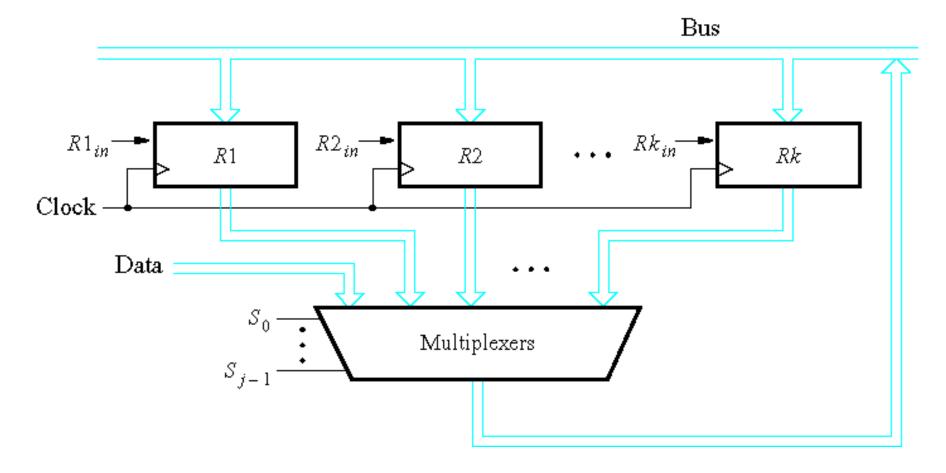

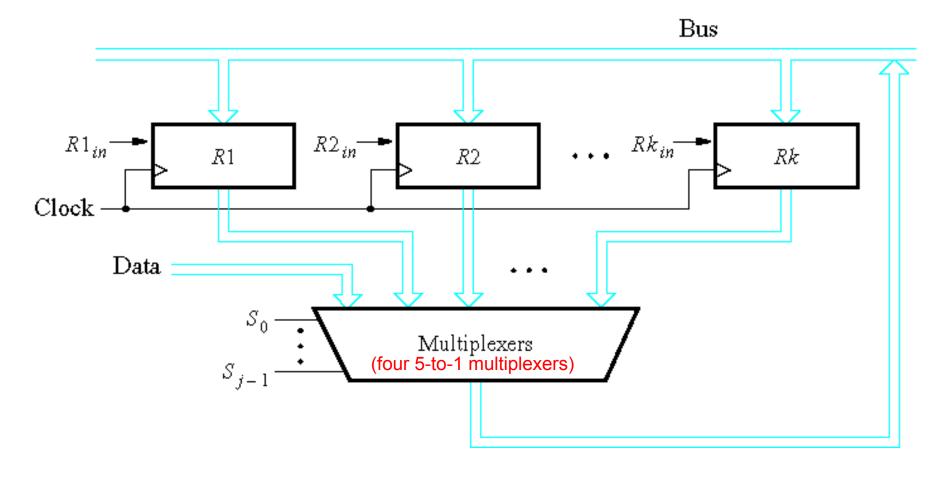

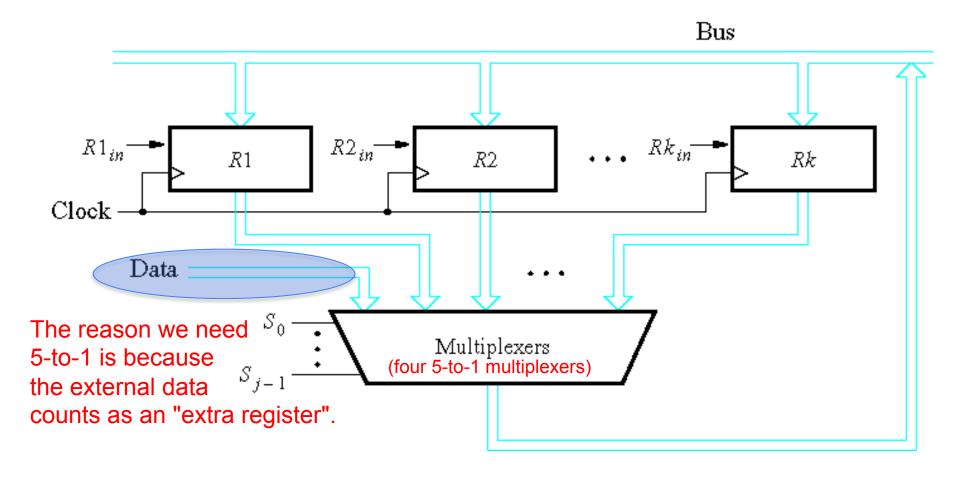

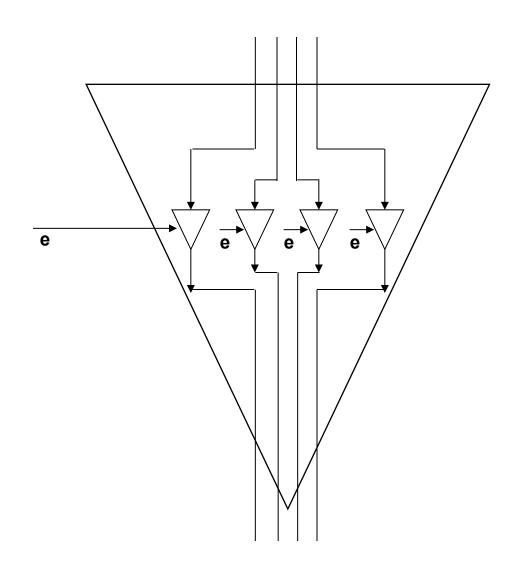

## One way to implement a data bus is to use multiplexers

## One way to implement a data bus is to use multiplexers

This requires one multiplexer per bit.

Assuming there are four 4-bit registers, we need four 5-to-1 multiplexers.

## One way to implement a data bus is to use multiplexers

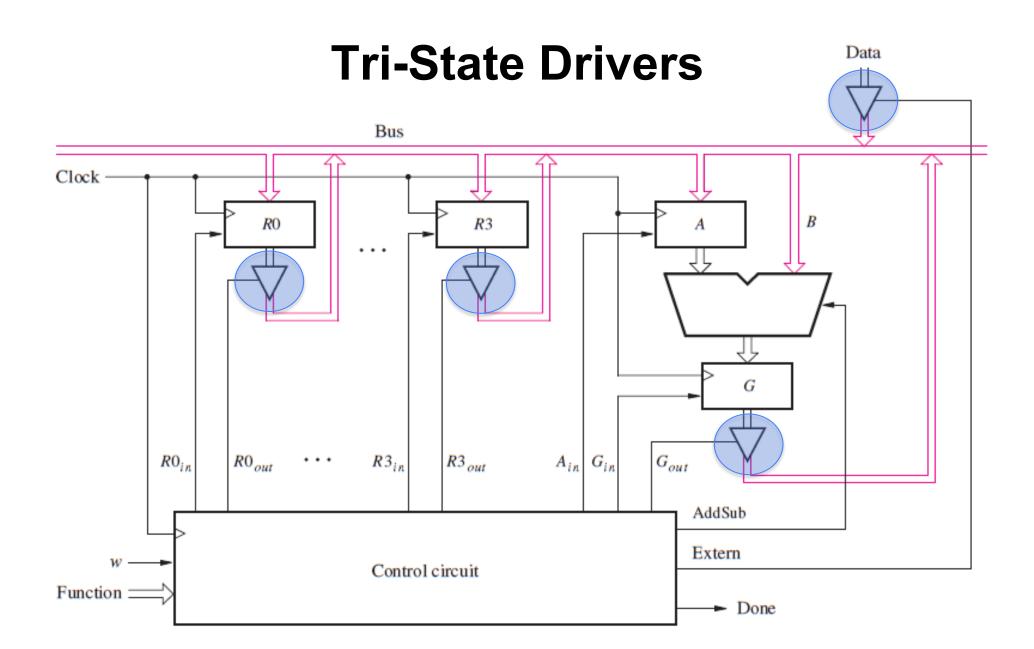

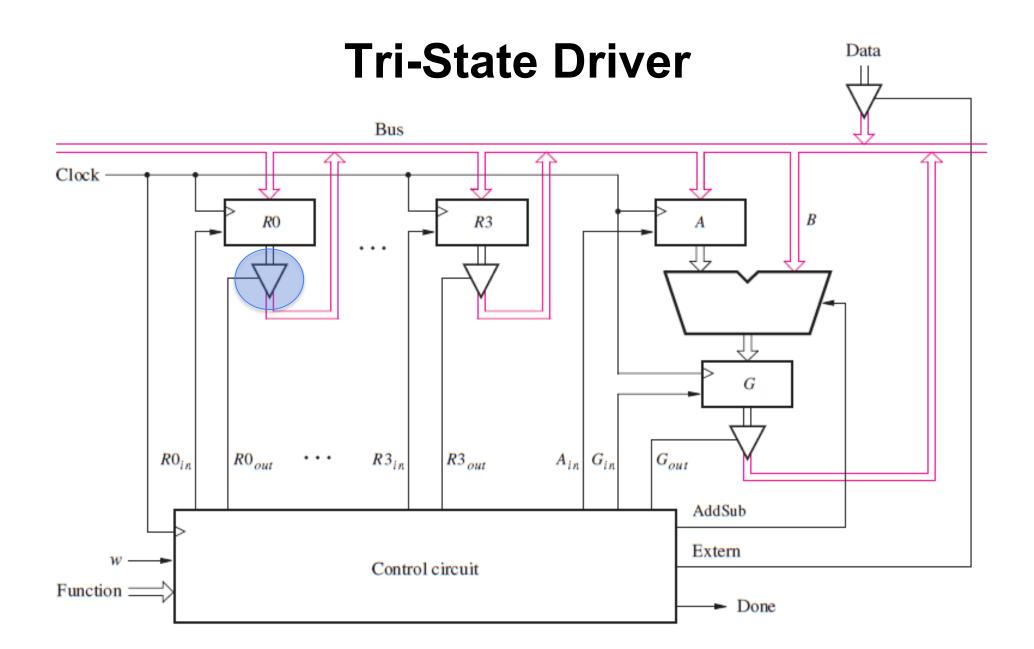

#### A Closer Look at the Tri-State Driver

[ Figure 7.9 from the textbook ]

[ Figure 7.9 from the textbook ]

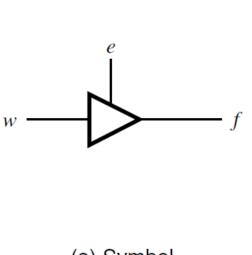

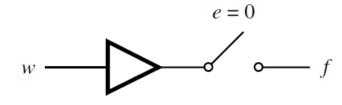

## Tri-state driver (see Appendix B for more details)

(b) Equivalent circuit

Z: High impedance state

| e | w | f |

|---|---|---|

| 0 | 0 | Z |

| 0 | 1 | Z |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

|   |   |   |

(c) Truth table

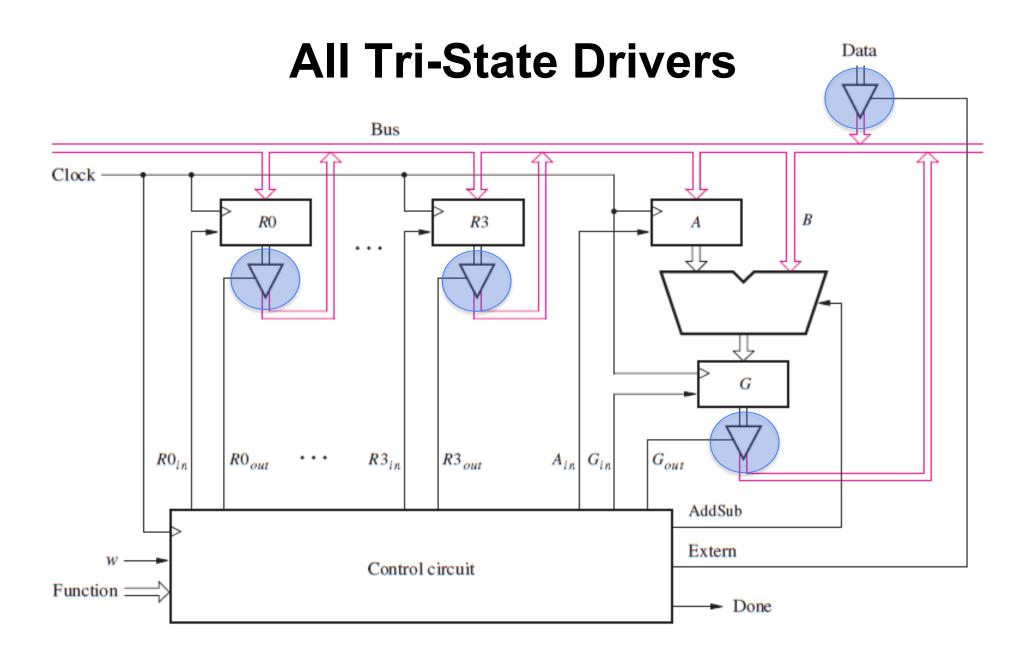

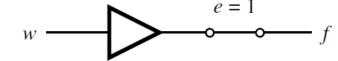

#### **Tri-state driver**

(see Appendix B for more details)

- Alternative way to implement a data bus

- Allows several devices to be connected to a single wire (this is not possible with regular logic gates because their outputs are always active; an OR gate is needed)

- Note that at any time, at most one of e0, e1, e2, and e3 can be set to 1

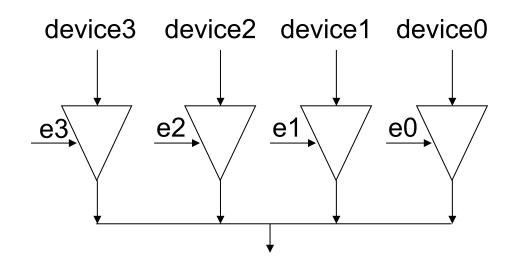

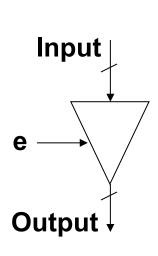

## An n-bit Tri-State Driver can be constructed using n 1-bit tri-state buffers

## 2-Bit Register

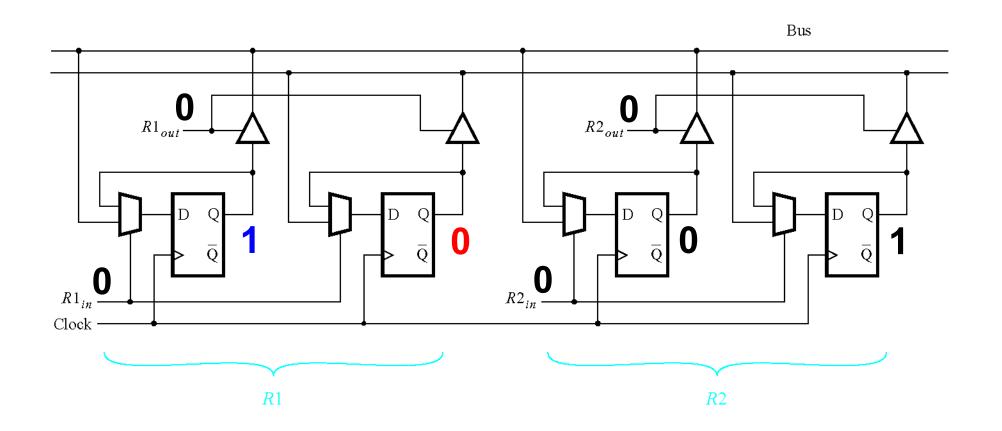

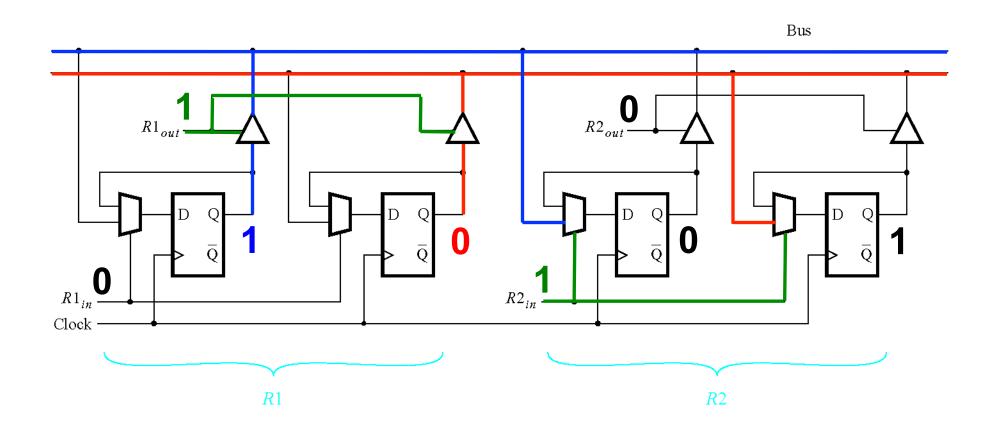

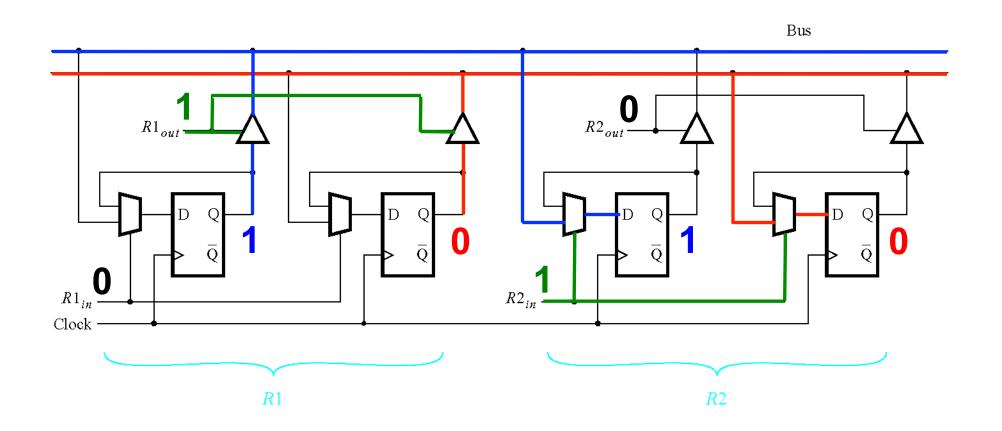

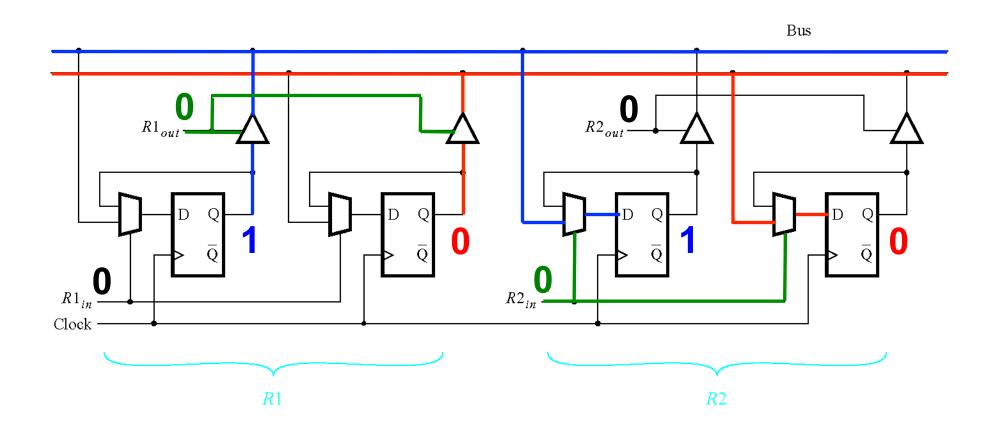

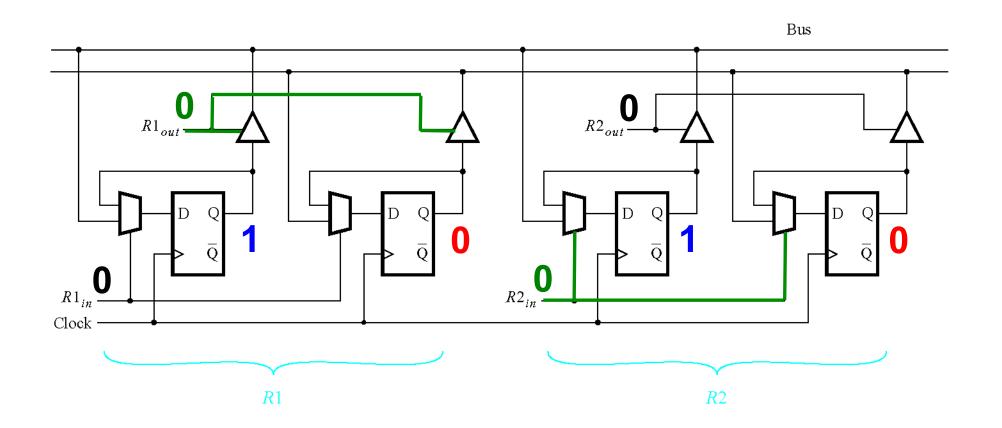

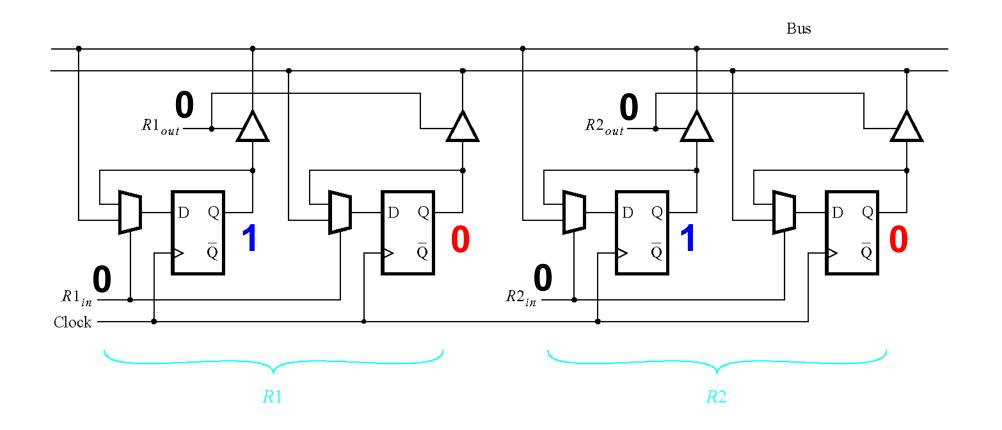

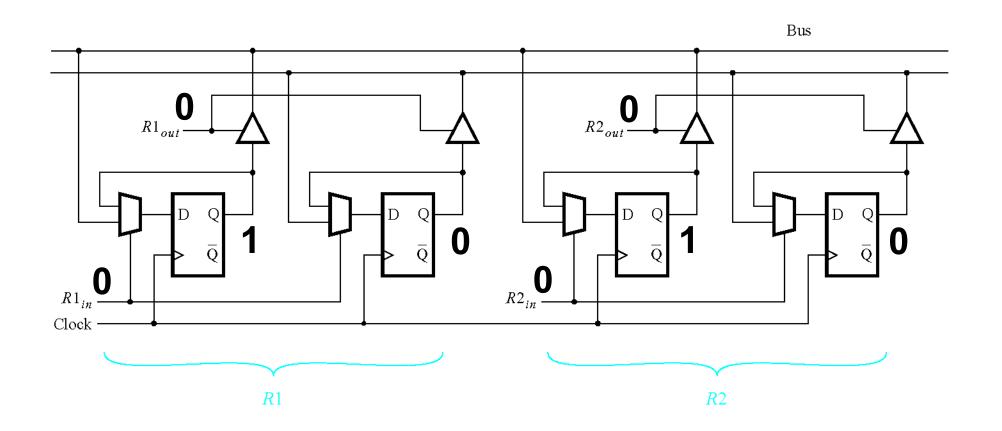

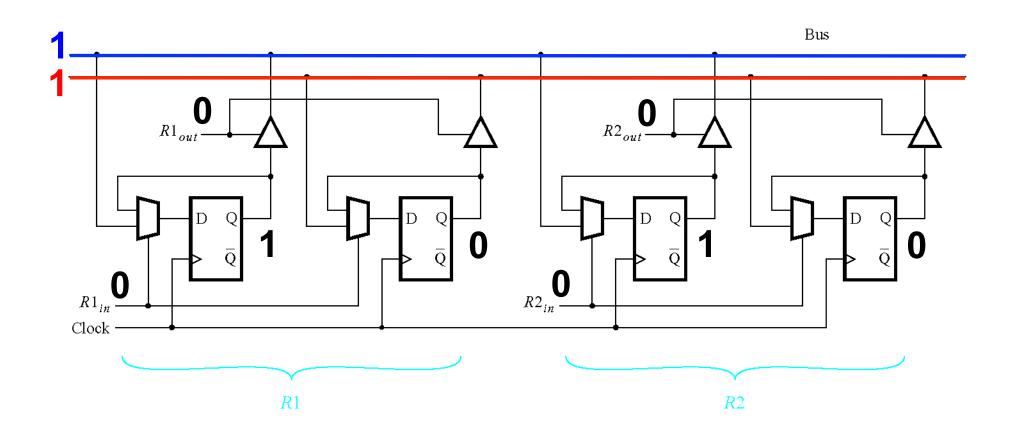

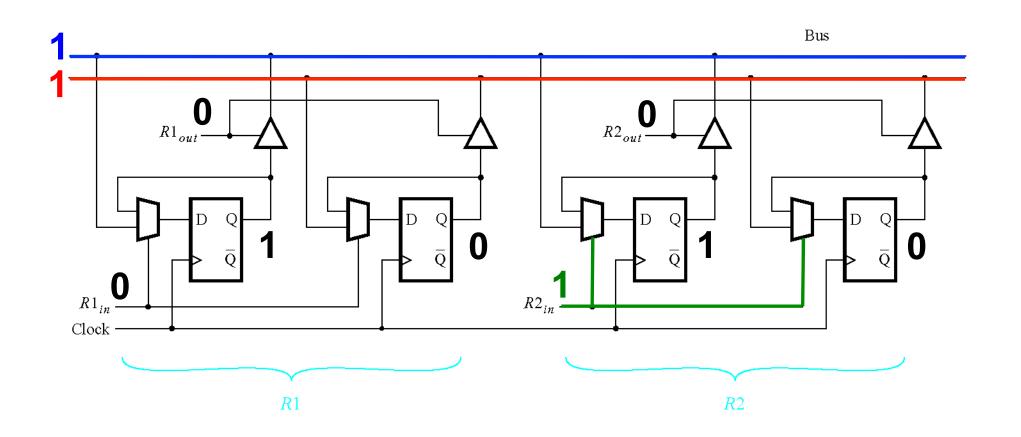

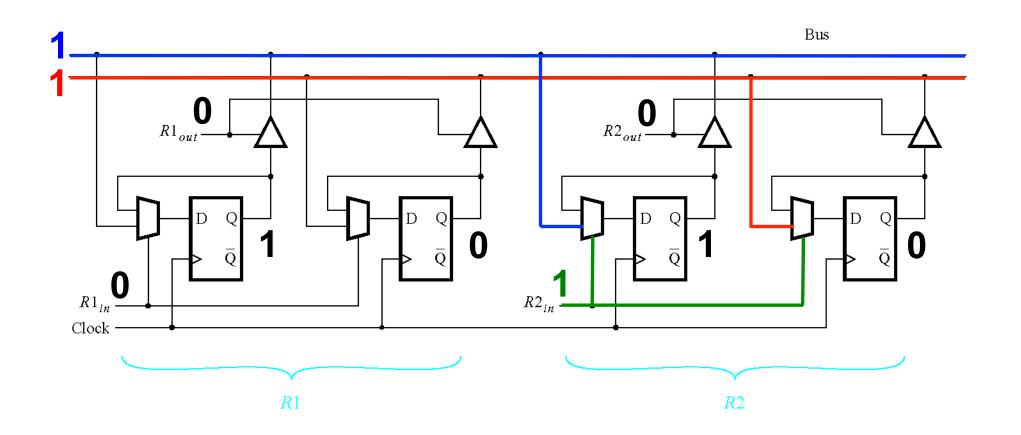

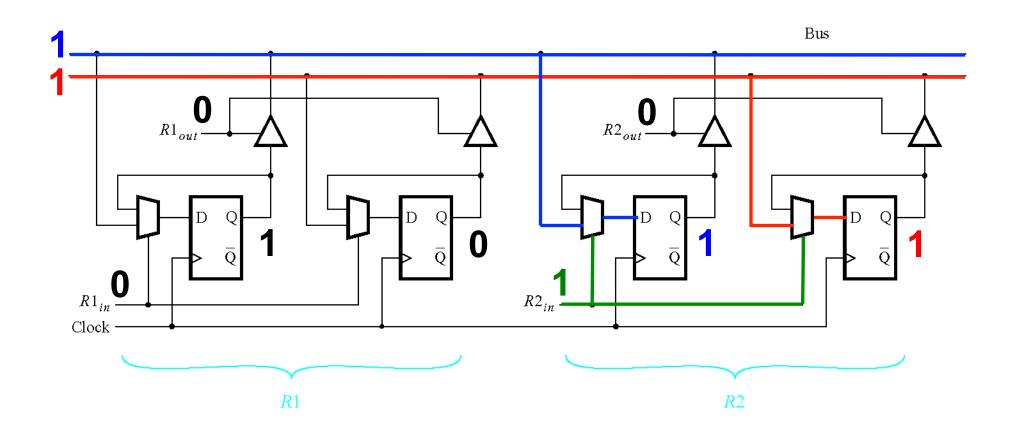

# How to connect two 2-bit registers to a bus (using tri-state drivers)

This shows only two 2-bit registers, but this design scales to more and larger registers.

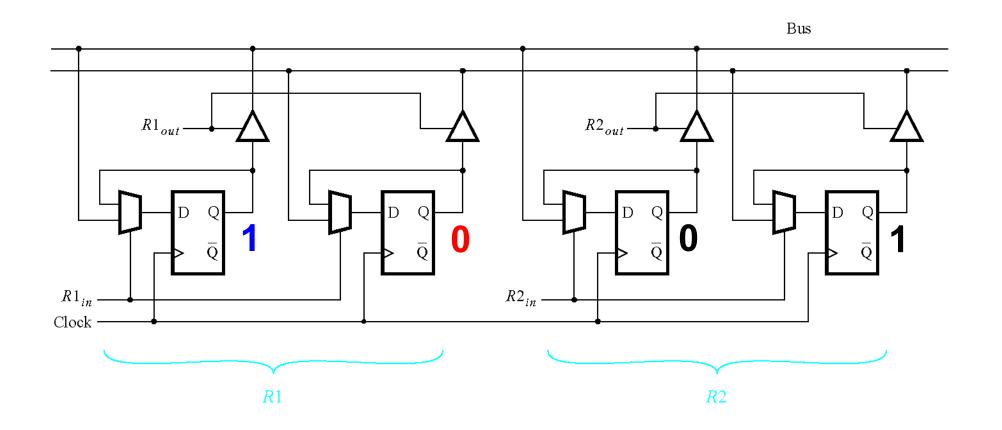

Register 1 stores the number  $2_{10} = 10_2$  Register 2 stores the number  $1_{10} = 01_2$

Initially all control inputs are set to 0 (no reading or writing allowed).

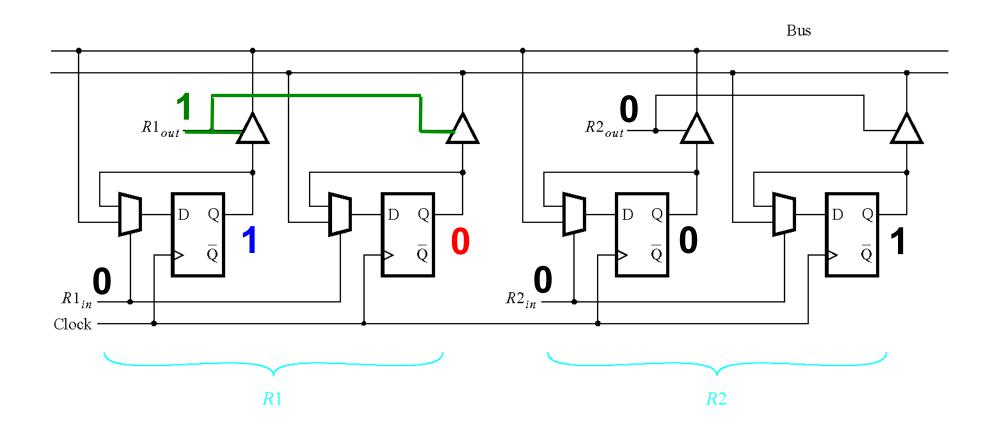

R1<sub>out</sub> is set to 1 (this enables reading from register 1).

The bits of R1 are now on the data bus (2-bit data bus in this case).

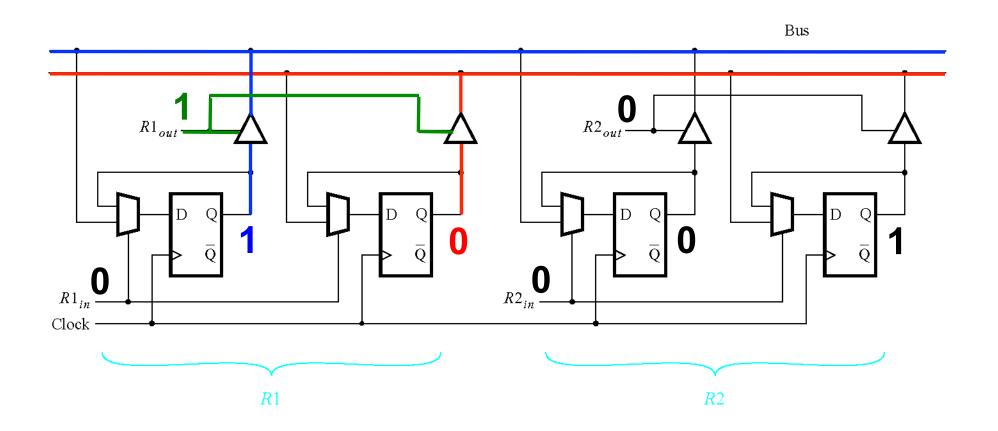

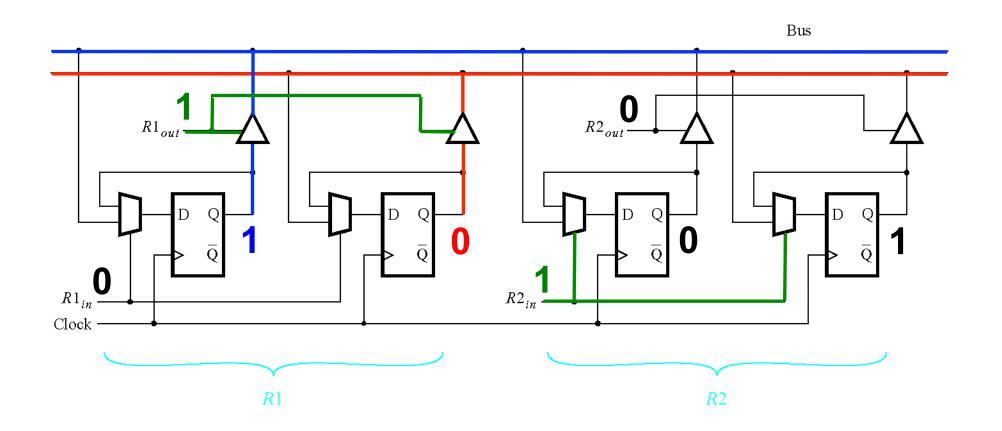

R2<sub>in</sub> is set to 1 (this enables writing to register 2).

The bits of R1 are still on the bus and they propagate to the multiplexers...

... and on the next positive clock edge to the outputs of the flip-flops of R2.

After the copy is complete R1<sub>out</sub> and R2<sub>in</sub> are set to 0.

All control inputs are now disabled (no reading or writing is allowed).

Register 2 now holds the same value as register 1.

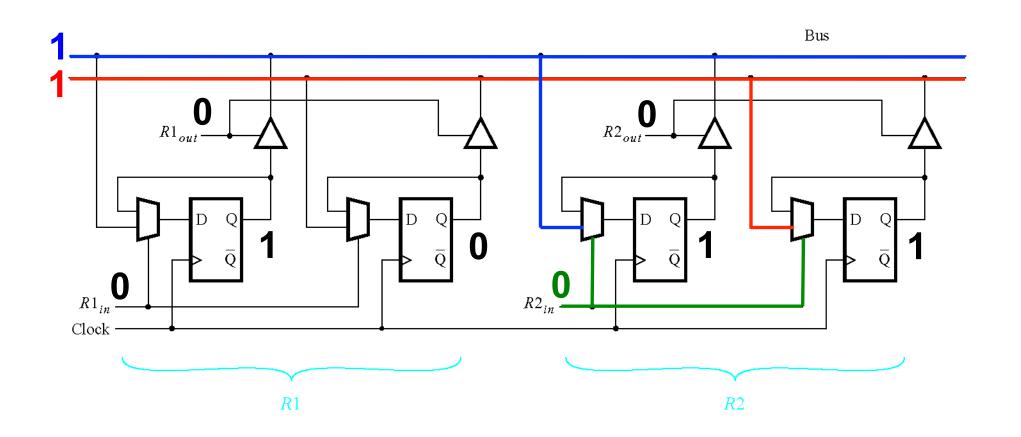

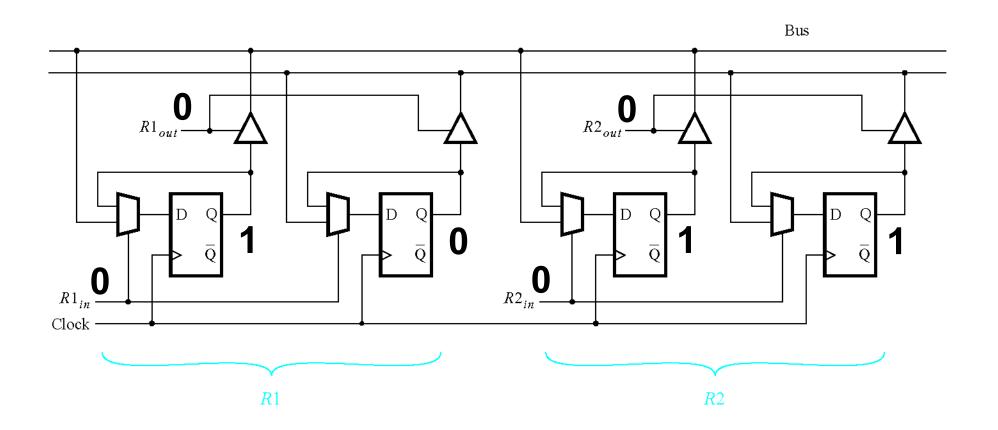

## **Another Example**

Initially all control inputs are set to 0 (no reading or writing allowed).

The number  $3_{10}=11_2$  is placed on the 2-bit data bus.

R2<sub>in</sub> is set to 1 (this enables writing to register 2).

The bits of the data propagate the multiplexers...

... and on the next positive clock edge to the outputs of the flip-flops of R2.

After the loading is complete R2<sub>in</sub> is set to 0.

Register 2 now stores the number  $3_{10}=11_2$ .

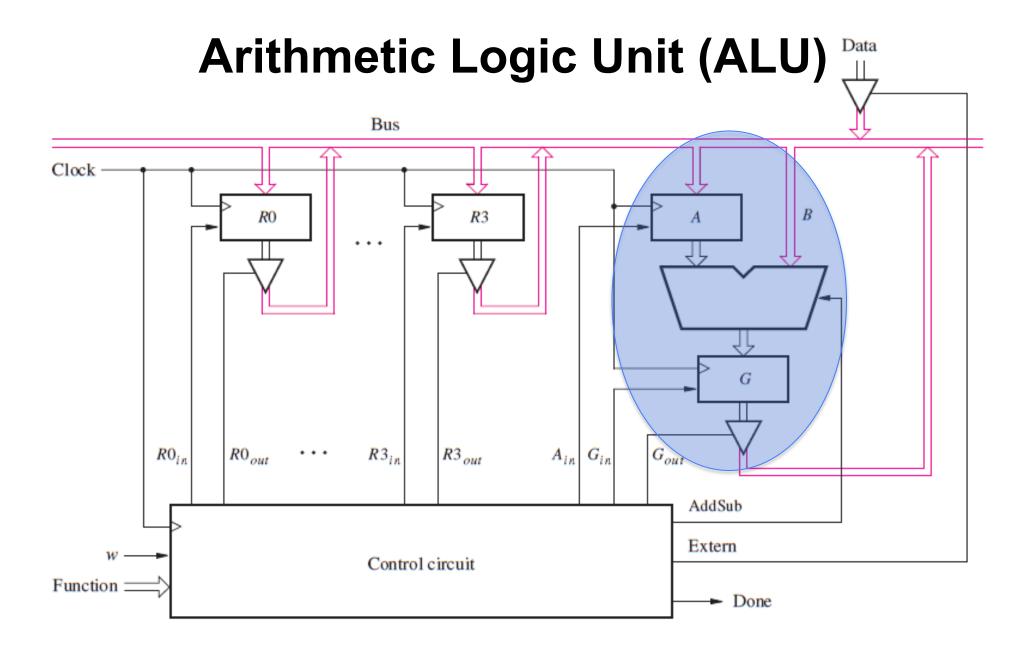

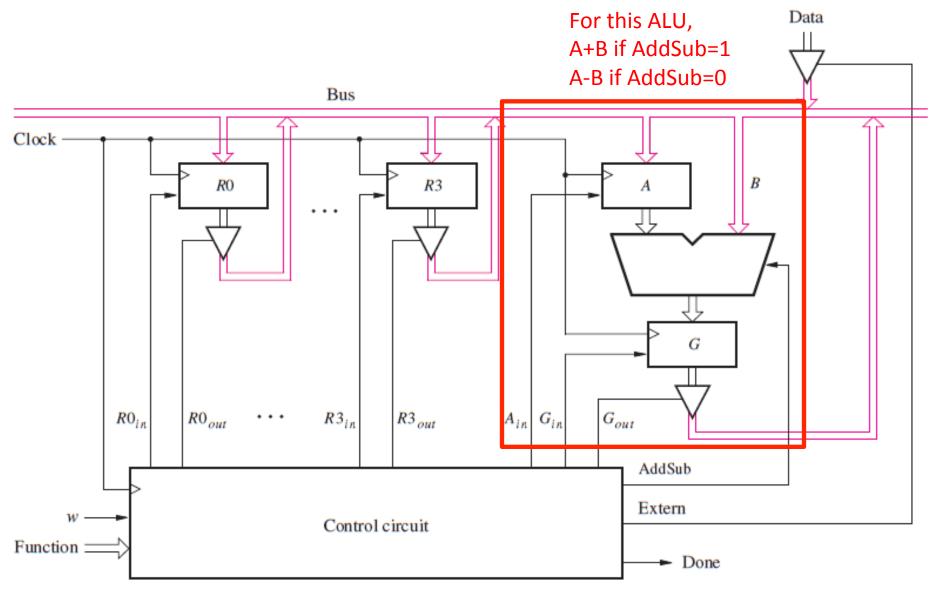

# A Closer Look at the Arithmetic Logic Unit (ALU)

[ Figure 7.9 from the textbook ]

### **4-Bit Register**

[ Figure 7.9 from the textbook ]

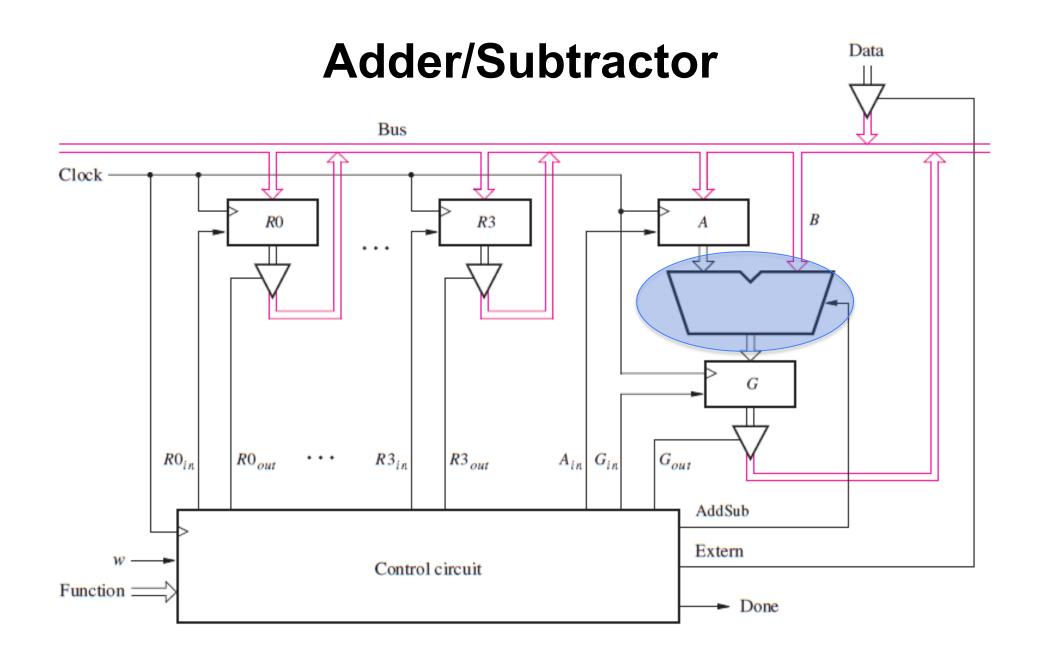

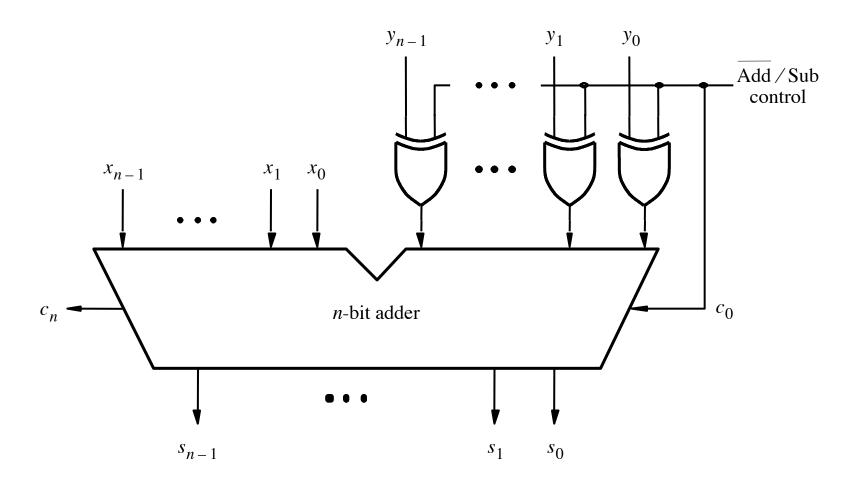

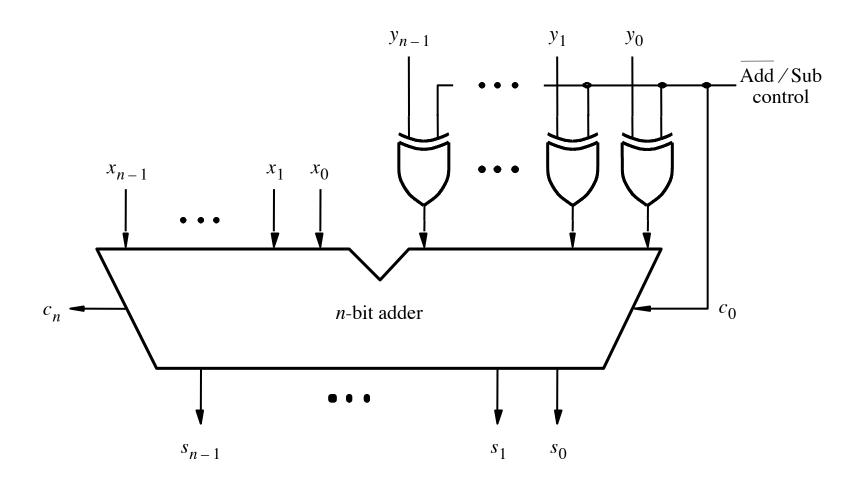

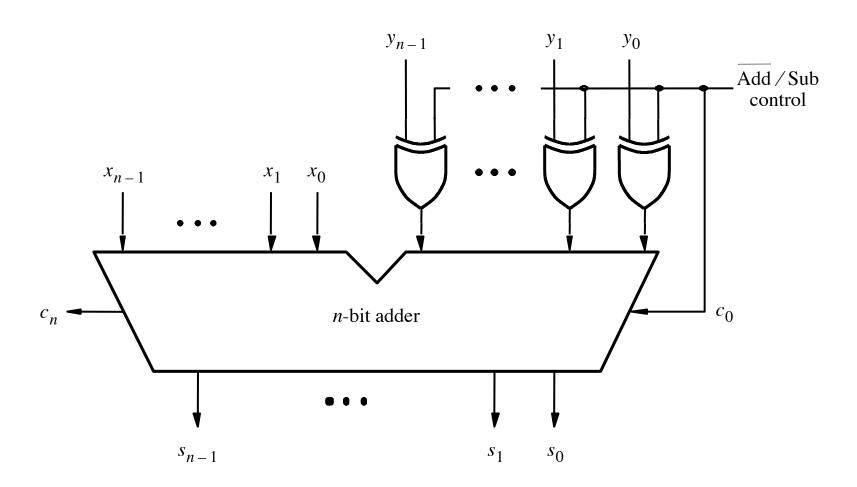

#### Adder/Subtractor unit

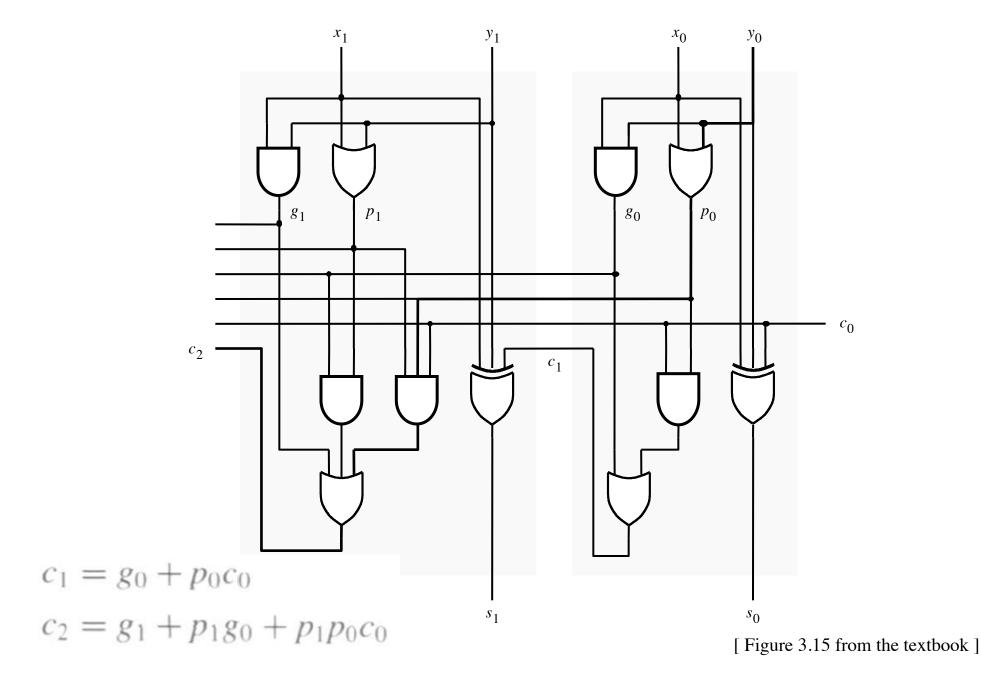

#### The first two stages of a carry-lookahead adder

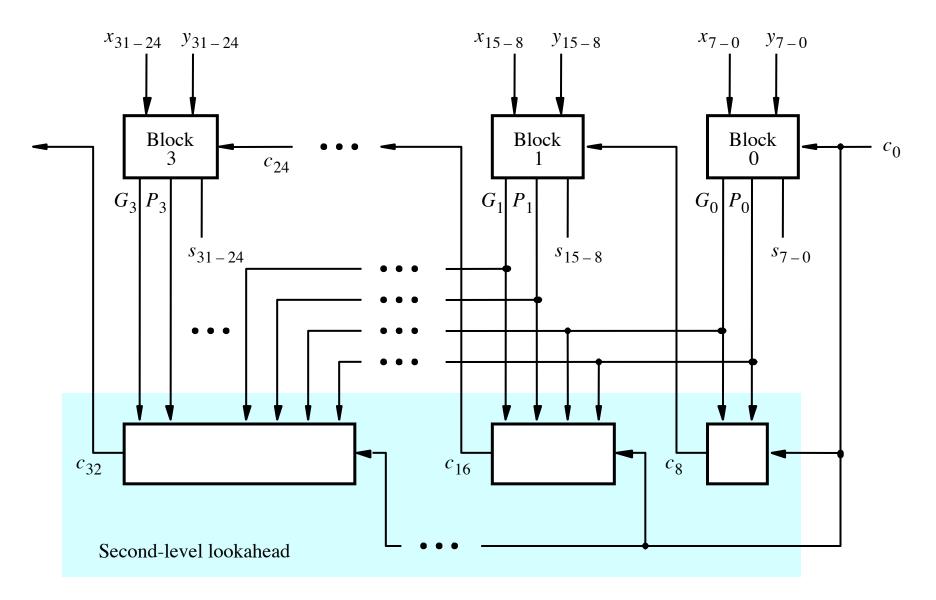

#### A hierarchical carry-lookahead adder

[ Figure 3.17 from the textbook ]

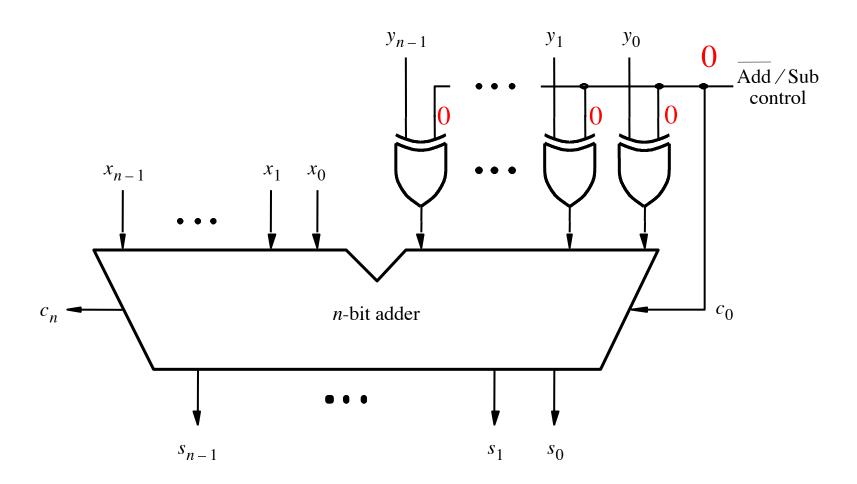

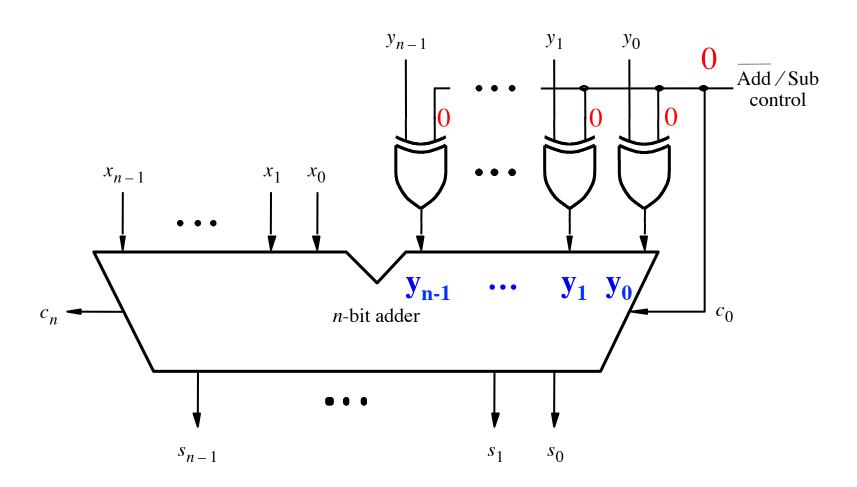

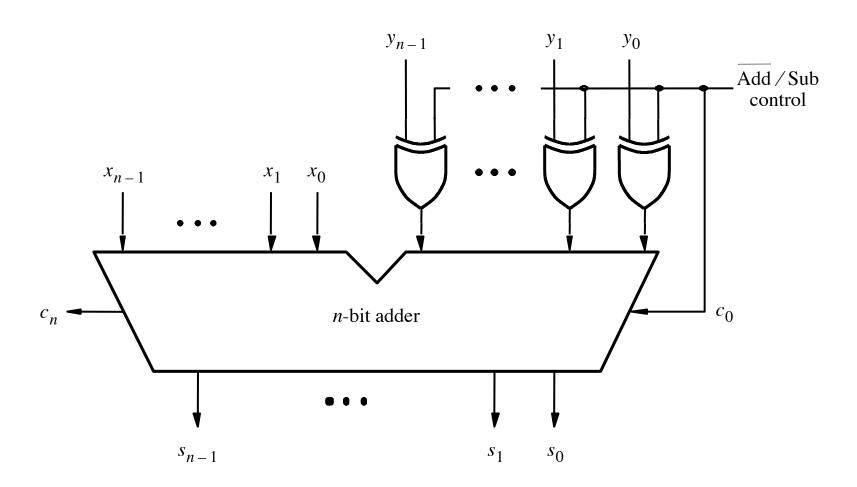

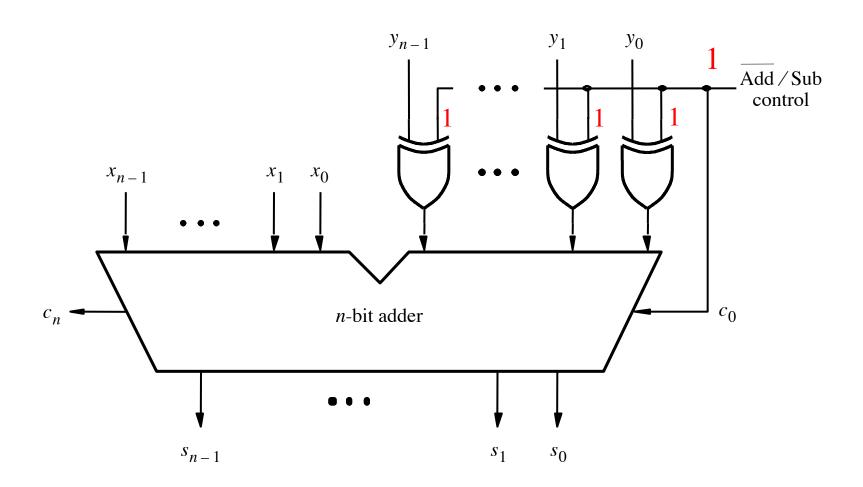

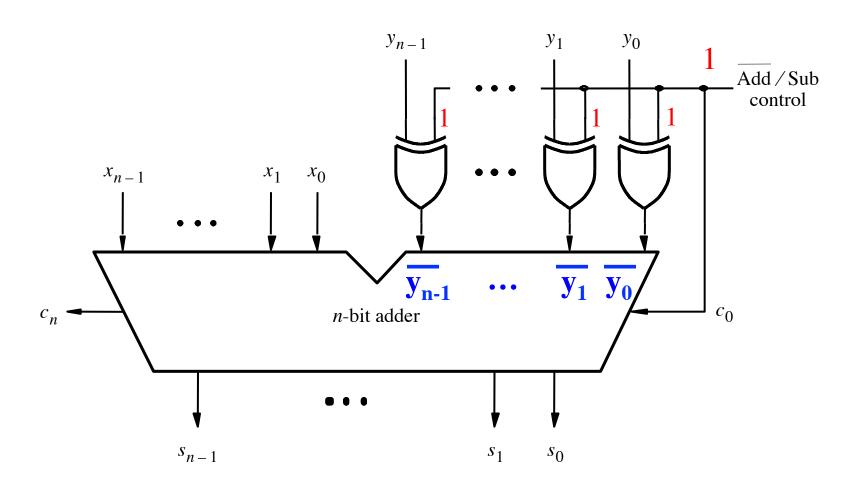

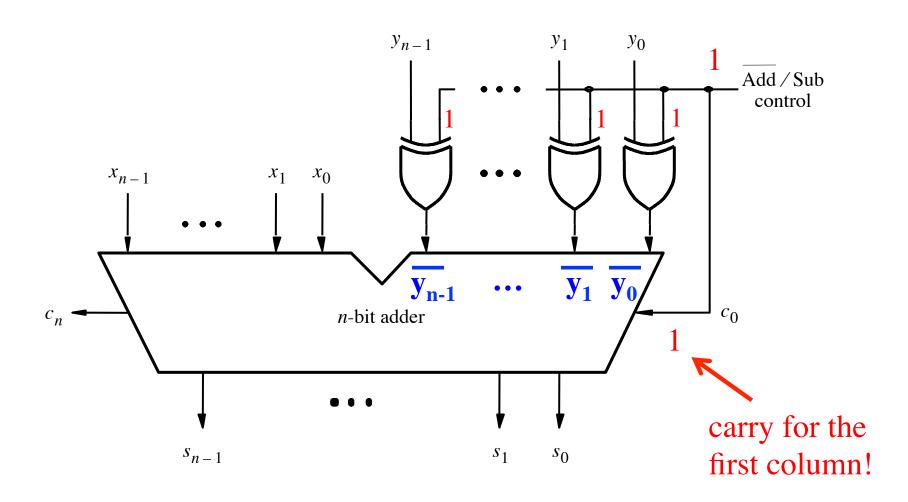

#### Adder/subtractor unit

Subtraction can be performed by simply adding the 2's complement of the second number, regardless of the signs of the two numbers.

Thus, the same adder circuit can be used to perform both addition and subtraction !!!

#### Adder/subtractor unit

[ Figure 3.12 from the textbook ]

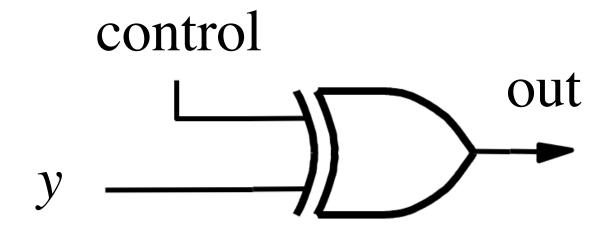

#### **XOR Tricks**

| control | y | out |

|---------|---|-----|

| 0       | 0 | 0   |

| 0       | 1 | 1   |

| 1       | 0 | 1   |

| 1       | 1 | 0   |

|         |   |     |

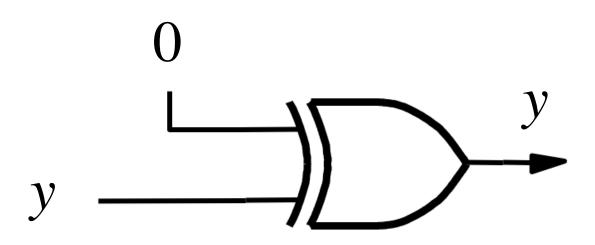

## XOR as a repeater

| control | y | out |

|---------|---|-----|

| 0       | 0 | 0   |

| 0       | 1 | 1   |

| 1       | 0 | 1   |

| 1       | 1 | 0   |

|         |   |     |

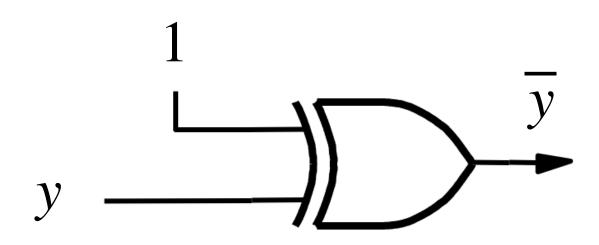

#### XOR as an inverter

| control | y | out |

|---------|---|-----|

| 0       | 0 | 0   |

| 0       | 1 | 1   |

| 1       | 0 | 1   |

| 1       | 1 | 0   |

|         |   |     |

#### Addition: when control = 0

#### Addition: when control = 0

[ Figure 3.12 from the textbook ]

## Addition: when control = 0

[ Figure 3.12 from the textbook ]

[ Figure 3.12 from the textbook ]

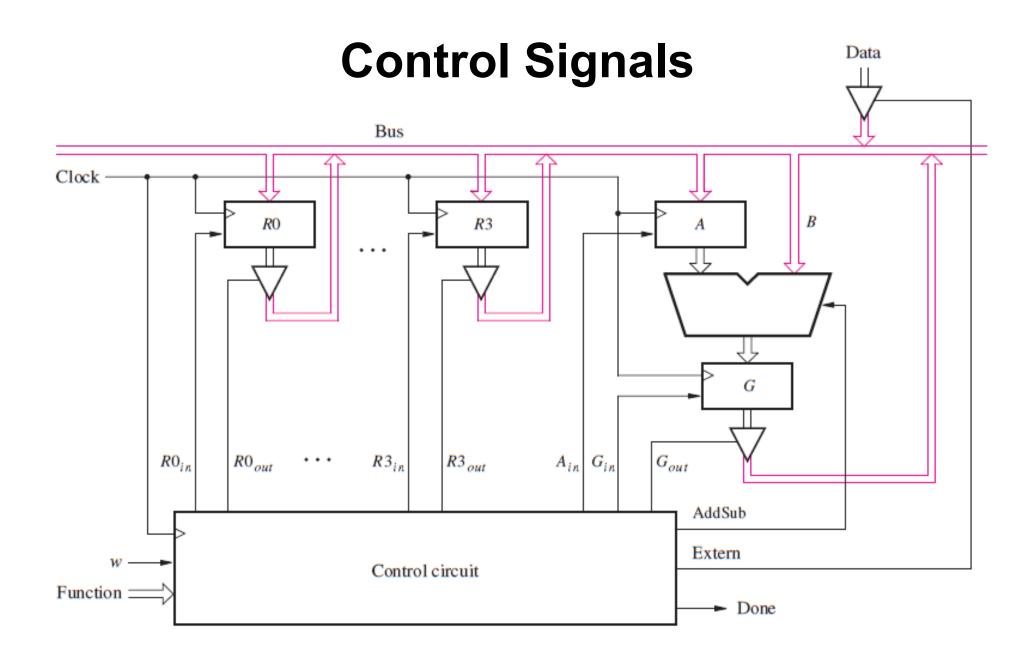

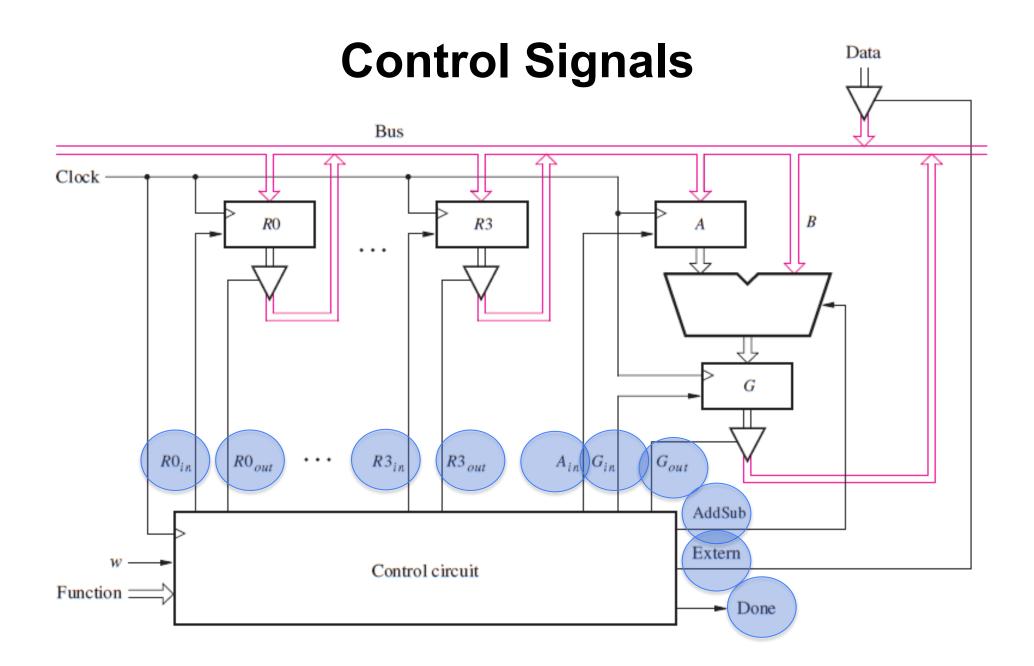

#### A Closer Look at the Control Circuit

[ Figure 7.9 from the textbook ]

[ Figure 7.9 from the textbook ]

# Design a FSM with input w and outputs

• **R0**<sub>in</sub>

• A<sub>in</sub>

AddSub

• R0<sub>out</sub>

Extern

• R1<sub>in</sub>

• Gin

• **R1**<sub>out</sub>

• G<sub>out</sub>

Done

• R2<sub>in</sub>

Clear

- R2<sub>out</sub>

- R3<sub>in</sub>

- FR<sub>in</sub>

- R3<sub>out</sub>

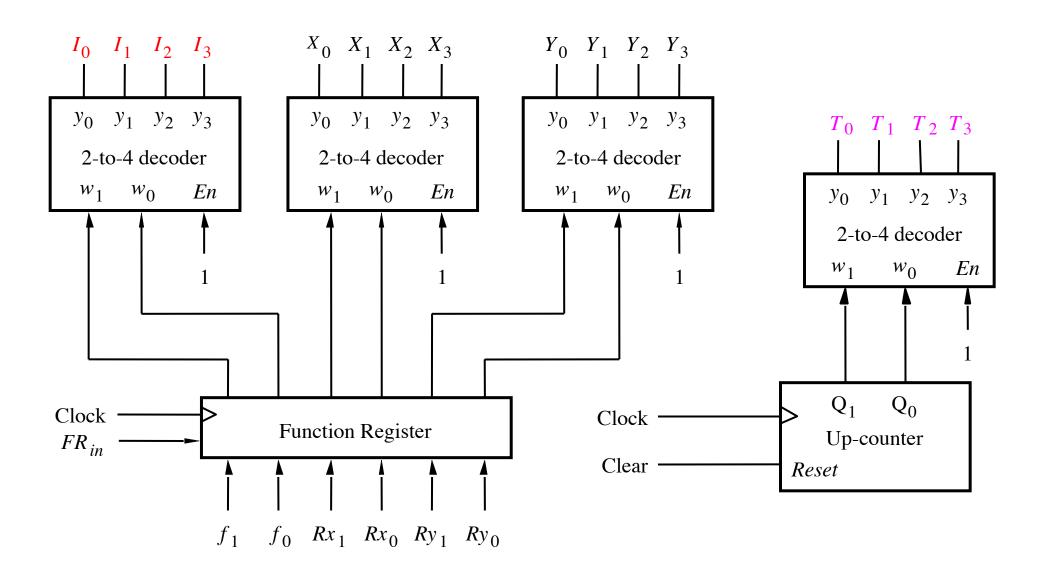

# Design a FSM with input w and outputs

• **R0**<sub>in</sub> • R0<sub>out</sub> • A<sub>in</sub>

- AddSub

- T<sub>0</sub> • X<sub>0</sub>

Extern

• X<sub>1</sub>

• **R1**<sub>in</sub>

• Gin

• X<sub>2</sub> • T<sub>2</sub>

• T₁

• R1<sub>out</sub>

• G<sub>out</sub>

Done

• T<sub>3</sub> • X<sub>3</sub>

• **R2**<sub>in</sub>

Clear

• R2<sub>out</sub>

• **R3**<sub>in</sub>

• FR<sub>in</sub>

• Y<sub>0</sub> • Y<sub>1</sub> • Y<sub>2</sub> • Y<sub>3</sub>

• R3<sub>out</sub>

These are helper outputs that are one-hot encoded. They are used to simplify the expressions for the other outputs.

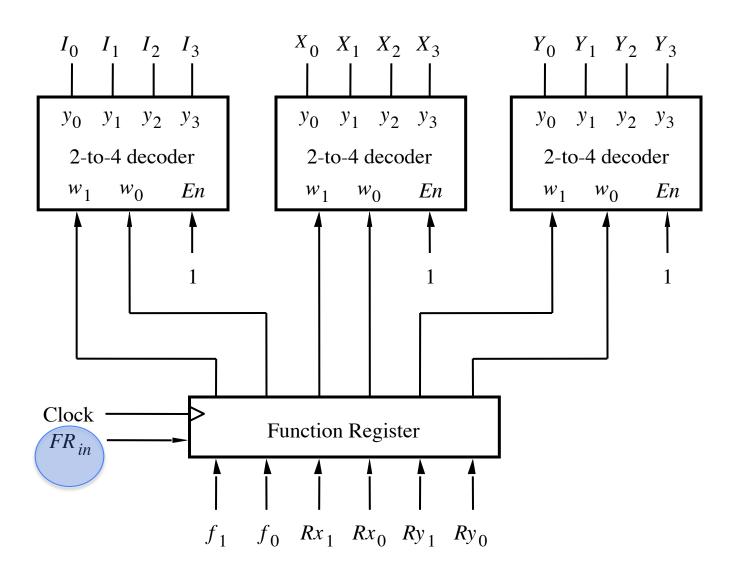

[ Figure 7.11 from the textbook ]

[ Figure 7.11 from the textbook ]

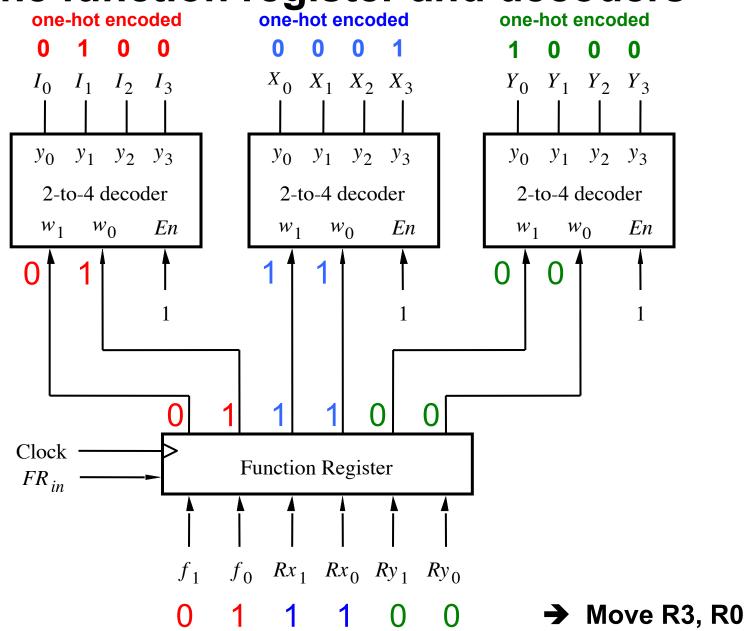

| Operation |     |      | Fur | nction Performed     |

|-----------|-----|------|-----|----------------------|

| Load      | Rx, | Data | Rx  | <b>←</b> Data        |

| Move      | Rx, | Ry   | Rx  | <b>←</b> [Ry]        |

| Add       | Rx, | Ry   | Rx  | <b>←</b> [Rx] + [Ry] |

| Sub       | Rx, | Ry   | Rx  | <b>←</b> [Rx] - [Ry] |

| Operation |     |      | Fur | nction Performed     |

|-----------|-----|------|-----|----------------------|

| Load      | Rx, | Data | Rx  | <b>←</b> Data        |

| Move      | Rx, | Ry   | Rx  | <b>←</b> [Ry]        |

| Add       | Rx, | Ry   | Rx  | <b>←</b> [Rx] + [Ry] |

| Sub       | Rx, | Ry   | Rx  | <b>←</b> [Rx] - [Ry] |

Where Rx and Ry can be one of four possible options: R0, R1, R2, and R3

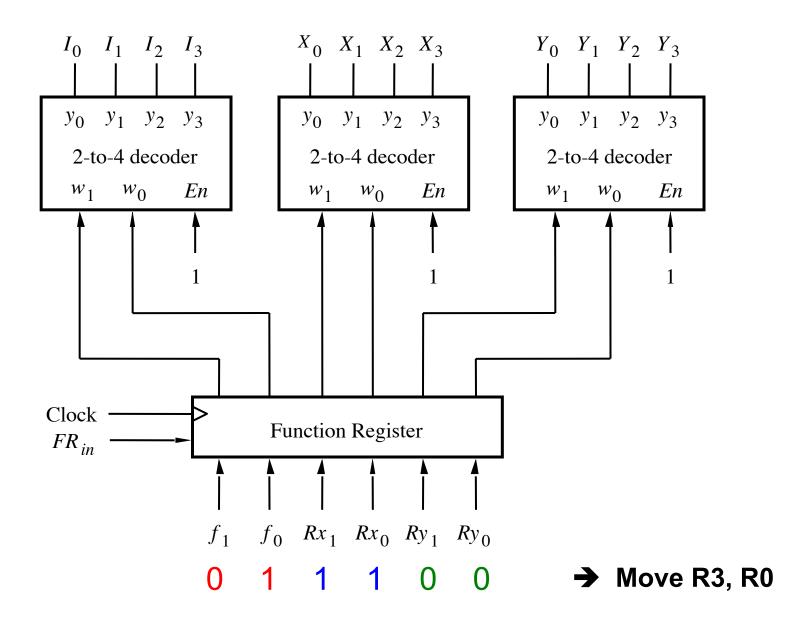

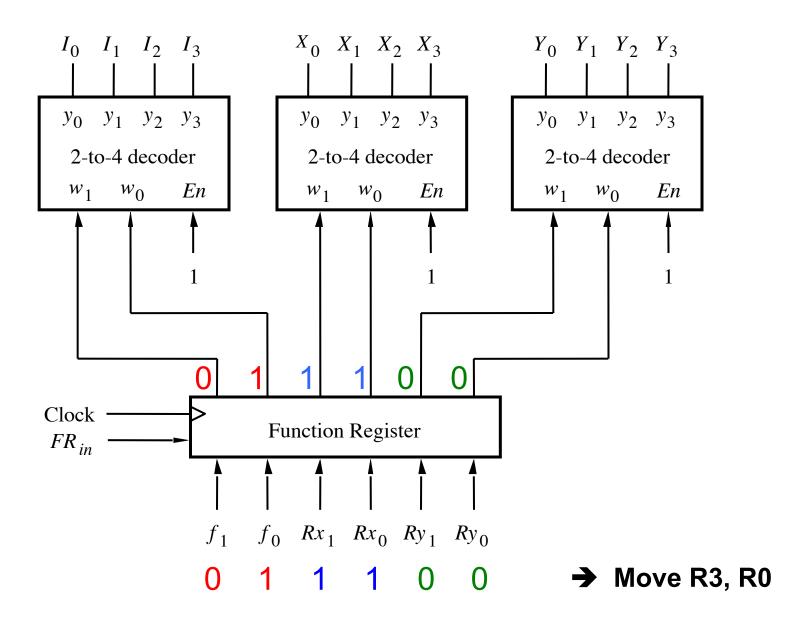

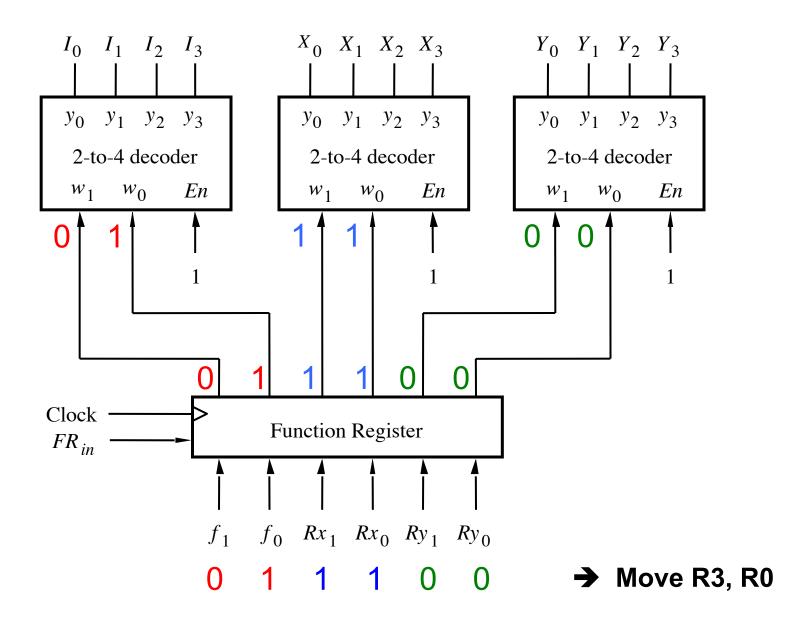

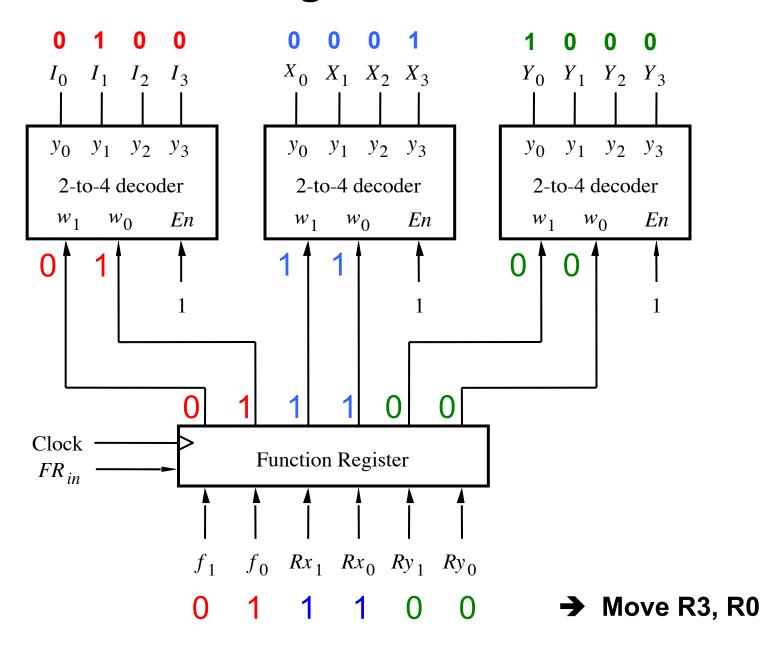

| $f_1$ | $f_{\theta}$ | Function |

|-------|--------------|----------|

| 0     | 0            | Load     |

| 0     | 1            | Move     |

| 1     | 0            | Add      |

| 1     | 1            | Sub      |

| $Rx_1$ | $Rx_{\theta}$ | Register |

|--------|---------------|----------|

| 0      | 0             | R0       |

| 0      | 1             | R1       |

| 1      | 0             | R2       |

| 1      | 1             | R3       |

| $Ry_1$ | $Ry_{\theta}$ | Register |

|--------|---------------|----------|

| 0      | 0             | R0       |

| 0      | 1             | R1       |

| 1      | 0             | R2       |

| 1      | 1             | R3       |

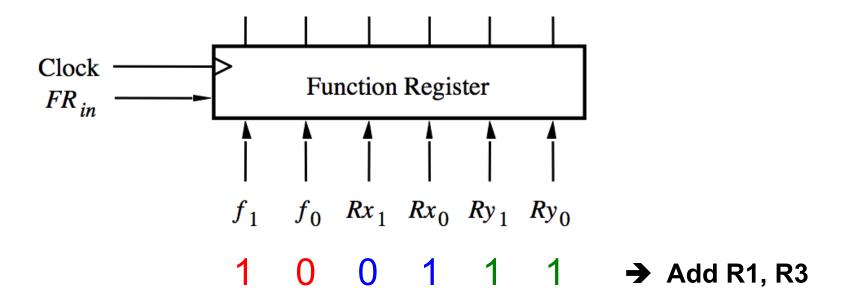

| $f_1$ | $f_{\theta}$ | Function |

|-------|--------------|----------|

| 0     | 0            | Load     |

| 0     | 1            | Move     |

| 1     | 0            | Add      |

| 1     | 1            | Sub      |

| $Rx_1$ | $Rx_{\theta}$ | Register |

|--------|---------------|----------|

| 0      | 0             | R0       |

| 0      | 1             | R1       |

| 1      | 0             | R2       |

| 1      | 1             | R3       |

| $Ry_1$ | $Ry_{\theta}$ | Register |

|--------|---------------|----------|

| 0      | 0             | R0       |

| 0      | 1             | R1       |

| 1      | 0             | R2       |

| 1      | 1             | R3       |

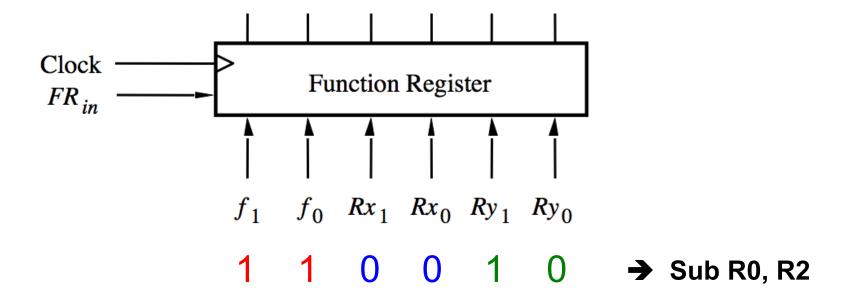

| $f_1$ | $f_{\theta}$ | Function |

|-------|--------------|----------|

| 0     | 0            | Load     |

| 0     | 1            | Move     |

| 1     | 0            | Add      |

| 1     | 1            | Sub      |

| $Rx_1$ | $Rx_{\theta}$ | Register |

|--------|---------------|----------|

| 0      | 0             | R0       |

| 0      | 1             | R1       |

| 1      | 0             | R2       |

| 1      | 1             | R3       |

| $Ry_1$ | $Ry_{\theta}$ | Register |

|--------|---------------|----------|

| 0      | 0             | R0       |

| 0      | 1             | R1       |

| 1      | 0             | R2       |

| 1      | 1             | R3       |

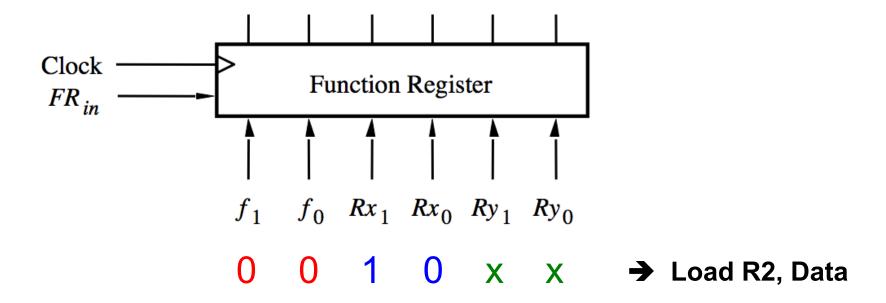

| $f_1$ | $f_{\theta}$ | Function |

|-------|--------------|----------|

| 0     | 0            | Load     |

| 0     | 1            | Move     |

| 1     | 0            | Add      |

| 1     | 1            | Sub      |

| $Rx_1$ | $Rx_{\theta}$ | Register |

|--------|---------------|----------|

| 0      | 0             | R0       |

| 0      | 1             | R1       |

| 1      | 0             | R2       |

| 1      | 1             | R3       |

| $Ry_1$ | $Ry_{\theta}$ | Register |

|--------|---------------|----------|

| 0      | 0             | R0       |

| 0      | 1             | R1       |

| 1      | 0             | R2       |

| 1      | 1             | R3       |

| $f_1$ | $f_{\theta}$ | Function |

|-------|--------------|----------|

| 0     | 0            | Load     |

| 0     | 1            | Move     |

| 1     | 0            | Add      |

| 1     | 1            | Sub      |

| $Rx_1$ | $Rx_{\theta}$ | Register |

|--------|---------------|----------|

| 0      | 0             | R0       |

| 0      | 1             | R1       |

| 1      | 0             | R2       |

| 1      | 1             | R3       |

| $Ry_1$ | $Ry_{\theta}$ | Register |

|--------|---------------|----------|

| 0      | 0             | R0       |

| 0      | 1             | R1       |

| 1      | 0             | R2       |

| 1      | 1             | R3       |

#### Similar Encoding is Used by Modern Chips

#### MIPS32 Add Immediate Instruction

| 001000  | 00001  | 00010  | 000000101011110 |

|---------|--------|--------|-----------------|

| OP Code | Addr 1 | Addr 2 | Immediate value |

Equivalent mnemonic:

addi \$r1, \$r2, 350

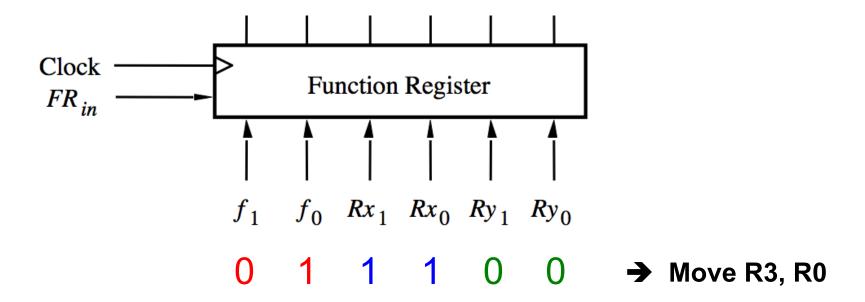

# Sample Assembly Language Program For This Processor

Move R3, R0

Add R1, R3

Sub R0, R2

Load R2, Data

| Machine Language | Assembly Language | Meaning / Interpretation |

|------------------|-------------------|--------------------------|

| 011100           | Move R3, R0       | R3 <b>←</b> [R0]         |

| 100111           | Add R1, R3        | R1 <b>(</b> [R1] + [R3]  |

| 110010           | Sub R0, R2        | R0 ← [R0] - [R2]         |

| 001000           | Load R2, Data     | R2 🗲 Data                |

|                  |                   |                          |

|                  |                   |                          |

| Machine Language | Assembly Language | Meaning / Interpretation |

|------------------|-------------------|--------------------------|

| 011100           | Move R3, R0       | R3 <b>←</b> [R0]         |

| 100111           | Add R1, R3        | R1 <b>(</b> [R1] + [R3]  |

| 110010           | Sub R0, R2        | R0 ← [R0] - [R2]         |

| 001000           | Load R2, Data     | R2 ← Data                |

|                  |                   |                          |

|                  |                   | 1                        |

| Machine Language                     | Assembly Language                               | Meaning / Interpretation                              |

|--------------------------------------|-------------------------------------------------|-------------------------------------------------------|

| 011100<br>100111<br>110010<br>001000 | Move R3, R0 Add R1, R3 Sub R0, R2 Load R2, Data | R3 ← [R0] R1 ← [R1] + [R3] R0 ← [R0] - [R2] R2 ← Data |

|                                      |                                                 |                                                       |

For short, each line can be expressed as a hexadecimal number

| Machine Language | Assembly Language | Meaning / Interpretation |

|------------------|-------------------|--------------------------|

| 1C               | Move R3, R0       | R3 <b>←</b> [R0]         |

| 27               | Add R1, R3        | R1 <b>(</b> [R1] + [R3]  |

| 32               | Sub R0, R2        | R0 ← [R0] - [R2]         |

| 80               | Load R2, Data     | R2 <b>←</b> Data         |

|                  |                   |                          |

|                  |                   |                          |

```

; memcpy(dst, src, len)

Intel 8086

; Copy a block of memory from one location to another.

; Entry stack parameters

[BP+6] = len, Number of bytes to copy

[BP+4] = src, Address of source data block

[BP+2] = dst, Address of target data block

; Return registers

AX = Zero

0000:1000

1000h

: Start at 0000:1000h

org

0000:1000

proc

memcpy

0000:1000 55

; Set up the call frame

push

bp

0000:1001 89 E5

bp,sp

mov

0000:1003 06

push

es

; Save ES

cx,[bp+6] ; Set CX = len

0000:1004 8B 4E 06

mov

done ; If len=0, return

0000:1007 E3 11

jcxz

0000:1009 8B 76 04

mov

si,[bp+4] ; Set SI = src

di,[bp+2] ; Set DI = dst

00000:100C 8B 7E 02

mov

0000:100F 1E

push

ds

: Set ES = DS

0000:1010 07

pop

es

0000:1011 8A 04

loop

mov

0000:1013 88 05

[di],al ; Store AL to [dst]

mov

si

0000:1015 46

inc

; Increment src

0000:1016 47

inc

di

: Increment dst

0000:1017 49

dec

CX

: Decrement len

0000:1018 75 F7

loop

jnz

; Repeat the loop

0000:101A 07

done

pop

es

: Restore ES

0000:101B 5D

; Restore previous call frame

pop

bp

0000:101C 29 CO

; Set AX = 0

sub

ax,ax

0000:101E C3

: Return

ret

0000:101F

end proc

[http://en.wikipedia.org/wiki/Intel 8086]

```

```

; memcpy(dst, src, len)

Intel 8086

; Copy a block of memory from one location to another.

; Entry stack parameters

[BP+6] = len, Number of bytes to copy

[BP+4] = src, Address of source data block

[BP+2] = dst, Address of target data block

Memory Address

; Return registers

AX = Zero

0000:1000

1000h

: Start at 0000:1000h

org

0000:1000

proc

memcpy

0000:1000 55

; Set up the call frame

push

bp

0000:1001 89 E5

bp,sp

mov

0000:1003 06

; Save ES

push

es

cx,[bp+6] ; Set CX = len

0000:1004 8B 4E 06

mov

0000:1007 E3 11

; If len=0, return

jcxz

done

0000:1009 8B 76 04

si,[bp+4] ; Set SI = src

mov

0000:100C 8B 7E 02

di,[bp+2] ; Set DI = dst

mov

0000:100F 1E

push

: Set ES = DS

0000:1010 07

pop

0000:1011 8A 04

al,[si]

; Load AL from [src]

loop

mov

0000:1013 88 05

[di],al

; Store AL to [dst]

mov

0000:1015 46

inc

si

: Increment src

0000:1016 47

; Increment dst

inc

di

0000:1017 49

dec

CX

: Decrement len

0000:1018 75 F7

jnz

loop

; Repeat the loop

0000:101A 07

done

es

: Restore ES

pop

0000:101B 5D

; Restore previous call frame

pop

bp

0000:101C 29 C0

; Set AX = 0

sub

ax,ax

0000:101E C3

: Return

ret

0000:101F

end proc

[http://en.wikipedia.org/wiki/Intel 8086]

```

```

; memcpy(dst, src, len)

Intel 8086

; Copy a block of memory from one location to another.

; Entry stack parameters

[BP+6] = len, Number of bytes to copy

[BP+4] = src, Address of source data block

[BP+2] = dst, Address of target data block

Machine

; Return registers

Language

AX = Zero

0000:1000

org

1000h

: Start at 0000:1000h

0000:1000

memcpy

proc

0000:1000 55

; Set up the call frame

push

bp

0000:1001 89 E5

bp,sp

mov

0000:1003 06

; Save ES

push

es

cx,[bp+6] ; Set CX = len

0000:1004 8B 4E 06

mov

0000:1007 E3 11

done ; If len=0, return

icxz

0000:1009 8B 76 04

si,[bp+4] ; Set SI = src

mov

0000:100C 8B 7E 02

di,[bp+2] ; Set DI = dst

mov

0000:100F 1E

push

ds

: Set ES = DS

0000:1010 07

pop

es

0000:1011 8A 04

loop

mov

0000:1013 88 05

[di],al ; Store AL to [dst]

mov

0000:1015 46

inc

si

: Increment src

0000:1016 47

inc

di

: Increment dst

0000:1017 49

dec

CX

: Decrement len

0000:1018 75 F7

loop

jnz

; Repeat the loop

0000:101A 07

done

es

: Restore ES

pop

0000:101B 5D

; Restore previous call frame

pop

bp

0000:101C 29 C0

; Set AX = 0

sub

ax,ax

0000:101E C3

: Return

ret

0000:101F

end proc

[http://en.wikipedia.org/wiki/Intel 8086]

```

```

; memcpy(dst, src, len)

Intel 8086

; Copy a block of memory from one location to another.

; Entry stack parameters

[BP+6] = len, Number of bytes to copy

[BP+4] = src, Address of source data block

[BP+2] = dst, Address of target data block

Assembly

; Return registers

Language

AX = Zero

0000:1000

org

1000h

: Start at 0000:1000h

0000:1000

memcpy

proc

0000:1000 55

; Set up the call frame

push

bp

0000:1001 89 E5

bp,sp

mov

0000:1003 06

: Save ES

push

es

0000:1004 8B 4E 06

: Set CX = len

cx, [bp+6]

mov

; If len=0, return

0000:1007 E3 11

done

jcxz

0000:1009 8B 76 04

si,[bp+4]

; Set SI = src

mov

0000:100C 8B 7E 02

di,[bp+2]

mov

: Set DI = dst

0000:100F 1E

: Set ES = DS

push

ds

0000:1010 07

pop

es

0000:1011 8A 04

al,[si]

; Load AL from [src]

loop

mov

0000:1013 88 05

[di],al

; Store AL to [dst]

mov

0000:1015 46

inc

si

: Increment src

di

0000:1016 47

inc

: Increment dst

0000:1017 49

dec

CX

: Decrement len

0000:1018 75 F7

jnz

loop

; Repeat the loop

; Restore ES

0000:101A 07

done

es

pop

0000:101B 5D

; Restore previous call frame

pop

bp

0000:101C 29 C0

: Set AX = 0

sub

ax,ax

0000:101E C3

: Return

ret

0000:101F

end proc

[http://en.wikipedia.org/wiki/Intel 8086]

```

```

; memcpy(dst, src, len)

Intel 8086

; Copy a block of memory from one location to another.

; Entry stack parameters

[BP+6] = len, Number of bytes to copy

[BP+4] = src, Address of source data block

[BP+2] = dst, Address of target data block

; Return registers

Comments

AX = Zero

: Start at 0000:1000h

0000:1000

org

1000h

0000:1000

proc

memcpy

0000:1000 55

; Set up the call frame

push

bp

0000:1001 89 E5

bp,sp

mov

0000:1003 06

: Save ES

push

es

: Set CX = len

00000:1004 8B 4E 06

cx, [bp+6]

mov

; If len=0, return

0000:1007 E3 11

jcxz

done

; Set SI = src

0000:1009 8B 76 04

mov

si,[bp+4]

di,[bp+2]

00000:100C 8B 7E 02

mov

: Set DI = dst

: Set ES = DS

0000:100F 1E

push

ds

0000:1010 07

pop

es

al,[si]

; Load AL from [src]

0000:1011 8A 04

loop

mov

0000:1013 88 05

; Store AL to [dst]

[di],al

mov

0000:1015 46

inc

si

: Increment src

0000:1016 47

inc

di

: Increment dst

0000:1017 49

dec

CX

: Decrement len

0000:1018 75 F7

jnz

loop

; Repeat the loop

0000:101A 07

done

es

: Restore ES

pop

0000:101B 5D

; Restore previous call frame

pop

bp

0000:101C 29 CO

: Set AX = 0

sub

ax,ax

0000:101E C3

: Return

ret

0000:101F

end proc

[http://en.wikipedia.org/wiki/Intel 8086]

```

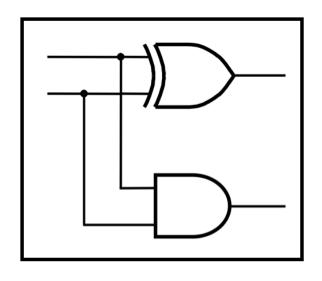

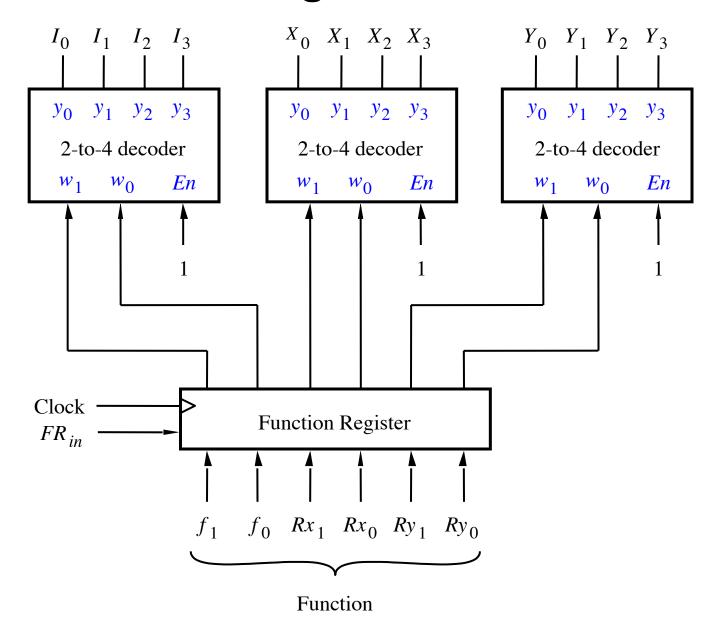

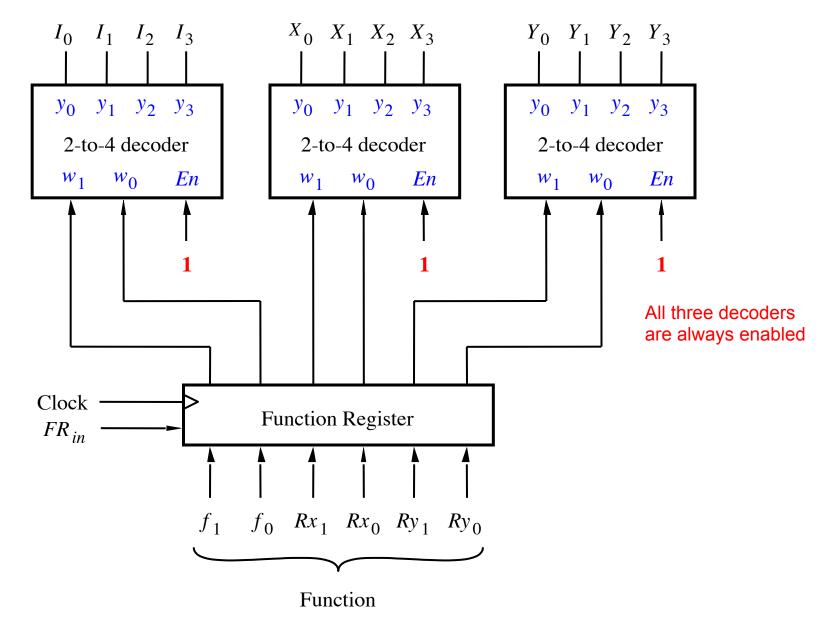

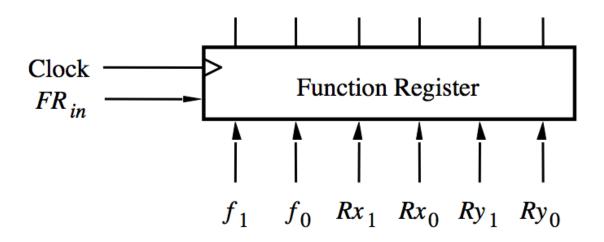

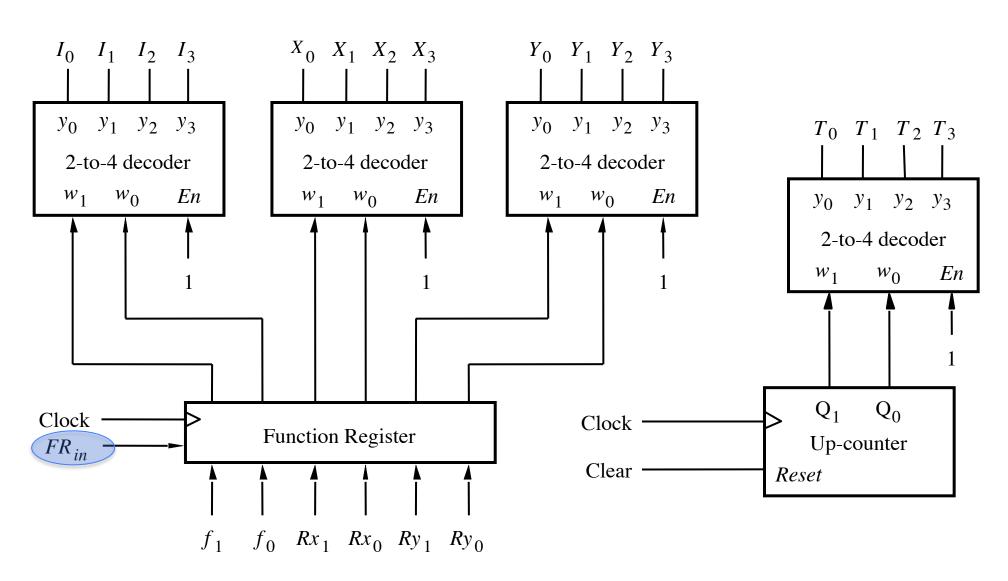

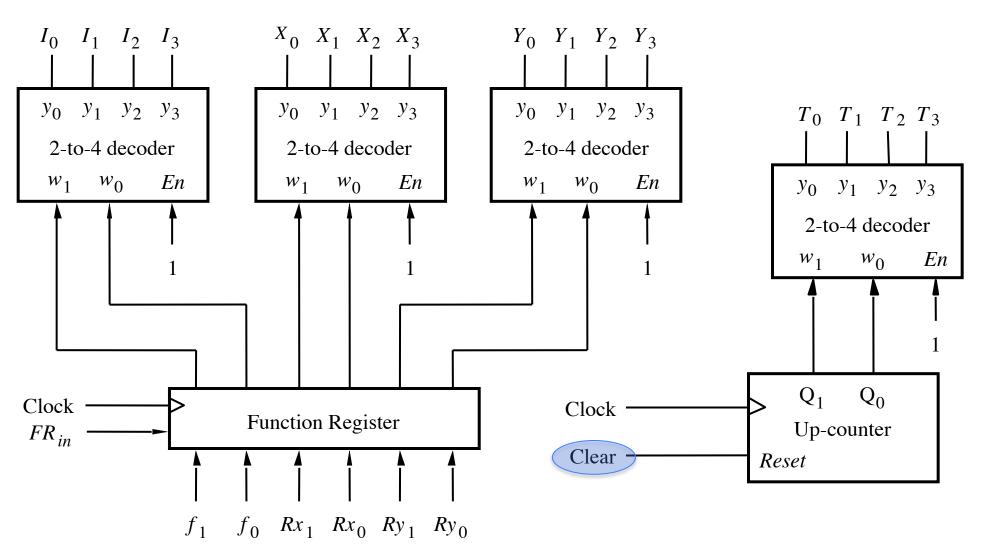

#### **Another Part of The Control Circuit**

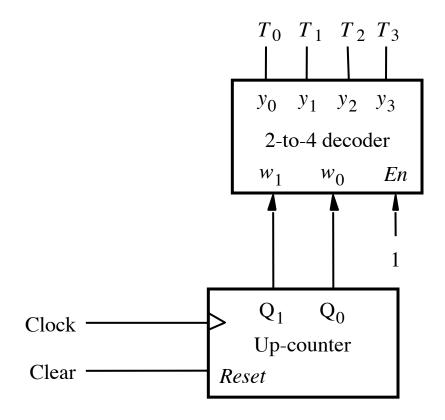

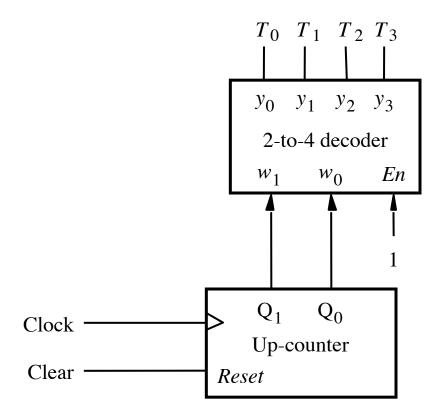

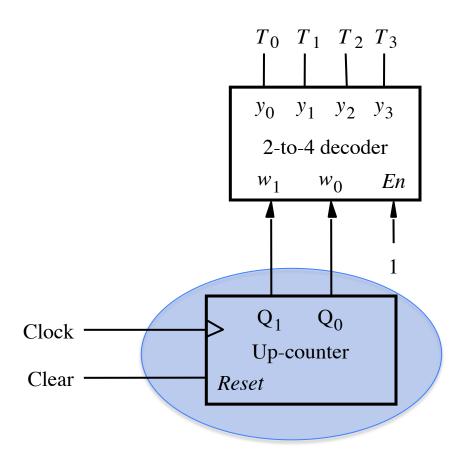

### A part of the control circuit for the processor

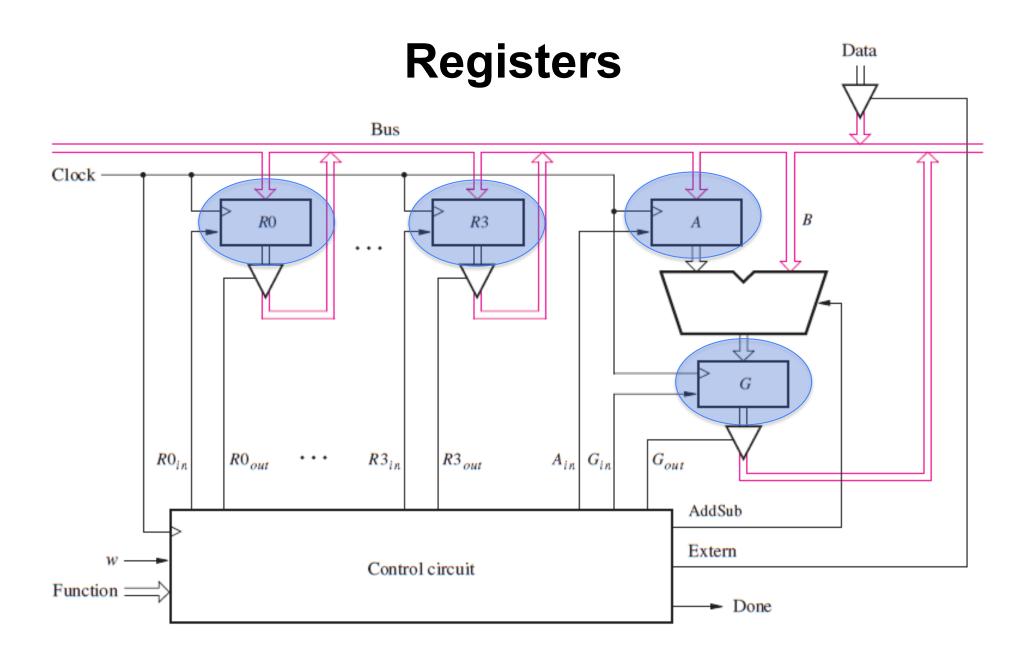

### What are the components?

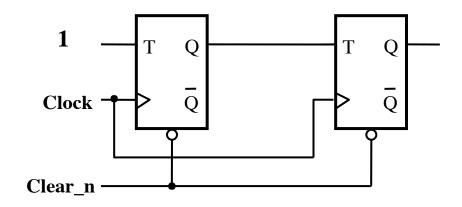

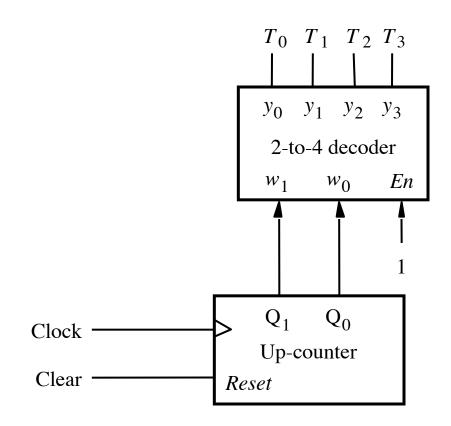

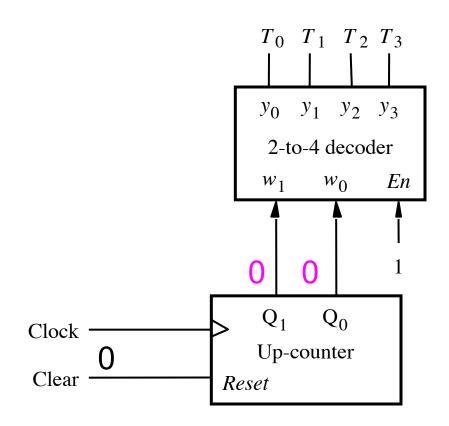

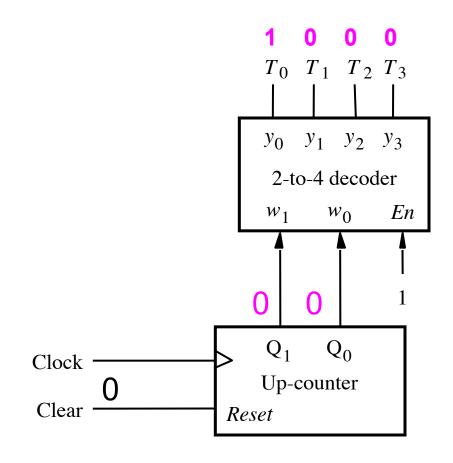

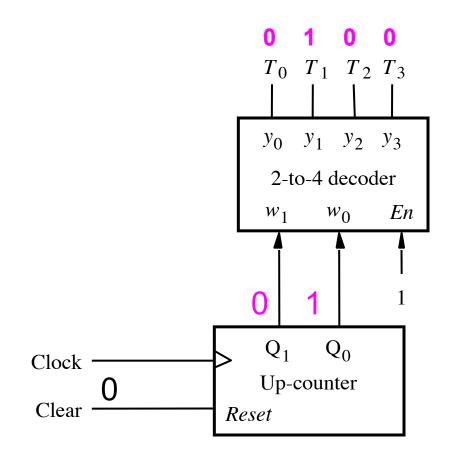

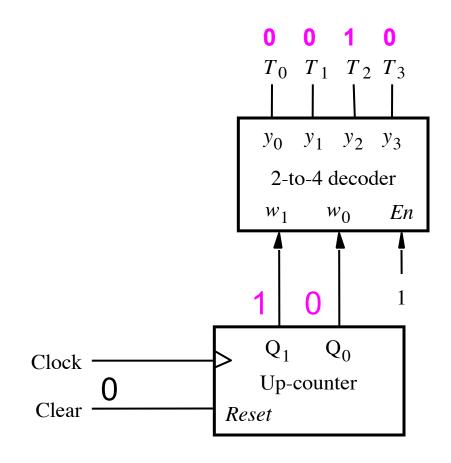

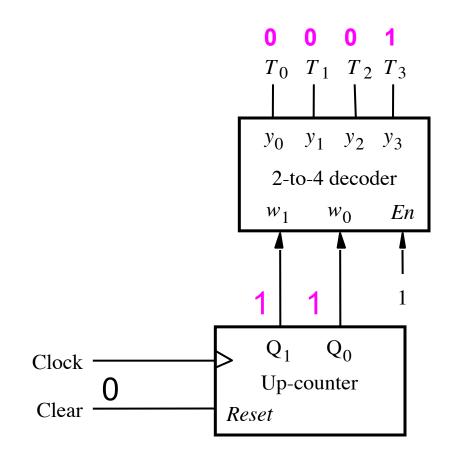

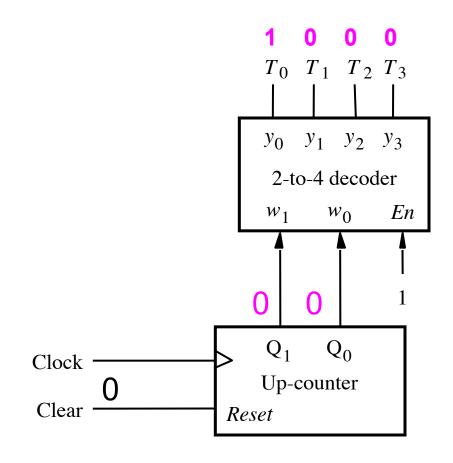

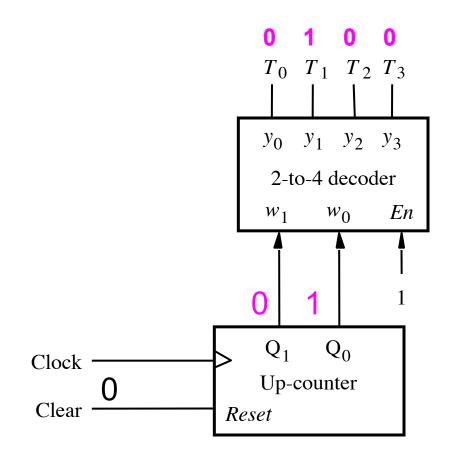

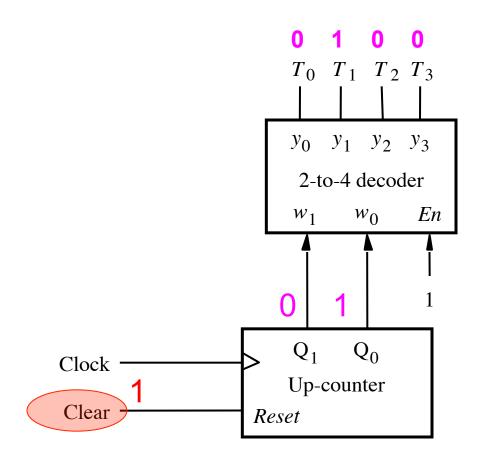

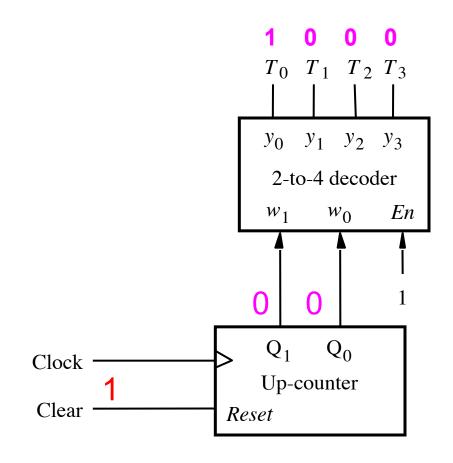

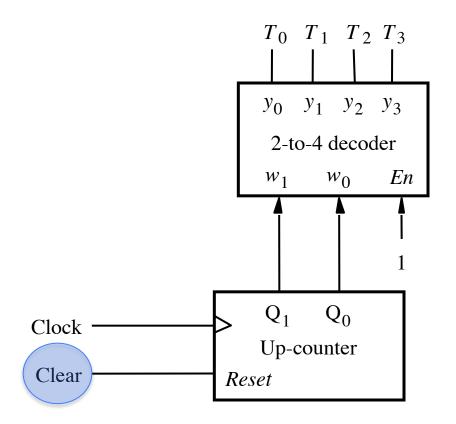

### 2-Bit Up-Counter

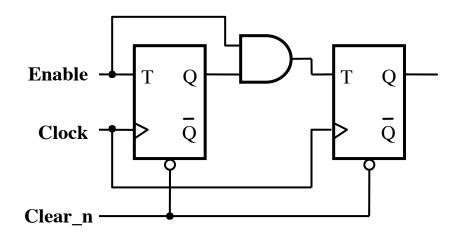

# 2-bit Synchronous Up-Counter

### 2-bit Synchronous Up-Counter with Enable

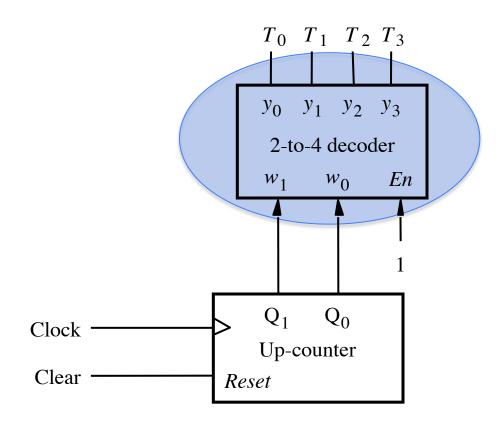

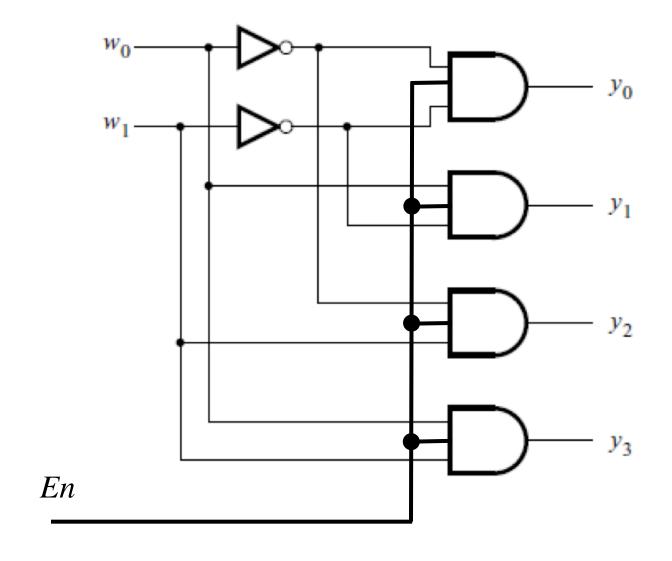

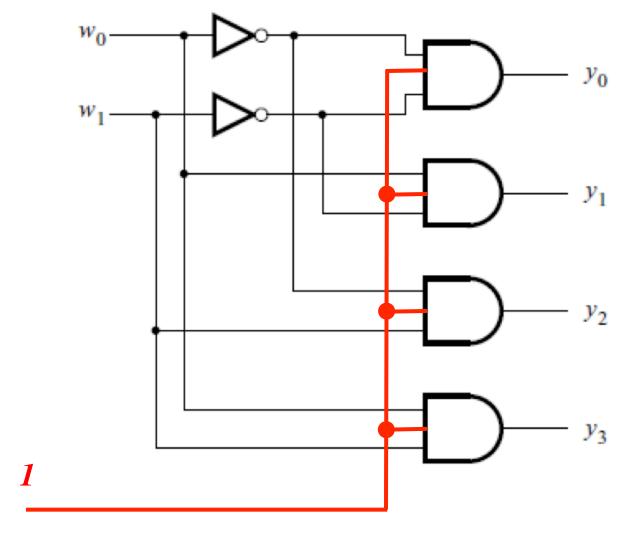

# 2-to-4 Decoder with Enable Input

# 2-to-4 Decoder with an Enable Input

# 2-to-4 Decoder with an Enable Input

(always enabled in this example)

# Meaning/Explanation

- This is like a FSM that cycles through its four states one after another.

- But it also can be reset to go to state 0 at any time.

- The implementation uses a counter followed by a decoder. The outputs of the decoder are one-hotencoded.

- This is like choosing a state assignment for an FSM in which there is one Flip-Flop per state, i.e., one-hot encoding (see Section 6.2.1 in the textbook)

# **Deriving the Control Signals**

# Design a FSM with input w and outputs

R0<sub>in</sub>

• A<sub>in</sub>

- AddSub

- T<sub>0</sub> • X<sub>0</sub>

R0<sub>out</sub>

Extern

Done

• X<sub>1</sub>

• X<sub>2</sub>

• R1<sub>in</sub>

• Gin

• T₁

• T<sub>2</sub>

R1<sub>out</sub>

• G<sub>out</sub>

- T<sub>3</sub>

- X<sub>3</sub>

• Y<sub>0</sub>

• Y<sub>1</sub>

• Y<sub>2</sub>

• Y<sub>3</sub>

R2<sub>in</sub>

Clear

- R2<sub>out</sub>

- R3<sub>in</sub>

- R3<sub>out</sub>

• FR<sub>in</sub>

- - These are helper outputs that are one-hot encoded. They are used to simplify the expressions for the other outputs.

[ Figure 7.9 from the textbook ]

### **Another Control Signal**

[ Figure 7.11 from the textbook ]

### **Yet Another Control Signal**

### **Expressing the 'FR<sub>in</sub>' signal**

$$FR_{in} = w T_0$$

Load a new operation into the function register

#### **Expressing the 'Clear' signal**

Clear =  $\overline{\mathbf{w}} \, \mathsf{T}_0 + \mathsf{Done}$

Reset the counter when Done or when w=0 and no operation is being executed (i.e.,  $T_0=1$ ).

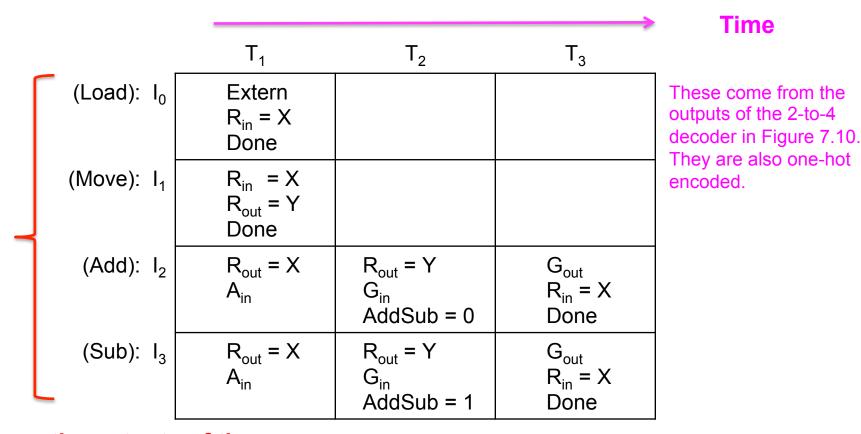

# Control signals asserted in each time step

|                        | T <sub>1</sub>                                      | $T_2$                             | T <sub>3</sub>                                  |

|------------------------|-----------------------------------------------------|-----------------------------------|-------------------------------------------------|

| (Load): I <sub>0</sub> | Extern<br>R <sub>in</sub> = X<br>Done               |                                   |                                                 |

| (Move): I <sub>1</sub> | R <sub>in</sub> = X<br>R <sub>out</sub> = Y<br>Done |                                   |                                                 |

| (Add): I <sub>2</sub>  | $R_{out} = X$ $A_{in}$                              | $R_{out} = Y$ $G_{in}$ AddSub = 0 | G <sub>out</sub><br>R <sub>in</sub> = X<br>Done |

| (Sub): I <sub>3</sub>  | $R_{out} = X$ $A_{in}$                              | $R_{out} = Y$ $G_{in}$ AddSub = 1 | G <sub>out</sub><br>R <sub>in</sub> = X<br>Done |

### Control signals asserted in each time step

These are the outputs of the first 2-to-4 decoder that is connected to the two most significant bits of the function register. They are one-hot encoded so only one of them is active at any given time (see Fig 7.11).

## The $I_0$ , $I_1$ , $I_2$ , $I_3$ and $T_0$ , $T_1$ , $T_2$ , $T_3$ Signals

[ Figure 7.11 from the textbook ]

### **Different Operations Take Different Amount of Time**

|                        | T <sub>1</sub>                                      | $T_2$                             | $T_3$                                           | _              |

|------------------------|-----------------------------------------------------|-----------------------------------|-------------------------------------------------|----------------|

| (Load): I <sub>0</sub> | Extern<br>R <sub>in</sub> = X<br>Done               |                                   |                                                 | 1 clock cycle  |

| (Move): I <sub>1</sub> | R <sub>in</sub> = X<br>R <sub>out</sub> = Y<br>Done |                                   |                                                 | 1 clock cycle  |

| (Add): I <sub>2</sub>  | $R_{out} = X$ $A_{in}$                              | $R_{out} = Y$ $G_{in}$ AddSub = 0 | G <sub>out</sub><br>R <sub>in</sub> = X<br>Done | 3 clock cycles |

| (Sub): I <sub>3</sub>  | $R_{out} = X$ $A_{in}$                              | $R_{out} = Y$ $G_{in}$ AddSub = 1 | G <sub>out</sub><br>R <sub>in</sub> = X<br>Done | 3 clock cycles |

### **Expressing the 'Extern' signal**

|                        | T <sub>1</sub>                        | $T_2$                             | T <sub>3</sub>                                  |

|------------------------|---------------------------------------|-----------------------------------|-------------------------------------------------|

| (Load): I <sub>0</sub> | Extern<br>R <sub>in</sub> = X<br>Done |                                   |                                                 |

| (Move): I <sub>1</sub> | $R_{in} = X$ $R_{out} = Y$ Done       |                                   |                                                 |

| (Add): I <sub>2</sub>  | $R_{out} = X$ $A_{in}$                | $R_{out} = Y$ $G_{in}$ AddSub = 0 | G <sub>out</sub><br>R <sub>in</sub> = X<br>Done |

| (Sub): I <sub>3</sub>  | $R_{out} = X$ $A_{in}$                | $R_{out} = Y$ $G_{in}$ AddSub = 1 | G <sub>out</sub><br>R <sub>in</sub> = X<br>Done |

Extern =

$$I_0 T_1$$

### **Expressing the 'Done' signal**

|                        | T <sub>1</sub>                  | $T_2$                             | T <sub>3</sub>                                  |

|------------------------|---------------------------------|-----------------------------------|-------------------------------------------------|

| (Load): I <sub>0</sub> | Extern R <sub>in</sub> = X Done |                                   |                                                 |

| (Move): I <sub>1</sub> | $R_{in} = X$ $R_{out} = Y$ Done |                                   |                                                 |

| (Add): I <sub>2</sub>  | $R_{out} = X$ $A_{in}$          | $R_{out} = Y$ $G_{in}$ AddSub = 0 | G <sub>out</sub><br>R <sub>in</sub> = X<br>Done |

| (Sub): I <sub>3</sub>  | $R_{out} = X$ $A_{in}$          | $R_{out} = Y$ $G_{in}$ AddSub = 1 | $G_{out}$ $R_{in} = X$ Done                     |

Done =

$$(I_0 + I_1)T_1 + (I_2 + I_3)T_3$$

# Expressing the 'A<sub>in</sub>' signal

|                        | T <sub>1</sub>                                      | $T_2$                             | T <sub>3</sub>                                  |

|------------------------|-----------------------------------------------------|-----------------------------------|-------------------------------------------------|

| (Load): I <sub>0</sub> | Extern<br>R <sub>in</sub> = X<br>Done               |                                   |                                                 |

| (Move): I <sub>1</sub> | R <sub>in</sub> = X<br>R <sub>out</sub> = Y<br>Done |                                   |                                                 |

| (Add): I <sub>2</sub>  | $R_{out} = X$ $A_{in}$                              | $R_{out} = Y$ $G_{in}$ AddSub = 0 | G <sub>out</sub><br>R <sub>in</sub> = X<br>Done |

| (Sub): I <sub>3</sub>  | $R_{out} = X$ $A_{in}$                              | $R_{out} = Y$ $G_{in}$ AddSub = 1 | G <sub>out</sub><br>R <sub>in</sub> = X<br>Done |

$$A_{in} = (I_2 + I_3)T_1$$

# Expressing the 'G<sub>in</sub>' signal

|                        | T <sub>1</sub>                                      | $T_2$                             | T <sub>3</sub>                                  |

|------------------------|-----------------------------------------------------|-----------------------------------|-------------------------------------------------|

| (Load): I <sub>0</sub> | Extern<br>R <sub>in</sub> = X<br>Done               |                                   |                                                 |

| (Move): I <sub>1</sub> | R <sub>in</sub> = X<br>R <sub>out</sub> = Y<br>Done |                                   |                                                 |

| (Add): I <sub>2</sub>  | $R_{out} = X$ $A_{in}$                              | $R_{out} = Y$ $G_{in}$ AddSub = 0 | G <sub>out</sub><br>R <sub>in</sub> = X<br>Done |

| (Sub): I <sub>3</sub>  | $R_{out} = X$ $A_{in}$                              | $R_{out} = Y$ $G_{in}$ AddSub = 1 | G <sub>out</sub><br>R <sub>in</sub> = X<br>Done |

$$G_{in} = (I_2 + I_3)T_2$$

# Expressing the 'Gout' signal

|                        | T <sub>1</sub>                        | $T_2$                             | $T_3$                                           |

|------------------------|---------------------------------------|-----------------------------------|-------------------------------------------------|

| (Load): I <sub>0</sub> | Extern<br>R <sub>in</sub> = X<br>Done |                                   |                                                 |

| (Move): I <sub>1</sub> | $R_{in} = X$ $R_{out} = Y$ Done       |                                   |                                                 |

| (Add): I <sub>2</sub>  | $R_{out} = X$ $A_{in}$                | $R_{out} = Y$ $G_{in}$ AddSub = 0 | $G_{out}$ $R_{in} = X$ Done                     |

| (Sub): I <sub>3</sub>  | $R_{out} = X$ $A_{in}$                | $R_{out} = Y$ $G_{in}$ AddSub = 1 | G <sub>out</sub><br>R <sub>in</sub> = X<br>Done |

$$G_{out} = (I_2 + I_3)T_3$$

## **Expressing the 'AddSub' signal**

|                        | T <sub>1</sub>                                      | $T_2$                             | T <sub>3</sub>                                  |

|------------------------|-----------------------------------------------------|-----------------------------------|-------------------------------------------------|

| (Load): I <sub>0</sub> | Extern<br>R <sub>in</sub> = X<br>Done               |                                   |                                                 |

| (Move): I <sub>1</sub> | R <sub>in</sub> = X<br>R <sub>out</sub> = Y<br>Done |                                   |                                                 |

| (Add): I <sub>2</sub>  | $R_{out} = X$ $A_{in}$                              | $R_{out} = Y$ $G_{in}$ AddSub = 0 | G <sub>out</sub><br>R <sub>in</sub> = X<br>Done |

| (Sub): I <sub>3</sub>  | $R_{out} = X$ $A_{in}$                              | $R_{out} = Y$ $G_{in}$ AddSub = 1 | G <sub>out</sub><br>R <sub>in</sub> = X<br>Done |

AddSub =  $I_3$

# Expressing the 'R0<sub>in</sub>' signal

|                        | T <sub>1</sub>                    | $T_2$                             | T <sub>3</sub>                                  |

|------------------------|-----------------------------------|-----------------------------------|-------------------------------------------------|

| (Load): I <sub>0</sub> | Extern  R <sub>in</sub> = X  Done |                                   |                                                 |

| (Move): I <sub>1</sub> | $R_{in} = X$ $R_{out} = Y$ Done   |                                   |                                                 |

| (Add): I <sub>2</sub>  | $R_{out} = X$ $A_{in}$            | $R_{out} = Y$ $G_{in}$ AddSub = 0 | G <sub>out</sub><br>R <sub>in</sub> ∓ X<br>Done |

| (Sub): I <sub>3</sub>  | $R_{out} = X$ $A_{in}$            | $R_{out} = Y$ $G_{in}$ AddSub = 1 | G <sub>out</sub> R <sub>in</sub> = X Done       |

$$R0_{in} = (I_0 + I_1)T_1X_0 + (I_2 + I_3)T_3X_0$$

## **Expressing the 'R1<sub>in</sub>' signal**

|                        | T <sub>1</sub>                    | $T_2$                             | T <sub>3</sub>                            |

|------------------------|-----------------------------------|-----------------------------------|-------------------------------------------|

| (Load): I <sub>0</sub> | Extern  R <sub>in</sub> = X  Done |                                   |                                           |

| (Move): I <sub>1</sub> | $R_{in} = X$ $R_{out} = Y$ Done   |                                   |                                           |

| (Add): I <sub>2</sub>  | $R_{out} = X$ $A_{in}$            | $R_{out} = Y$ $G_{in}$ AddSub = 0 | G <sub>out</sub> R <sub>in</sub> ∓ X Done |

| (Sub): I <sub>3</sub>  | $R_{out} = X$ $A_{in}$            | $R_{out} = Y$ $G_{in}$ AddSub = 1 | G <sub>out</sub> R <sub>in</sub> = X Done |

$$R1_{in} = (I_0 + I_1)T_1X_1 + (I_2 + I_3)T_3X_1$$

## **Expressing the 'R2<sub>in</sub>' signal**

|                        | T <sub>1</sub>                    | $T_2$                             | T <sub>3</sub>                                  |

|------------------------|-----------------------------------|-----------------------------------|-------------------------------------------------|

| (Load): I <sub>0</sub> | Extern  R <sub>in</sub> = X  Done |                                   |                                                 |

| (Move): I <sub>1</sub> | $R_{in} = X$ $R_{out} = Y$ Done   |                                   |                                                 |

| (Add): I <sub>2</sub>  | $R_{out} = X$ $A_{in}$            | $R_{out} = Y$ $G_{in}$ AddSub = 0 | G <sub>out</sub><br>R <sub>in</sub> ∓ X<br>Done |

| (Sub): I <sub>3</sub>  | $R_{out} = X$ $A_{in}$            | $R_{out} = Y$ $G_{in}$ AddSub = 1 | G <sub>out</sub> R <sub>in</sub> = X Done       |

$$R_{in}^2 = (I_0 + I_1)T_1X_2 + (I_2 + I_3)T_3X_2$$

## **Expressing the 'R3<sub>in</sub>' signal**

|                        | T <sub>1</sub>                    | $T_2$                             | T <sub>3</sub>                            |

|------------------------|-----------------------------------|-----------------------------------|-------------------------------------------|

| (Load): I <sub>0</sub> | Extern  R <sub>in</sub> = X  Done |                                   |                                           |

| (Move): I <sub>1</sub> | $R_{in} = X$ $R_{out} = Y$ Done   |                                   |                                           |

| (Add): I <sub>2</sub>  | $R_{out} = X$ $A_{in}$            | $R_{out} = Y$ $G_{in}$ AddSub = 0 | G <sub>out</sub> R <sub>in</sub> ∓ X Done |

| (Sub): I <sub>3</sub>  | $R_{out} = X$ $A_{in}$            | $R_{out} = Y$ $G_{in}$ AddSub = 1 | G <sub>out</sub> R <sub>in</sub> = X Done |

$$R_{in}^3 = (I_0 + I_1)T_1X_3 + (I_2 + I_3)T_3X_3$$

## **Expressing the 'R0<sub>out</sub>' signal**

|                        | T <sub>1</sub>                        | $T_2$                             | T <sub>3</sub>                                  |

|------------------------|---------------------------------------|-----------------------------------|-------------------------------------------------|

| (Load): I <sub>0</sub> | Extern<br>R <sub>in</sub> = X<br>Done |                                   |                                                 |

| (Move): I <sub>1</sub> | $R_{in} = X$ $R_{out} = Y$ Done       |                                   |                                                 |

| (Add): I <sub>2</sub>  | $R_{out} = X$ $A_{in}$                | $R_{out} = Y$ $G_{in}$ AddSub = 0 | G <sub>out</sub><br>R <sub>in</sub> = X<br>Done |

| (Sub): I <sub>3</sub>  | $R_{out} = X$ $A_{in}$                | $R_{out} = Y$ $G_{in}$ AddSub = 1 | G <sub>out</sub><br>R <sub>in</sub> = X<br>Done |

$$R0_{out} = I_1T_1Y_0 + (I_2 + I_3) (T_1X_0 + T_2Y_0)$$

## **Expressing the 'R1<sub>out</sub>' signal**

|                        | T <sub>1</sub>                        | $T_2$                             | T <sub>3</sub>                                  |

|------------------------|---------------------------------------|-----------------------------------|-------------------------------------------------|

| (Load): I <sub>0</sub> | Extern<br>R <sub>in</sub> = X<br>Done |                                   |                                                 |

| (Move): I <sub>1</sub> | $R_{in} = X$ $R_{out} = Y$ Done       |                                   |                                                 |

| (Add): I <sub>2</sub>  | $R_{out} = X$ $A_{in}$                | $R_{out} = Y$ $G_{in}$ AddSub = 0 | G <sub>out</sub><br>R <sub>in</sub> = X<br>Done |

| (Sub): I <sub>3</sub>  | $R_{out} = X$ $A_{in}$                | $R_{out} = Y$ $G_{in}$ AddSub = 1 | G <sub>out</sub><br>R <sub>in</sub> = X<br>Done |

$$R_{out}^1 = I_1 T_1 Y_1 + (I_2 + I_3) (T_1 X_1 + T_2 Y_1)$$

## **Expressing the 'R2<sub>out</sub>' signal**

|                        | T <sub>1</sub>                        | $T_2$                             | T <sub>3</sub>                                  |

|------------------------|---------------------------------------|-----------------------------------|-------------------------------------------------|

| (Load): I <sub>0</sub> | Extern<br>R <sub>in</sub> = X<br>Done |                                   |                                                 |

| (Move): I <sub>1</sub> | $R_{in} = X$ $R_{out} = Y$ Done       |                                   |                                                 |

| (Add): I <sub>2</sub>  | $R_{out} = X$ $A_{in}$                | $R_{out} = Y$ $G_{in}$ AddSub = 0 | G <sub>out</sub><br>R <sub>in</sub> = X<br>Done |

| (Sub): I <sub>3</sub>  | $R_{out} = X$ $A_{in}$                | $R_{out} = Y$ $G_{in}$ AddSub = 1 | G <sub>out</sub><br>R <sub>in</sub> = X<br>Done |

$$R_{out}^2 = I_1 T_1 Y_2 + (I_2 + I_3) (T_1 X_2 + T_2 Y_2)$$

# **Expressing the 'R3<sub>out</sub>' signal**

|                        | T <sub>1</sub>                        | $T_2$                             | T <sub>3</sub>                                  |

|------------------------|---------------------------------------|-----------------------------------|-------------------------------------------------|

| (Load): I <sub>0</sub> | Extern<br>R <sub>in</sub> = X<br>Done |                                   |                                                 |

| (Move): I <sub>1</sub> | $R_{in} = X$ $R_{out} = Y$ Done       |                                   |                                                 |

| (Add): I <sub>2</sub>  | $R_{out} = X$ $A_{in}$                | $R_{out} = Y$ $G_{in}$ AddSub = 0 | G <sub>out</sub><br>R <sub>in</sub> = X<br>Done |

| (Sub): I <sub>3</sub>  | $R_{out} = X$ $A_{in}$                | $R_{out} = Y$ $G_{in}$ AddSub = 1 | G <sub>out</sub><br>R <sub>in</sub> = X<br>Done |

$$R_{out}^3 = I_1 T_1 Y_3 + (I_2 + I_3) (T_1 X_3 + T_2 Y_3)$$

# **Derivation of the Control Inputs**

For more insights into these derivations see pages 434 and 435 in the textbook

# **Some Additional Topics**

## The ALU for the Simple Processor

[ Figure 7.9 from the textbook ]

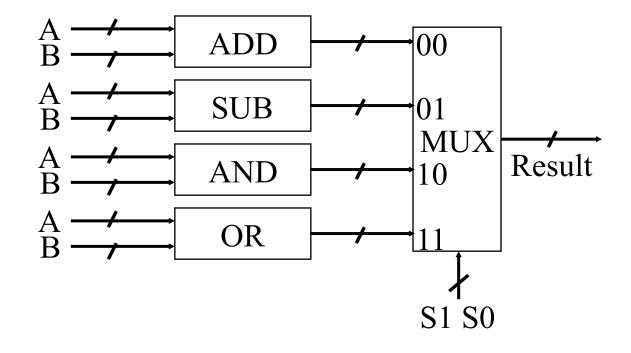

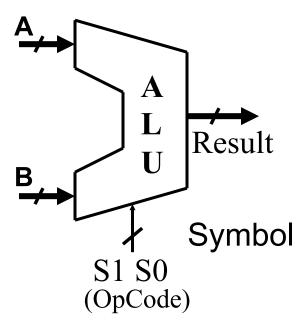

## **Another Arithmetic Logic Unit (ALU)**

- Arithmetic Logic Unit (ALU) computes arithmetic or logic functions

- Example: A four-function ALU has two selection bits S1 S0 (also called OpCode) to specify the function

- 00 (ADD), 01 (SUB), 10 (AND), 11 (OR)

- Then the following set up will work

| <b>S1</b> | S0 | Function |

|-----------|----|----------|

| 0         | 0  | ADD      |

| 0         | 1  | SUB      |

| 1         | 0  | AND      |

| 1         | 1  | OR       |

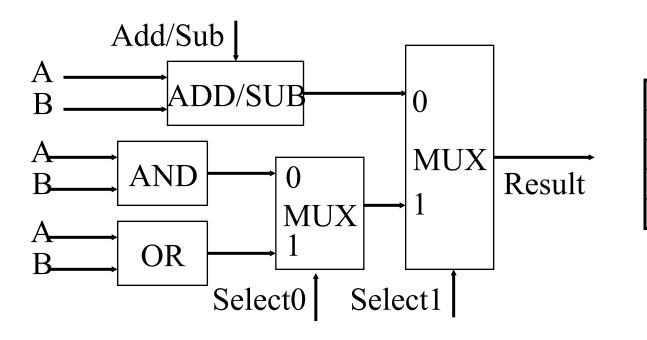

#### An Alternative Design of Four-Function ALU

- The previous design is not very efficient as it uses an adder and a subtractor circuit

- We can design an add/subtract unit as discussed earlier

- Then we can design a logical unit (AND and OR) separately

- Then select appropriate output as result

- What are the control signals, Add/Sub, Select0, and Select1?

| <b>S1</b> | S0 | Function |

|-----------|----|----------|

| 0         | 0  | ADD      |

| 0         | 1  | SUB      |

| 1         | 0  | AND      |

| 1         | 1  | OR       |

# **Examples of Some Famous Microprocessors**

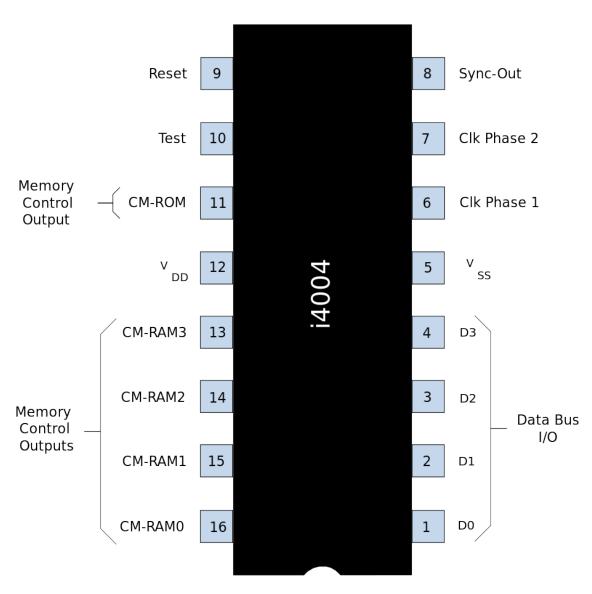

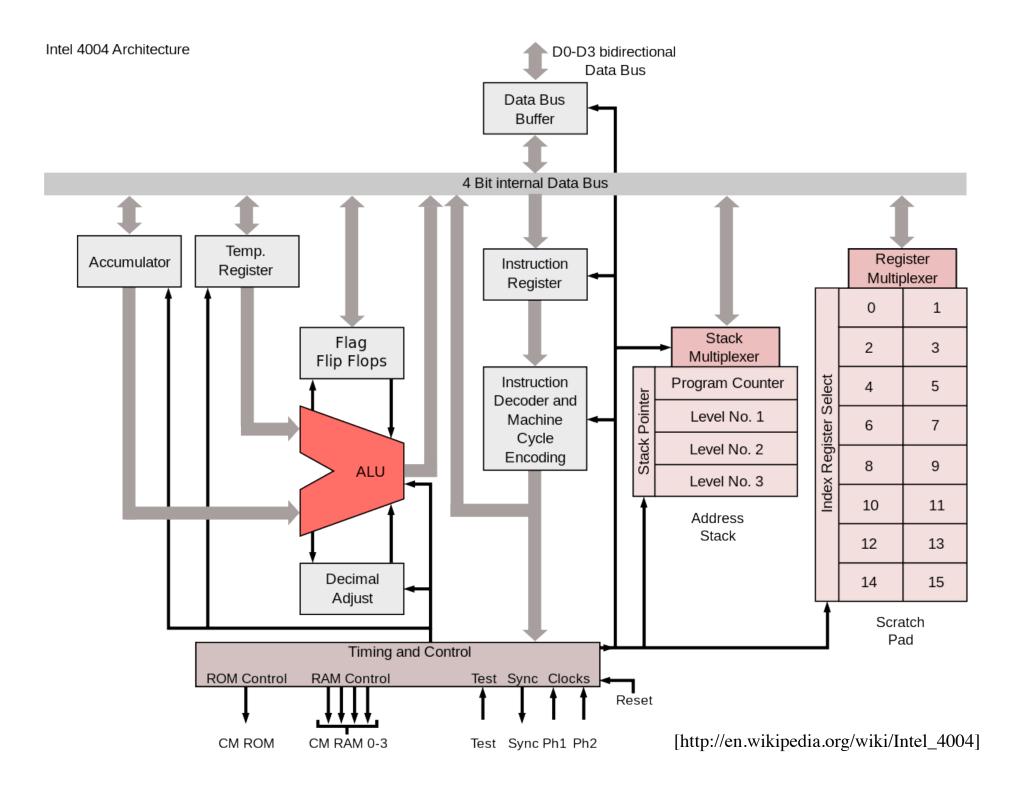

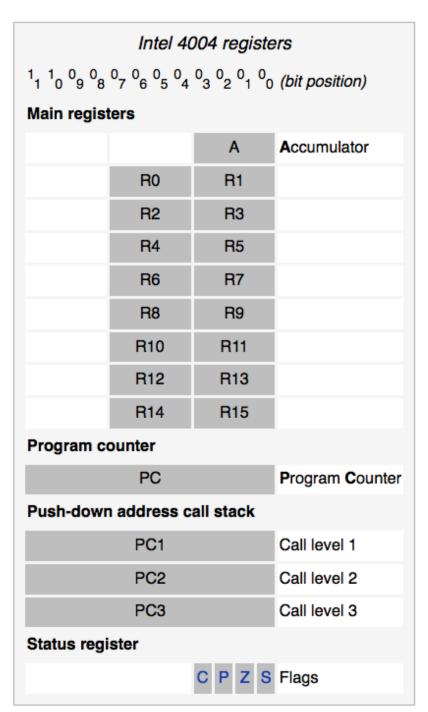

# Intel's 4004 Chip

# **Technical specifications**

- Maximum clock speed was 740 kHz

- Instruction cycle time: 10.8 µs

(8 clock cycles / instruction cycle)

- Instruction execution time 1 or 2 instruction cycles (10.8 or 21.6 µs), 46300 to 92600 instructions per second

- Built using 2,300 transistors

# **Technical specifications**

- Separate program and data storage.

- The 4004, with its need to keep pin count down, used a single multiplexed 4-bit bus for transferring:

- 12-bit addresses

- 8-bit instructions

- 4-bit data words

- Instruction set contained 46 instructions (of which 41 were 8 bits wide and 5 were 16 bits wide)

- Register set contained 16 registers of 4 bits each

- Internal subroutine stack, 3 levels deep.

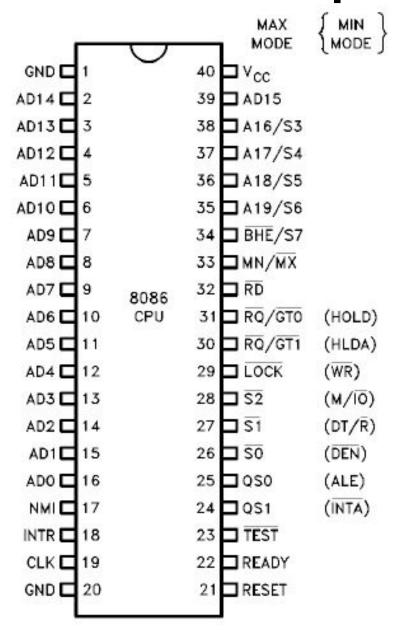

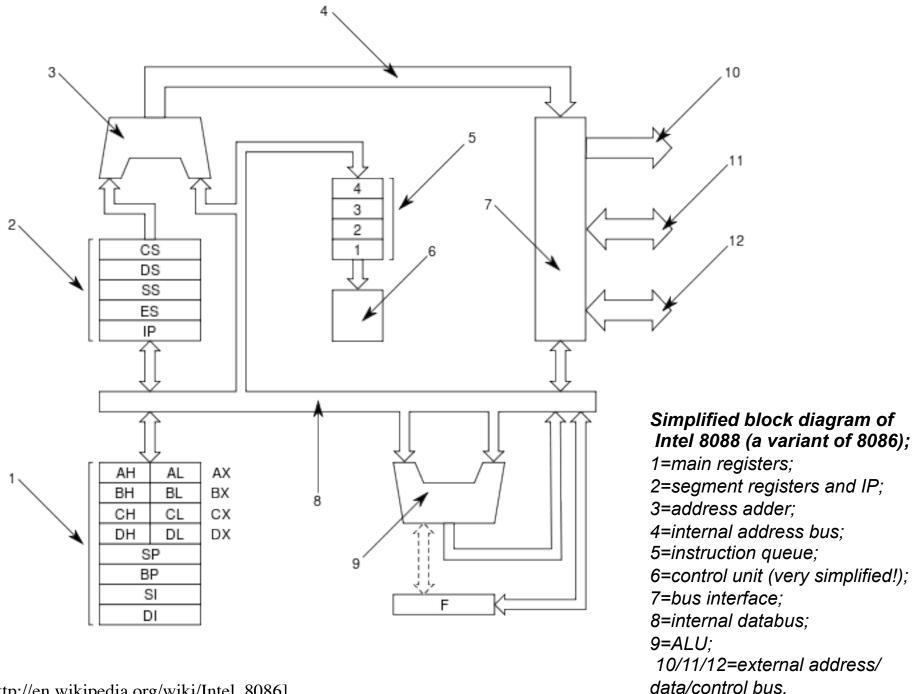

## Intel's 8086 Chip

|                                                             |                                                                                                                           | Intel 8086 i                                                               | registers                                                   |                                   |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------|

| <sup>1</sup> 9 <sup>1</sup> 8 <sup>1</sup> 7 <sup>1</sup> 6 | 3 <sup>1</sup> 5 <sup>1</sup> 4 <sup>1</sup> 3 <sup>1</sup> 2 <sup>1</sup> 1 <sup>1</sup> 0 <sup>0</sup> 9 <sup>0</sup> 8 | 3 <sup>0</sup> 7 <sup>0</sup> 6 <sup>0</sup> 5 <sup>0</sup> 4 <sup>0</sup> | 0 <sub>3</sub> 0 <sub>2</sub> 0 <sub>1</sub> 0 <sub>0</sub> | (bit position)                    |

| Main regis                                                  | ters                                                                                                                      |                                                                            |                                                             |                                   |

|                                                             | AH                                                                                                                        | AL                                                                         | -                                                           | AX (primary accumulator)          |

|                                                             | ВН                                                                                                                        | BL                                                                         | -                                                           | BX (base, accumulator)            |

|                                                             | СН                                                                                                                        | Cl                                                                         | _                                                           | CX (counter, accumulator)         |

|                                                             | DH                                                                                                                        | DI                                                                         | L                                                           | DX (accumulator, other functions) |

| Index regi                                                  | sters                                                                                                                     |                                                                            |                                                             |                                   |

| 0000                                                        | :                                                                                                                         | SI                                                                         |                                                             | Source Index                      |

| 0000                                                        |                                                                                                                           | DI                                                                         |                                                             | Destination Index                 |

| 0000                                                        | E                                                                                                                         | 3P                                                                         |                                                             | Base Pointer                      |

| 0000                                                        | 5                                                                                                                         | SP                                                                         |                                                             | Stack Pointer                     |

| Program o                                                   | ounter                                                                                                                    |                                                                            |                                                             |                                   |

| 0000                                                        |                                                                                                                           | IP                                                                         |                                                             | Instruction Pointer               |

| Segment r                                                   | egisters                                                                                                                  |                                                                            |                                                             |                                   |

|                                                             | CS                                                                                                                        |                                                                            | 0000                                                        | Code Segment                      |

|                                                             | DS                                                                                                                        |                                                                            | 0000                                                        | Data Segment                      |

|                                                             | ES                                                                                                                        |                                                                            | 0000                                                        | ExtraSegment                      |

|                                                             | SS                                                                                                                        |                                                                            | 0000                                                        | Stack Segment                     |

| Status reg                                                  | ister                                                                                                                     |                                                                            |                                                             |                                   |

|                                                             | O D I T                                                                                                                   | SZ-A                                                                       | - P - C                                                     | Flags [http://en.wikipedia.org/w  |

[http://en.wikipedia.org/wiki/Intel\_8086]

**Questions?**

# THE END