# **CprE 281: Digital Logic**

**Instructor: Alexander Stoytchev**

http://www.ece.iastate.edu/~alexs/classes/

### **Code Converters**

CprE 281: Digital Logic Iowa State University, Ames, IA Copyright © Alexander Stoytchev

#### **Administrative Stuff**

• HW 7 is out

It is due next Monday (Oct 17) @ 4pm

#### **Administrative Stuff**

The second midterm is in 2 weeks.

#### **Administrative Stuff**

- Midterm Exam #2

- When: Friday October 28 @ 4pm.

- Where: This classroom

- What: Chapters 1, 2, 3, 4 and 5.1-5.8

- The exam will be open book and open notes (you can bring up to 3 pages of handwritten/typed notes).

#### Midterm 2: Format

- The exam will be out of 130 points

- You need 95 points to get an A

- It will be great if you can score more than 100 points.

- but you can't roll over your extra points ⊗

# **Quick Review**

## **Decoders**

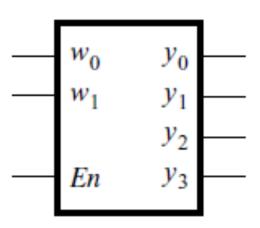

## 2-to-4 Decoder (Definition)

- Has two inputs: w<sub>1</sub> and w<sub>0</sub>

- Has four outputs: y<sub>0</sub>, y<sub>1</sub>, y<sub>2</sub>, and y<sub>3</sub>

- If  $w_1=0$  and  $w_0=0$ , then the output  $y_0$  is set to 1

- If  $w_1=0$  and  $w_0=1$ , then the output  $y_1$  is set to 1

- If  $w_1=1$  and  $w_0=0$ , then the output  $y_2$  is set to 1

- If w<sub>1</sub>=1 and w<sub>0</sub>=1, then the output y<sub>3</sub> is set to 1

- Only one output is set to 1. All others are set to 0.

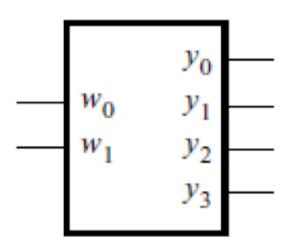

# Truth Table and Graphical Symbol for a 2-to-4 Decoder

| $w_1$ | $w_0$ | $y_0$ | $y_1$ | $y_2$ | $y_3$ |

|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 1     | 0     | 0     | 0     |

| 0     | 1     | 0     | 1     | 0     | 0     |

| 1     | 0     | 0     | 0     | 1     | 0     |

| 1     | 1     | 0     | 0     | 0     | 1     |

|       |       |       |       |       |       |

(a) Truth table

(b) Graphical symbol

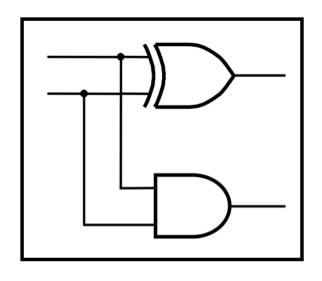

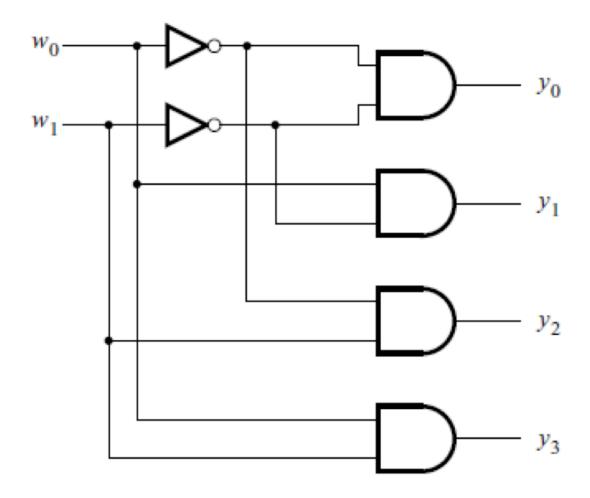

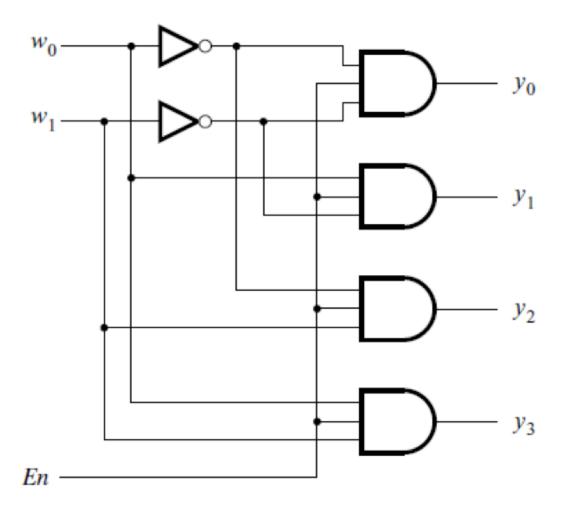

# Truth Logic Circuit for a 2-to-4 Decoder

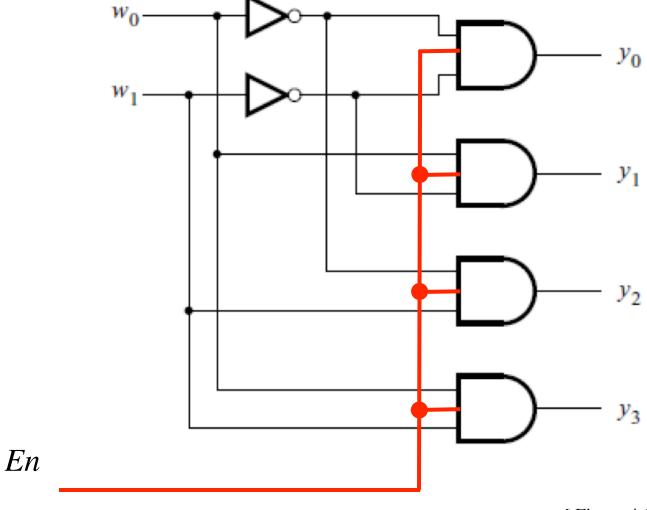

# Adding an Enable Input

[ Figure 4.13c from the textbook ]

# Truth Table and Graphical Symbol for a 2-to-4 Decoder with an Enable Input

| En | $w_1$ | $w_0$ | $y_0$ | $y_1$ | $y_2$ | $y_3$ |

|----|-------|-------|-------|-------|-------|-------|

| 1  | 0     | 0     | 1     | 0     | 0     | 0     |

| 1  | 0     | 1     | 0     | 1     | 0     | 0     |

| 1  | 1     | 0     | 0     | 0     | 1     | 0     |

| 1  | 1     | 1     | 0     | 0     | 0     | 1     |

| 0  | X     | X     | 0     | 0     | 0     | 0     |

(a) Truth table

(b) Graphical symbol

# Truth Table and Graphical Symbol for a 2-to-4 Decoder with an Enable Input

| En              | $w_1$ | $w_0$ | $y_0$ | $y_1$ | $y_2$ | $y_3$ |  |

|-----------------|-------|-------|-------|-------|-------|-------|--|

| 1               | 0     | 0     | 1     | 0     | 0     | 0     |  |

| 1               | 0     | 1     | 0     | 1     | 0     | 0     |  |

| 1               | 1     | 0     | 0     | 0     | 1     | 0     |  |

| 1               | 1     | 1     | 0     | 0     | 0     | 1     |  |

| 0               | Х     | Х     | 0     | 0     | 0     | 0     |  |

| (a) Truth table |       |       |       |       |       |       |  |

x indicates that it does not matter what the value of these variable is for this row of the truth table

(b) Graphical symbol

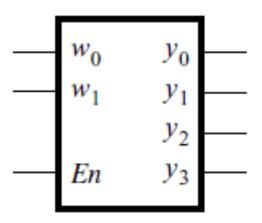

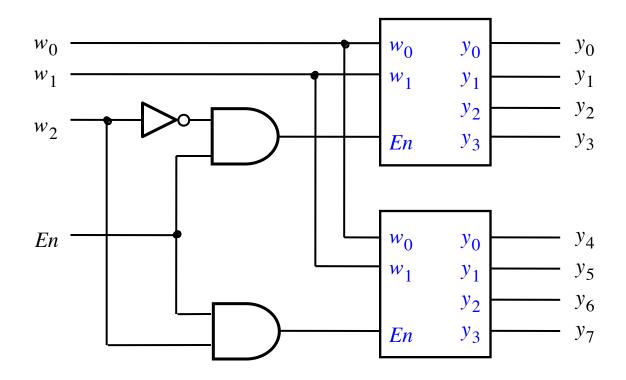

# Graphical Symbol for a Binary n-to-2<sup>n</sup> Decoder with an Enable Input

(d) An n-to-2<sup>n</sup> decoder

A binary decoder with n inputs has 2<sup>n</sup> outputs

The outputs of an enabled binary decoder are "one-hot" encoded, meaning that only a single bit is set to 1, i.e., it is *hot*.

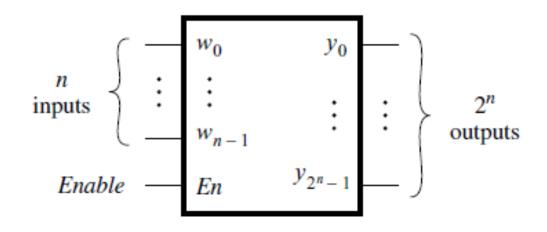

#### A 3-to-8 decoder using two 2-to-4 decoders

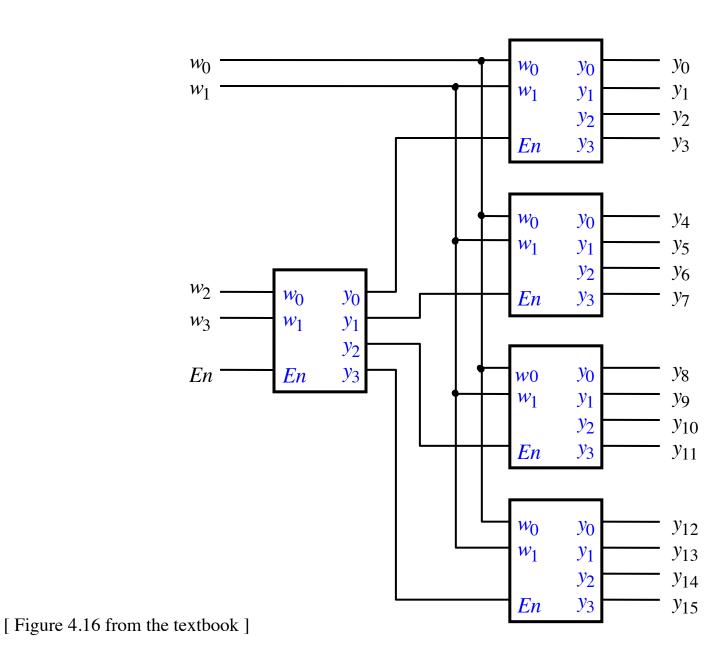

#### A 4-to-16 decoder built using a decoder tree

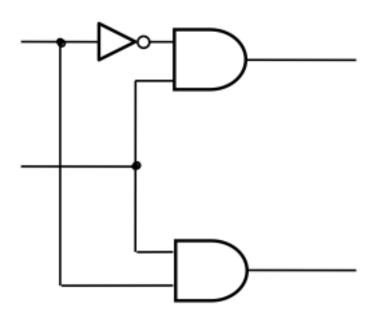

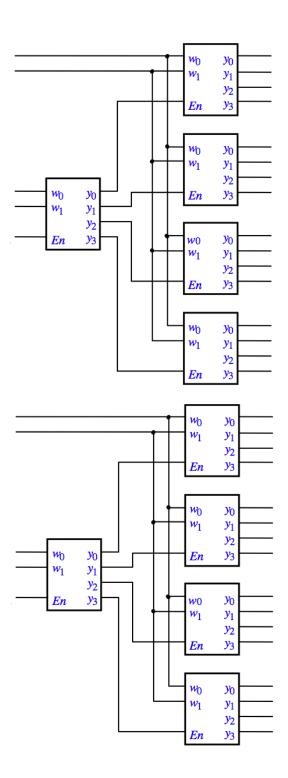

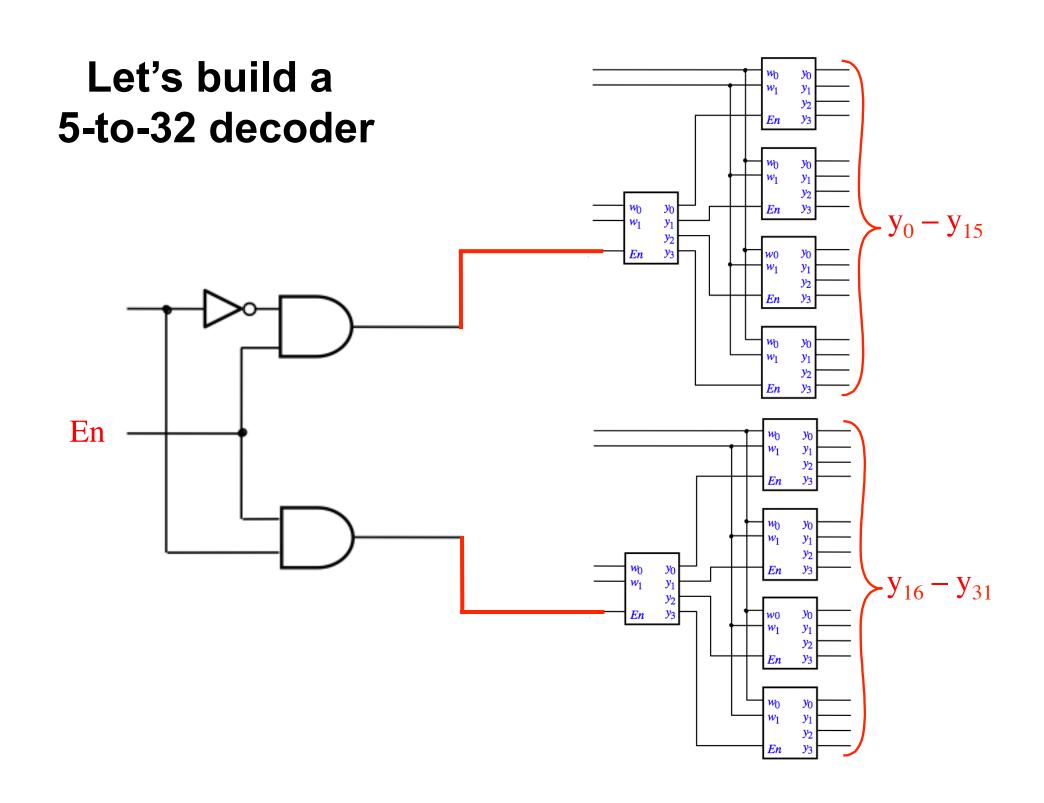

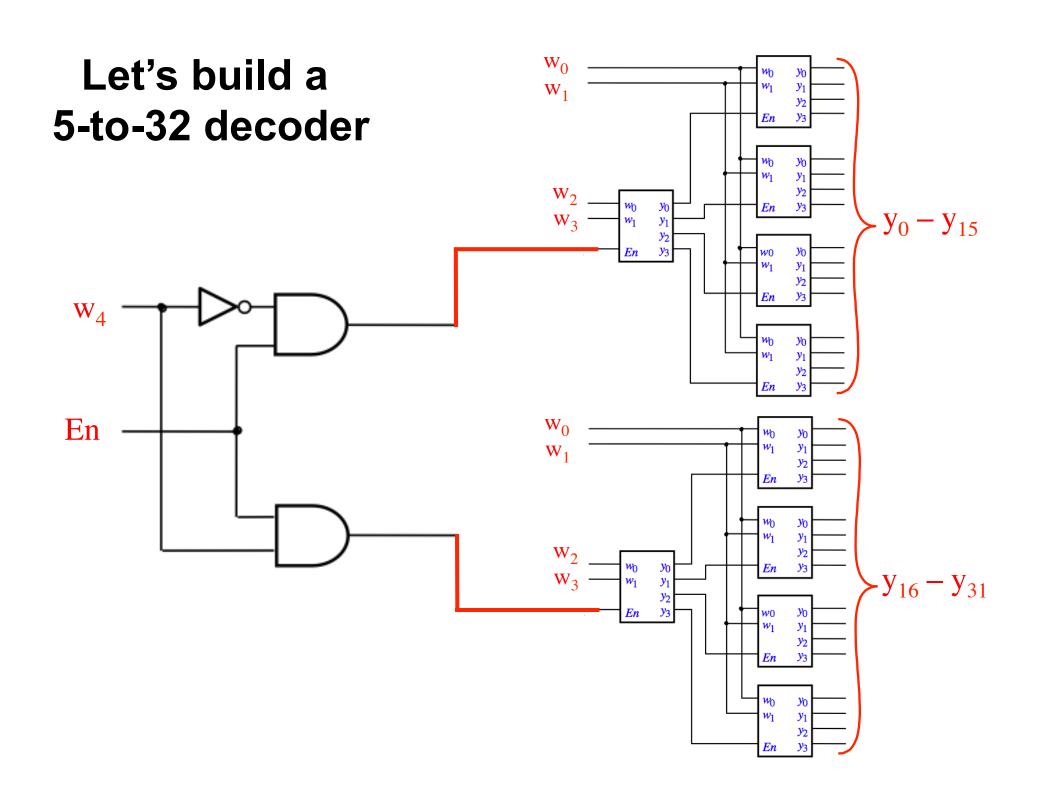

# Let's build a 5-to-32 decoder

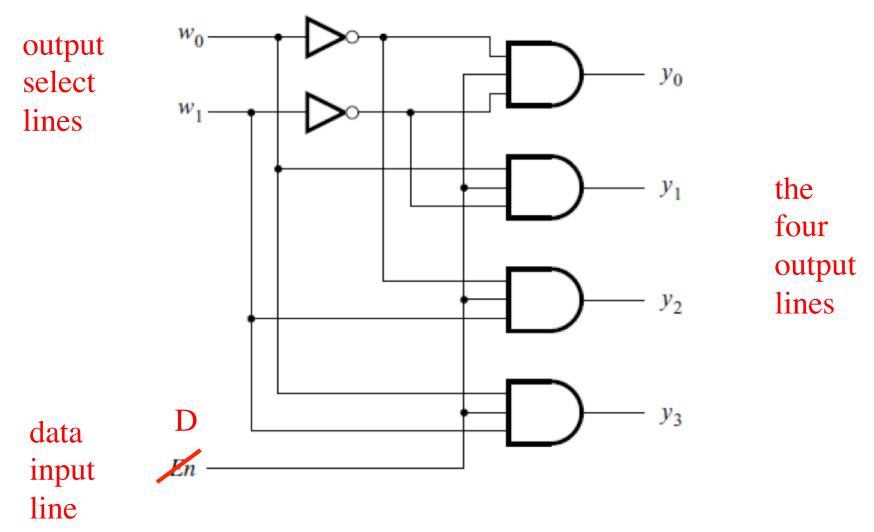

# **Demultiplexers**

## 1-to-4 Demultiplexer (Definition)

- Has one data input line: D

- Has two output select lines: w<sub>1</sub> and w<sub>0</sub>

- Has four outputs:  $y_0$ ,  $y_1$ ,  $y_2$ , and  $y_3$

- If  $w_1=0$  and  $w_0=0$ , then the output  $y_0$  is set to D

- If  $w_1=0$  and  $w_0=1$ , then the output  $y_1$  is set to D

- If  $w_1=1$  and  $w_0=0$ , then the output  $y_2$  is set to D

- If  $w_1=1$  and  $w_0=1$ , then the output  $y_3$  is set to D

- Only one output is set to D. All others are set to 0.

# A 1-to-4 demultiplexer built with a 2-to-4 decoder

# A 1-to-4 demultiplexer built with a 2-to-4 decoder

[ Figure 4.14c from the textbook ]

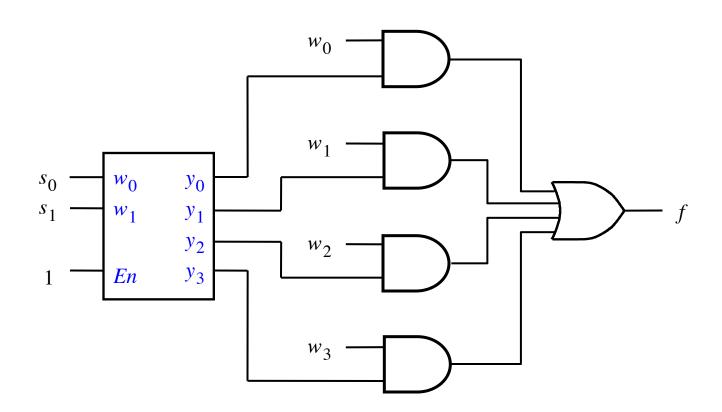

# Multiplexers (Implemented with Decoders)

# A 4-to-1 multiplexer built using a 2-to-4 decoder

## **Encoders**

# **Binary Encoders**

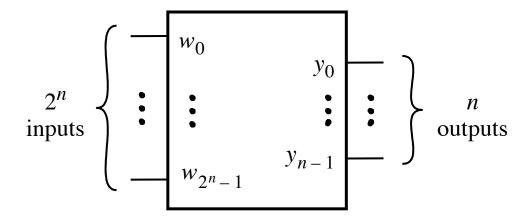

## A 2<sup>n</sup>-to-n binary encoder

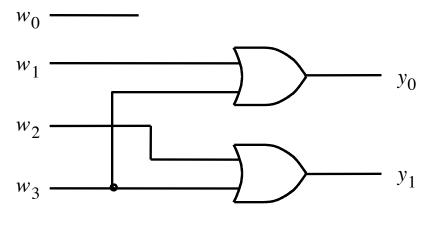

## A 4-to-2 binary encoder

| $w_3$ | $w_2$ | $w_1$ | $w_0$ | $y_1$ | $y_0$ |

|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 1     | 0     | 0     |

| 0     | 0     | 1     | 0     | 0     | 1     |

| 0     | 1     | 0     | 0     | 1     | 0     |

| 1     | 0     | 0     | 0     | 1     | 1     |

(a) Truth table

(b) Circuit

[ Figure 4.19 from the textbook ]

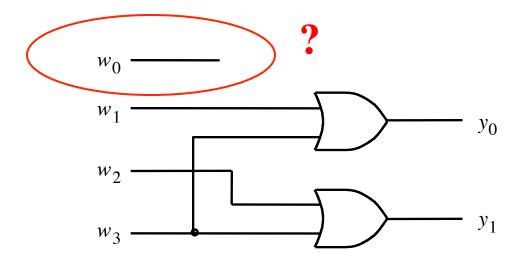

## A 4-to-2 binary encoder

| $w_3$ | $w_2$ | $w_1$ | $w_0$ | $y_1$ | $y_0$ |

|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 1     | 0     | 0     |

| 0     | 0     | 1     | 0     | 0     | 1     |

| 0     | 1     | 0     | 0     | 1     | 0     |

| 1     | 0     | 0     | 0     | 1     | 1     |

(a) Truth table

(b) Circuit

[ Figure 4.19 from the textbook ]

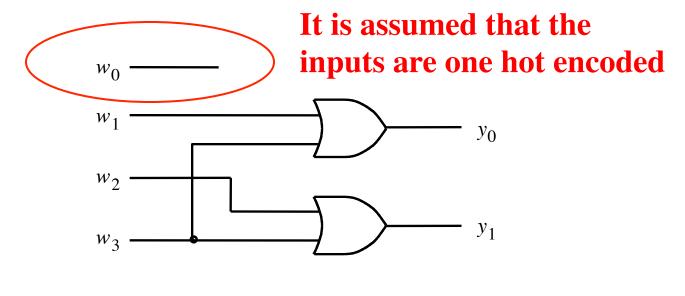

### A 4-to-2 binary encoder

| $w_3$ | $w_2$ | $w_1$ | $w_0$ | $y_1$ | $y_0$ |

|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 1     | 0     | 0     |

| 0     | 0     | 1     | 0     | 0     | 1     |

| 0     | 1     | 0     | 0     | 1     | 0     |

| 1     | 0     | 0     | 0     | 1     | 1     |

#### (a) Truth table

(b) Circuit

[ Figure 4.19 from the textbook ]

# **Priority Encoders**

## Truth table for a 4-to-2 priority encoder

| $w_3$ | $w_2$ | $w_1$ | $w_0$ | $y_1$ | $y_0$ | $\mathcal{Z}$ |

|-------|-------|-------|-------|-------|-------|---------------|

| 0     | 0     | 0     | 0     | d     | d     | 0             |

| 0     | 0     | 0     | 1     | 0     | 0     | 1             |

| 0     | 0     | 1     | X     | 0     | 1     | 1             |

| 0     | 1     | X     | X     | 1     | 0     | 1             |

| 1     | X     | X     | X     | 1     | 1     | 1             |

### Truth table for a 4-to-2 priority encoder

| $w_3$ | $w_2$ | $w_1$ | $w_0$ | $y_1$ | $y_0$ | z |

|-------|-------|-------|-------|-------|-------|---|

| 0     | 0     | 0     | 0     | d     | d     | 0 |

| 0     | 0     | 0     | 1     | 0     | 0     | 1 |

| 0     | 0     | 1     | X     | 0     | 1     | 1 |

| 0     | 1     | X     | X     | 1     | 0     | 1 |

| 1     | X     | X     | X     | 1     | 1     | 1 |

$$i_0 = \overline{w}_3 \overline{w}_2 \overline{w}_1 w_0$$

$$i_1 = \overline{w}_3 \overline{w}_2 w_1$$

$$i_2 = \overline{w}_3 w_2$$

$$i_3 = w_3$$

$$y_0 = i_1 + i_3$$

$y_1 = i_2 + i_3$

$$z = i_0 + i_1 + i_2 + i_3$$

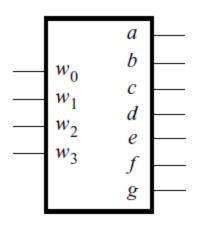

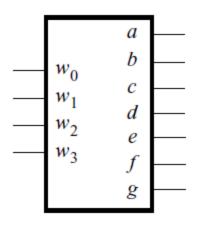

## **Code Converter (Definition)**

Converts from one type of input encoding to a different type of output encoding.

# **Code Converter (Definition)**

- Converts from one type of input encoding to a different type of output encoding.

- A decoder does that as well, but its outputs are always one-hot encoded so the output code is really only one type of output code.

- A binary encoder does that as well but its inputs are always one-hot encoded so the input code is really only one type of input code.

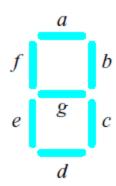

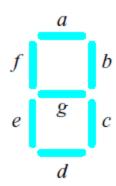

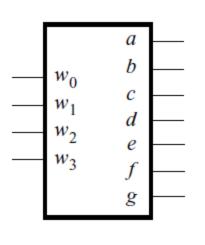

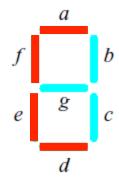

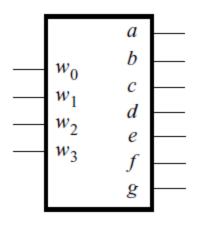

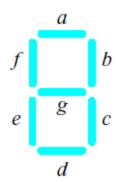

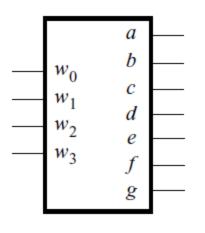

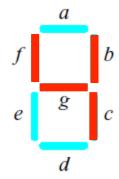

(a) Code converter

(b) 7-segment display

| $w_3$ | $w_2$ | $w_1$ | $w_0$ | а | b | c | d | e | f | g |

|-------|-------|-------|-------|---|---|---|---|---|---|---|

| 0     | 0     | 0     | 0     | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 0     | 0     | 0     | 1     | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 0     | 0     | 1     | 0     | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 0     | 0     | 1     | 1     | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 0     | 1     | 0     | 0     | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 0     | 1     | 0     | 1     | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 0     | 1     | 1     | 0     | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0     | 1     | 1     | 1     | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 1     | 0     | 0     | 0     | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1     | 0     | 0     | 1     | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1     | 0     | 1     | 0     | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 1     | 0     | 1     | 1     | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1     | 1     | 0     | 0     | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| 1     | 1     | 0     | 1     | 0 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1     | 1     | 1     | 0     | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 1     | 1     | 1     | 1     | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

(c) Truth table

(b) 7-segment display

| $w_3$ | $w_2$ | $w_1$ | $w_0$ | а | b | c | d | e | f | g |

|-------|-------|-------|-------|---|---|---|---|---|---|---|

| 0     | 0     | 0     | 0     | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 0     | 0     | 0     | 1     | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 0     | 0     | 1     | 0     | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 0     | 0     | 1     | 1     | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 0     | 1     | 0     | 0     | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 0     | 1     | 0     | 1     | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 0     | 1     | 1     | 0     | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0     | 1     | 1     | 1     | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 1     | 0     | 0     | 0     | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1     | 0     | 0     | 1     | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1     | 0     | 1     | 0     | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 1     | 0     | 1     | 1     | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1     | 1     | 0     | 0     | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| 1     | 1     | 0     | 1     | 0 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1     | 1     | 1     | 0     | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 1     | 1     | 1     | 1     | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

(c) Truth table

(a) Code converter

(b) 7-segment display

| $w_3$ | $w_2$ | $w_1$ | $w_0$ | a | b | c | d | e | f | g |

|-------|-------|-------|-------|---|---|---|---|---|---|---|

| 0     | 0     | 0     | 0     | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 0     | 0     | 0     | 1     | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 0     | 0     | 1     | 0     | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 0     | 0     | 1     | 1     | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 0     | 1     | 0     | 0     | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 0     | 1     | 0     | 1     | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 0     | 1     | 1     | 0     | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0     | 1     | 1     | 1     | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 1     | 0     | 0     | 0     | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1     | 0     | 0     | 1     | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1     | 0     | 1     | 0     | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 1     | 0     | 1     | 1     | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1     | 1     | 0     | 0     | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| 1     | 1     | 0     | 1     | 0 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1     | 1     | 1     | 0     | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 1     | 1     | 1     | 1     | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

(a) Code converter

(b) 7-segment display

| $w_3$ | $w_2$ | $w_1$ | $w_0$ | а | b | c | d | e | f | g |

|-------|-------|-------|-------|---|---|---|---|---|---|---|

| 0     | 0     | 0     | 0     | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 0     | 0     | 0     | 1     | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 0     | 0     | 1     | 0     | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 0     | 0     | 1     | 1     | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 0     | 1     | 0     | 0     | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 0     | 1     | 0     | 1     | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 0     | 1     | 1     | 0     | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0     | 1     | 1     | 1     | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 1     | 0     | 0     | 0     | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1     | 0     | 0     | 1     | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1     | 0     | 1     | 0     | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 1     | 0     | 1     | 1     | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1     | 1     | 0     | 0     | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| 1     | 1     | 0     | 1     | 0 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1     | 1     | 1     | 0     | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 1     | 1     | 1     | 1     | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

(c) Truth table

(a) Code converter

(b) 7-segment display

| $w_3$ | $w_2$ | $w_1$ | $w_0$ | а | b | c | d | e | f | g |

|-------|-------|-------|-------|---|---|---|---|---|---|---|

| 0     | 0     | 0     | 0     | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 0     | 0     | 0     | 1     | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 0     | 0     | 1     | 0     | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 0     | 0     | 1     | 1     | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 0     | 1     | 0     | 0     | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 0     | 1     | 0     | 1     | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 0     | 1     | 1     | 0     | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0     | 1     | 1     | 1     | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 1     | 0     | 0     | 0     | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1     | 0     | 0     | 1     | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1     | 0     | 1     | 0     | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 1     | 0     | 1     | 1     | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1     | 1     | 0     | 0     | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| 1     | 1     | 0     | 1     | 0 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1     | 1     | 1     | 0     | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 1     | 1     | 1     | 1     | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

(c) Truth table

| $x_3$ | $x_2$ | $x_1$ | $x_0$ | а | b | С | d | e | f | g |

|-------|-------|-------|-------|---|---|---|---|---|---|---|

| 0     | 0     | 0     | 0     | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 0     | 0     | 0     | 1     | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 0     | 0     | 1     | 0     | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 0     | 0     | 1     | 1     | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 0     | 1     | 0     | 0     | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 0     | 1     | 0     | 1     | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 0     | 1     | 1     | 0     | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0     | 1     | 1     | 1     | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 1     | 0     | 0     | 0     | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1     | 0     | 0     | 1     | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1     | 0     | 1     | 0     | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 1     | 0     | 1     | 1     | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1     | 1     | 0     | 0     | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| 1     | 1     | 0     | 1     | 0 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1     | 1     | 1     | 0     | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 1     | 1     | 1     | 1     | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| $x_3$ | $x_0$ | a | b | C | d | e | f | g |   |   |

|-------|-------|---|---|---|---|---|---|---|---|---|

| 0     | 0     | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 0     | 0     | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 0     | 0     | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 0     | 0     | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 0     | 1     | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 0     | 1     | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 0     | 1     | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0     | 1     | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 1     | 0     | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1     | 0     | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1     | 0     | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 1     | 0     | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1     | 1     | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| 1     | 1     | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1     | 1     | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 1     | 1     | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

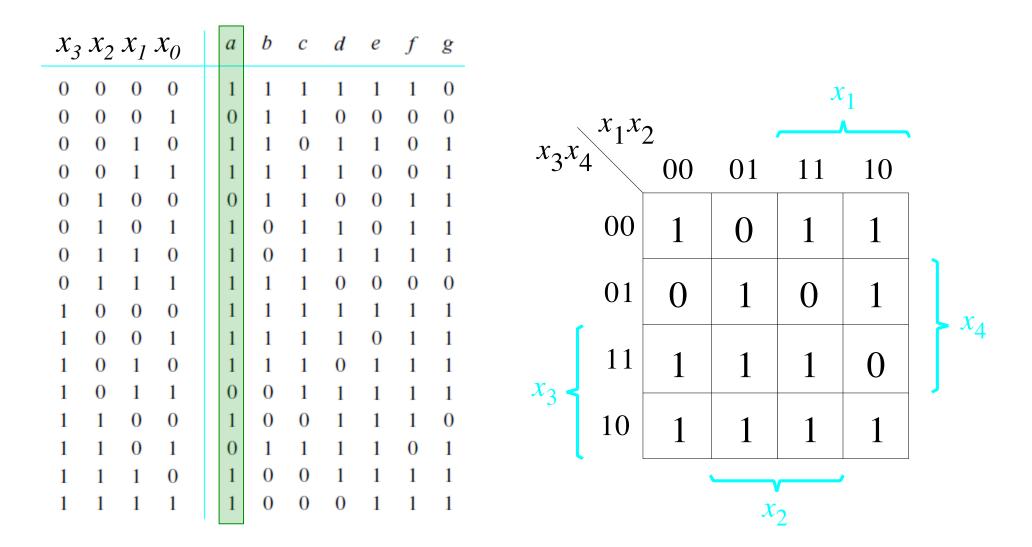

$f(x_1, x_2, x_3, x_4) = \sum m(0, 2, 3, 5, 6, 7, 8, 9, 10, 12, 14, 15)$

$f(x_1, x_2, x_3, x_4) = \sum m(0, 2, 3, 5, 6, 7, 8, 9, 10, 12, 14, 15)$

| $x_3$ | $x_2$ | $x_1$ | $x_0$ | а | b | c | d | е | f | g |

|-------|-------|-------|-------|---|---|---|---|---|---|---|

| 0     | 0     | 0     | 0     | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 0     | 0     | 0     | 1     | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 0     | 0     | 1     | 0     | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 0     | 0     | 1     | 1     | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 0     | 1     | 0     | 0     | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 0     | 1     | 0     | 1     | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 0     | 1     | 1     | 0     | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0     | 1     | 1     | 1     | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 1     | 0     | 0     | 0     | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1     | 0     | 0     | 1     | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1     | 0     | 1     | 0     | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 1     | 0     | 1     | 1     | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1     | 1     | 0     | 0     | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| 1     | 1     | 0     | 1     | 0 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1     | 1     | 1     | 0     | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 1     | 1     | 1     | 1     | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| $x_3$ | $x_2$ | $x_1$ | $x_0$ | a | b | c | d | e | f | g |          |    |                            |        |          |                  |

|-------|-------|-------|-------|---|---|---|---|---|---|---|----------|----|----------------------------|--------|----------|------------------|

| 0     | 0     | 0     | 0     | 1 | 1 | 1 | 1 | 1 | 1 | 0 |          |    |                            | $\chi$ | ⁄ 1      |                  |

| 0     | 0     | 0     | 1     | 0 | 1 | 1 | 0 | 0 | 0 | 0 | $x_1x$   |    |                            |        | 1        |                  |

| 0     | 0     | 1     | 0     | 1 | 1 | 0 | 1 | 1 | 0 | 1 | $x_3x_4$ |    |                            |        |          |                  |

| 0     | 0     | 1     | 1     | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 3.4      | 00 | 01                         | 11     | 10       |                  |

| 0     | 1     | 0     | 0     | 0 | 1 | 1 | 0 | 0 | 1 | 1 | ·        |    |                            |        |          |                  |

| 0     | 1     | 0     | 1     | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 00       | 1  | 0                          | 1      | 1        |                  |

| 0     | 1     | 1     | 0     | 1 | 0 | 1 | 1 | 1 | 1 | 1 |          |    |                            |        |          | 1                |

| 0     | 1     | 1     | 1     | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 01       | 0  | 1                          | 1      | 1        |                  |

| 1     | 0     | 0     | 0     | 1 | 1 | 1 | 1 | 1 | 1 | 1 | •        |    | 1                          | 1      | <b>.</b> | - x <sub>4</sub> |

| 1     | 0     | 0     | 1     | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 1      |    |                            |        | 4        | 4                |

| 1     | 0     | 1     | 0     | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 11       | 1  | 0                          | 0      | 1        |                  |

| 1     | 0     | 1     | 1     | 0 | 0 | 1 | 1 | 1 | 1 | 1 | $x_3$    |    |                            |        |          | . ,              |

| 1     | 1     | 0     | 0     | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 10       | 1  | 1                          | 1      | 0        |                  |

| 1     | 1     | 0     | 1     | 0 | 1 | 1 | 1 | 1 | 0 | 1 | l        |    | _                          |        |          |                  |

| 1     | 1     | 1     | 0     | 1 | 0 | 0 | 1 | 1 | 1 | 1 |          |    |                            |        |          |                  |

| 1     | 1     | 1     | 1     | 1 | 0 | 0 | 0 | 1 | 1 | 1 |          |    | $\boldsymbol{\mathcal{X}}$ | 2      |          |                  |

$f(x_1, x_2, x_3, x_4) = \sum m(0, 2, 3, 5, 6, 8, 9, 11, 12, 13, 14)$

# **Arithmetic Comparison Circuits**

## Truth table for a one-bit digital comparator

| Inp            | uts | Outputs |       |       |  |  |  |  |  |  |

|----------------|-----|---------|-------|-------|--|--|--|--|--|--|

| $\overline{A}$ | B   | A > B   | A = B | A < B |  |  |  |  |  |  |

| 0              | 0   | 0       | 1     | 0     |  |  |  |  |  |  |

| 0              | 1   | 0       | 0     | 1     |  |  |  |  |  |  |

| 1              | 0   | 1       | 0     | 0     |  |  |  |  |  |  |

| 1              | 1   | 0       | 1     | 0     |  |  |  |  |  |  |

## A one-bit digital comparator circuit

| Inp            | uts | Outputs |       |       |  |  |  |  |  |  |

|----------------|-----|---------|-------|-------|--|--|--|--|--|--|

| $\overline{A}$ | B   | A > B   | A = B | A < B |  |  |  |  |  |  |

| 0              | 0   | 0       | 1     | 0     |  |  |  |  |  |  |

| 0              | 1   | 0       | 0     | 1     |  |  |  |  |  |  |

| 1              | 0   | 1       | 0     | 0     |  |  |  |  |  |  |

| 1              | 1   | 0       | 1     | 0     |  |  |  |  |  |  |

## Truth table for a two-bit digital comparator

|       | Inp   | uts   |       | Outputs |       |       |  |  |  |

|-------|-------|-------|-------|---------|-------|-------|--|--|--|

| $A_1$ | $A_0$ | $B_1$ | $B_0$ | A < B   | A = B | A > B |  |  |  |

| 0     | 0     | 0     | 0     | 0       | 1     | 0     |  |  |  |

| 0     | 0     | 0     | 1     | 1       | 0     | 0     |  |  |  |

| 0     | 0     | 1     | 0     | 1       | 0     | 0     |  |  |  |

| 0     | 0     | 1     | 1     | 1       | 0     | 0     |  |  |  |

| 0     | 1     | 0     | 0     | 0       | 0     | 1     |  |  |  |

| 0     | 1     | 0     | 1     | 0       | 1     | 0     |  |  |  |

| 0     | 1     | 1     | 0     | 1       | 0     | 0     |  |  |  |

| 0     | 1     | 1     | 1     | 1       | 0     | 0     |  |  |  |

| 1     | 0     | 0     | 0     | 0       | 0     | 1     |  |  |  |

| 1     | 0     | 0     | 1     | 0       | 0     | 1     |  |  |  |

| 1     | 0     | 1     | 0     | 0       | 1     | 0     |  |  |  |

| 1     | 0     | 1     | 1     | 1       | 0     | 0     |  |  |  |

| 1     | 1     | 0     | 0     | 0       | 0     | 1     |  |  |  |

| 1     | 1     | 0     | 1     | 0       | 0     | 1     |  |  |  |

| 1     | 1     | 1     | 0     | 0       | 0     | 1     |  |  |  |

| 1     | 1     | 1     | 1     | 0       | 1     | 0     |  |  |  |

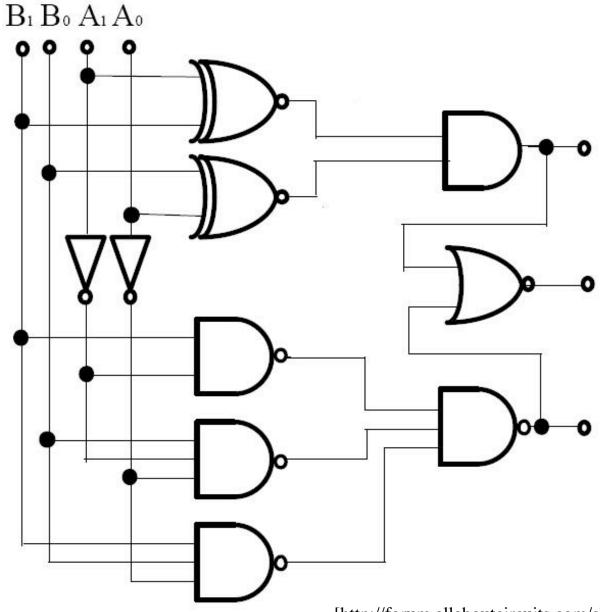

## A two-bit digital comparator circuit

[http://forum.allaboutcircuits.com/showthread.php?t=10561]

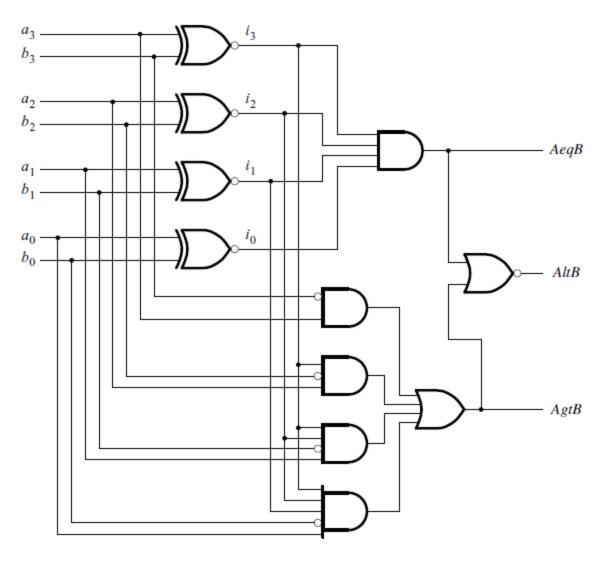

## A four-bit comparator circuit

[ Figure 4.22 from the textbook ]

# **Example Problems from Chapter 4**

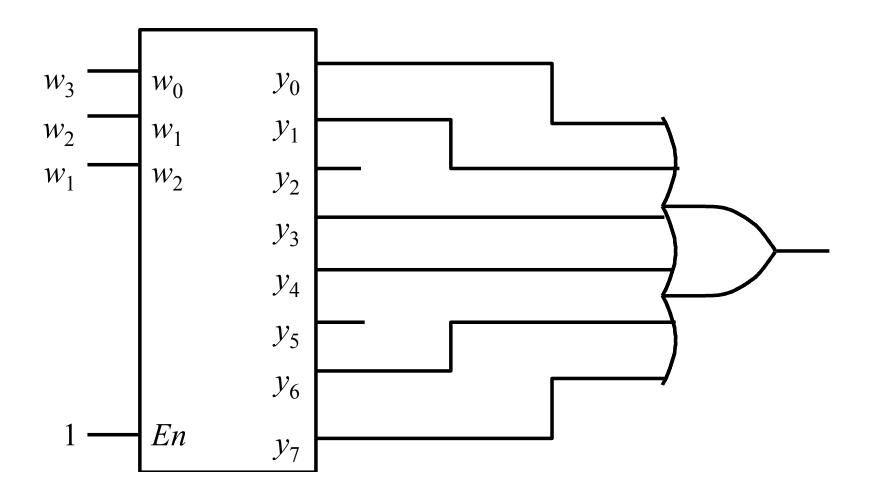

# **Example 1: SOP vs Decoders**

Implement the function

$$f(w_1, w_2, w_3) = \Sigma m(0, 1, 3, 4, 6, 7)$$

by using a 3-8 binary decoder and one OR gate.

#### **Solution Circuit**

$$f(w_1, w_2, w_3) = \sum m(0, 1, 3, 4, 6, 7)$$

#### Example 2: Implement an 8-to-3 binary encoder

| И | 7 | $w_6$ | $w_5$ | $w_4$ | $w_3$ | $w_2$ | $w_1$ | $w_0$ | $y_2$ | $y_1$ | $y_0$ |

|---|---|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|   | 0 | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     |

|   | 0 | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 1     |

|   | 0 | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 1     | 0     |

| Ô | 0 | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 0     | 1     | 1     |

|   | 0 | 0     | 0     | 1     | 0     | 0     | 0     | 0     | 1     | 0     | 0     |

| ì | 0 | 0     | 1     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 1     |

|   | 0 | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 0     |

|   | 1 | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 1     |

#### Example 2: Implement an 8-to-3 binary encoder

| $w_7$ | $w_6$ | $w_5$ | $w_4$ | $w_3$ | $w_2$ | $w_1$ | $w_0$ | $y_2$ | $y_1$ | $y_0$ |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     |

| 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 1     |

| 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 1     | 0     |

| 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 0     | 1     | 1     |

| 0     | 0     | 0     | 1     | 0     | 0     | 0     | 0     | 1     | 0     | 0     |

| 0     | 0     | 1     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 1     |

| 0     | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 0     |

| 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 1     |

$$y_2 = w_4 + w_5 + w_6 + w_7$$

$y_1 = w_2 + w_3 + w_6 + w_7$

$y_0 = w_1 + w_3 + w_5 + w_7$

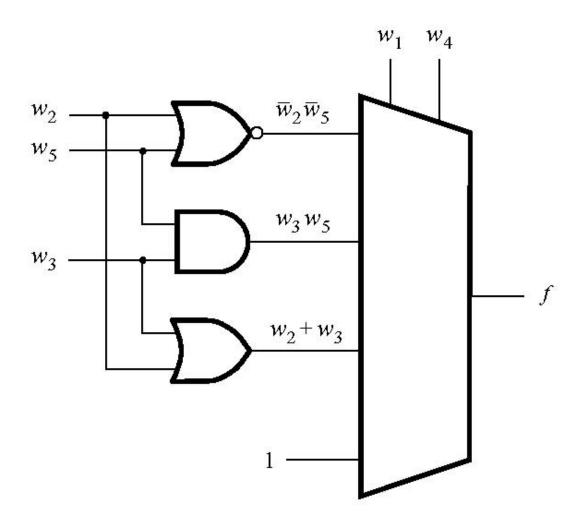

# Example 3:Circuit implementation using a multiplexer

Implement the function

$$f(w_1, w_2, w_3, w_4, w_5) = \overline{w}_1 \overline{w}_2 \overline{w}_4 \overline{w}_5 + w_1 w_2 + w_1 w_3 + w_1 w_4 + w_3 w_4 w_5$$

using a 4-to-1 multiplexer

# Some Boolean Algebra Leads To

$$\overline{w_{1}}\overline{w_{2}}\overline{w_{4}}\overline{w_{5}} + w_{1}w_{2} + w_{1}w_{3} + w_{1}w_{4} + w_{3}w_{4}w_{5}$$

$$\overline{w_{1}}\overline{w_{4}}(\overline{w_{5}}\overline{w_{2}}) + w_{4}(w_{3}w_{5}) + w_{1}(w_{2} + w_{3}) + w_{1}w_{4}(1)$$

$$\overline{w_{1}}\overline{w_{4}}(\overline{w_{5}}\overline{w_{2}}) + (\overline{w_{1}}+w_{1})w_{4}(w_{3}w_{5}) + w_{1}(\overline{w_{4}}+w_{4})(w_{2}+w_{3}) + w_{1}w_{4}(1)$$

$$\overline{w_{1}}\overline{w_{4}}(\overline{w_{5}}\overline{w_{2}}) + \overline{w_{1}}w_{4}(w_{3}w_{5}) + w_{1}\overline{w_{4}}(w_{2}+w_{3}) + w_{1}w_{4}(w_{3}w_{5} + (w_{2}+w_{3}) + 1)$$

$$\overline{w_{1}}\overline{w_{4}}(\overline{w_{5}}\overline{w_{2}}) + \overline{w_{1}}w_{4}(w_{3}w_{5}) + w_{1}\overline{w_{4}}(w_{2}+w_{3}) + w_{1}w_{4}(1)$$

Note that the split is by  $w_1$  and  $w_4$ , not  $w_1$  and  $w_2$

#### **Solution Circuit**

$$\overline{w_1}\overline{w_4}(\overline{w_5}\overline{w_2}) + \overline{w_1}w_4(w_3w_5) + w_1\overline{w_4}(w_2 + w_3) + w_1w_4(1)$$

# Some Final Things from Chapter 4

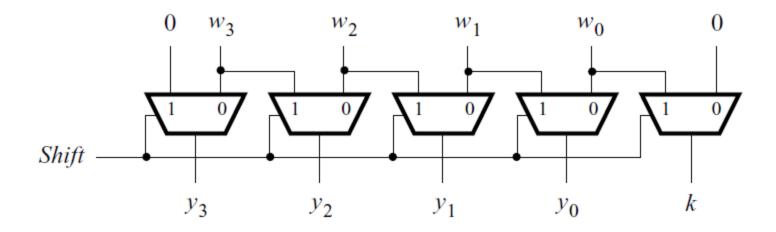

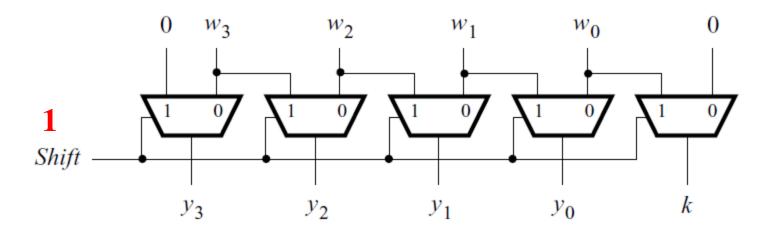

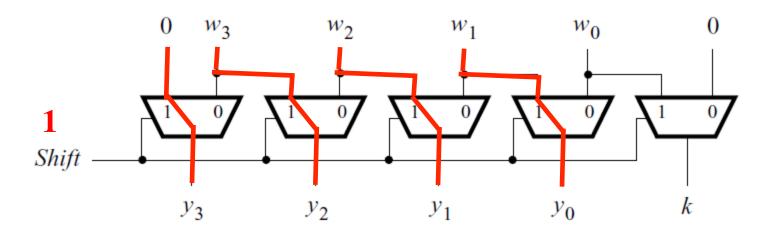

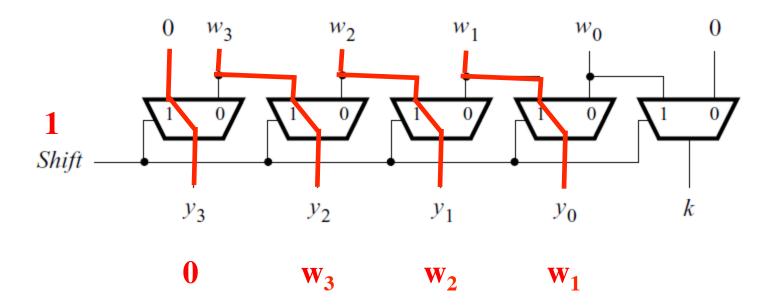

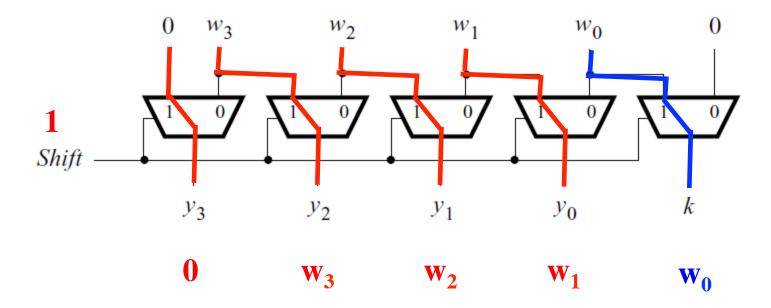

No shift in this case.

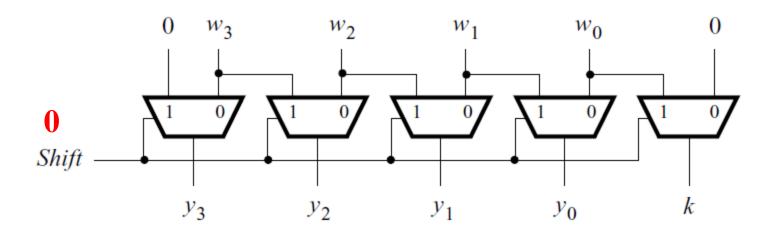

Shift to the right by 1 bit

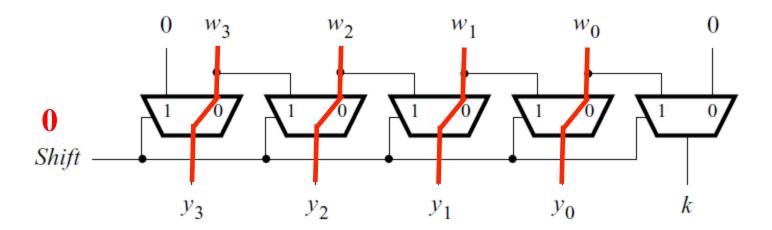

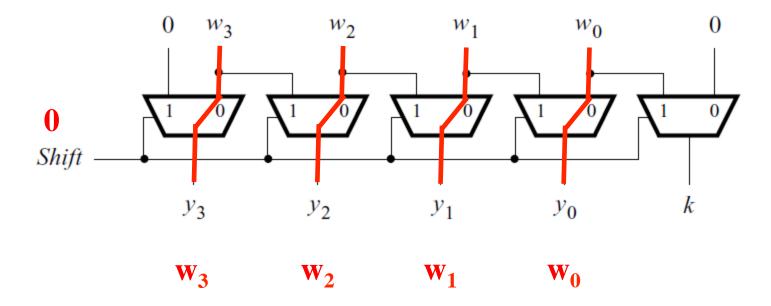

Shift to the right by 1 bit

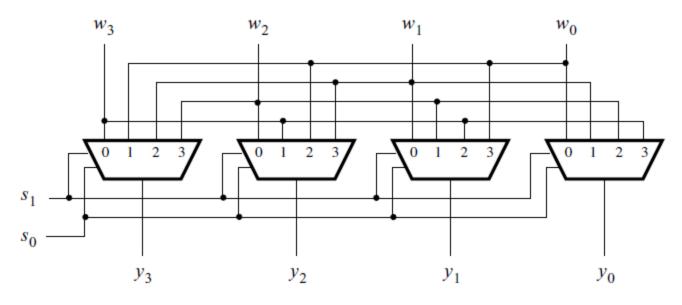

## A barrel shifter circuit

| $y_3$ | $y_2$             | $y_1$                                 | $y_0$                               |

|-------|-------------------|---------------------------------------|-------------------------------------|

| $w_3$ | $w_2$             | $w_1$                                 | $w_0$                               |

| $w_0$ | $w_3$             | $w_2$                                 | $w_1$                               |

| $w_1$ | $w_0$             | $w_3$                                 | $w_2$                               |

| $w_2$ | $w_1$             | $w_0$                                 | $w_3$                               |

|       | $w_3$ $w_0$ $w_1$ | $w_3 	 w_2 \\ w_0 	 w_3 \\ w_1 	 w_0$ | $w_3 \ w_2 \ w_1 \ w_0 \ w_3 \ w_2$ |

(a) Truth table

(b) Circuit

[ Figure 4.51 from the textbook ]

**Questions?**

## THE END