# CprE 281: Digital Logic

#### Instructor: Alexander Stoytchev

#### http://www.ece.iastate.edu/~alexs/classes/

# **Mealy State Model**

CprE 281: Digital Logic Iowa State University, Ames, IA Copyright © Alexander Stoytchev

## **Administrative Stuff**

- Homework 10 is out

- It is due on Monday Nov 14 @ 4pm

## **Administrative Stuff**

Final Project

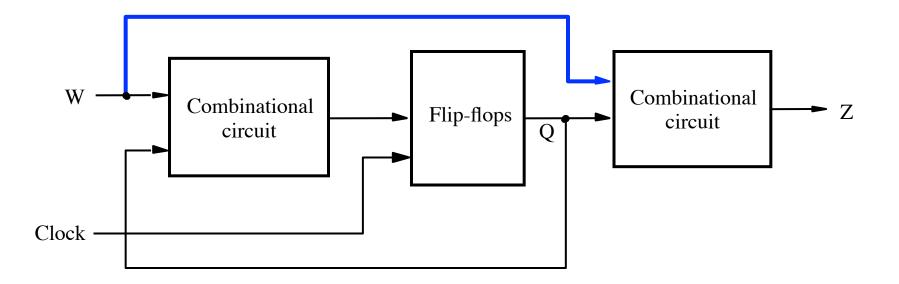

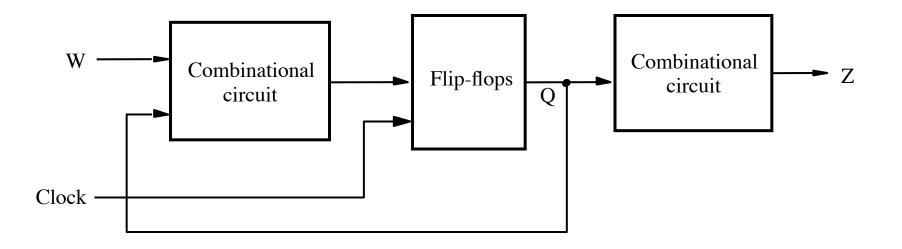

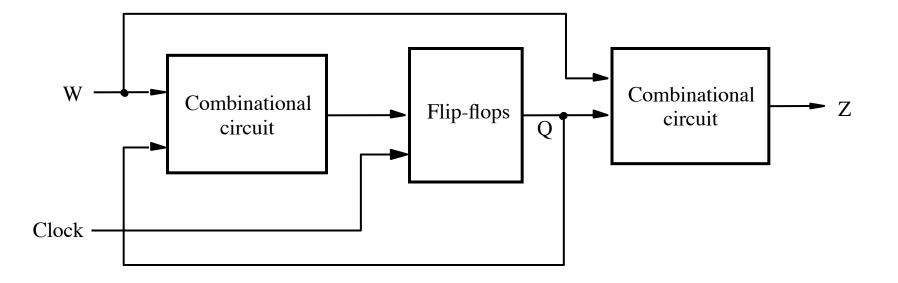

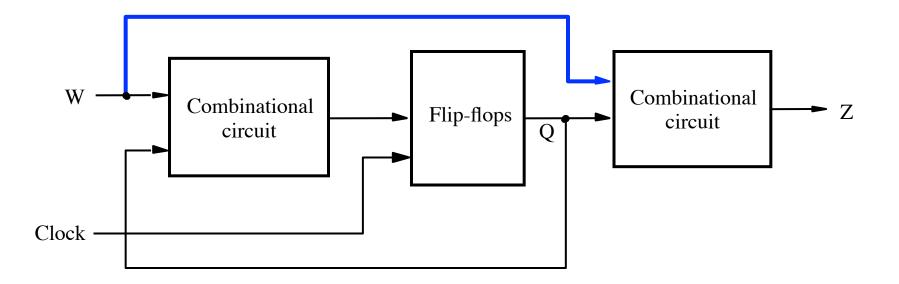

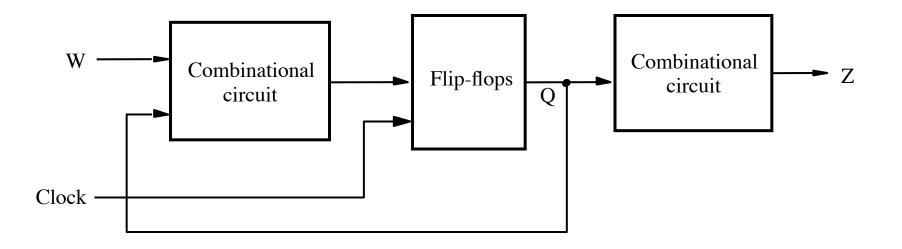

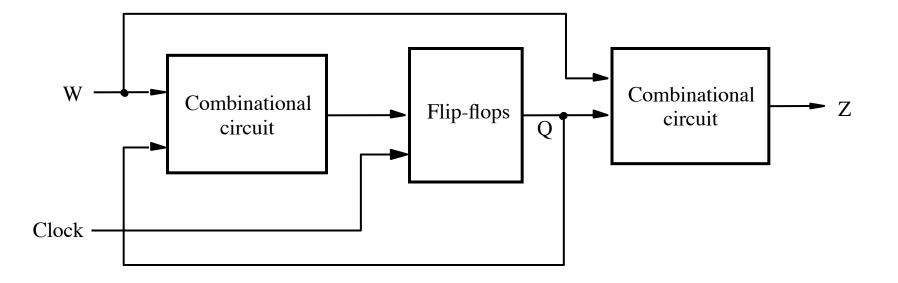

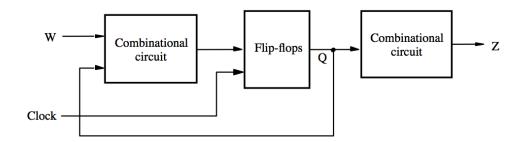

#### The general form of a synchronous sequential circuit

[Figure 6.1 from the textbook]

### **Moore Type**

## **Mealy Type**

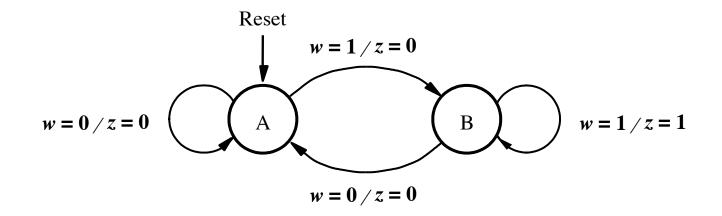

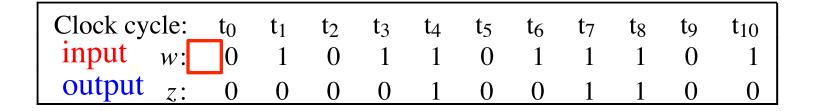

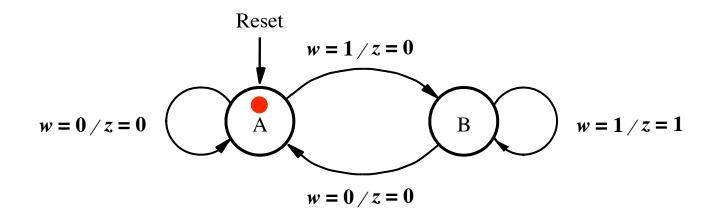

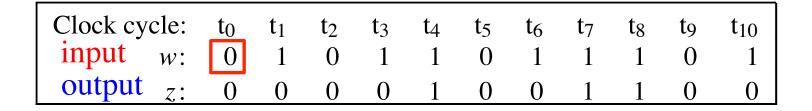

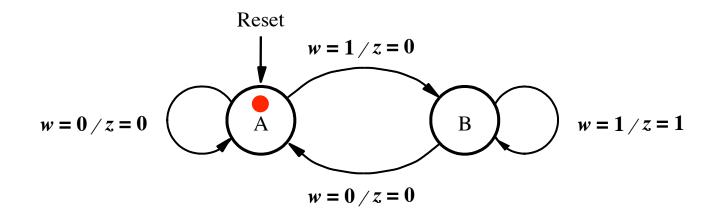

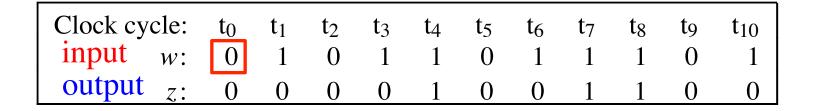

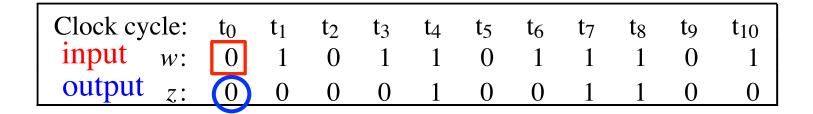

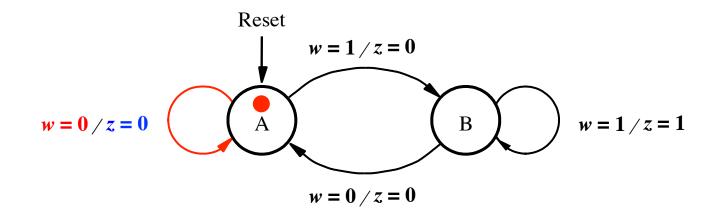

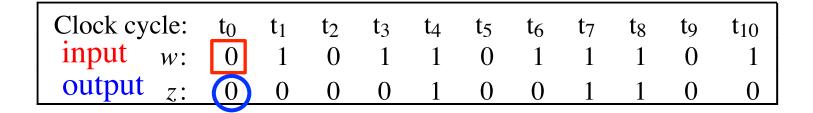

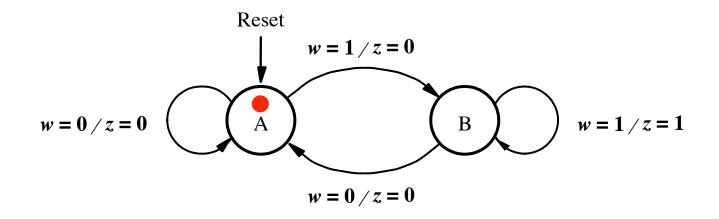

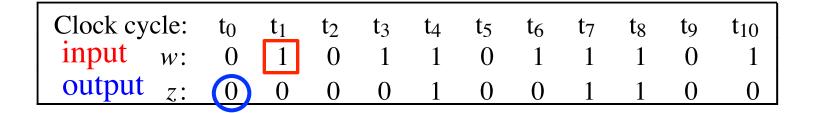

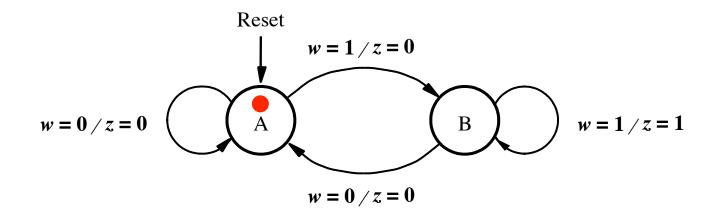

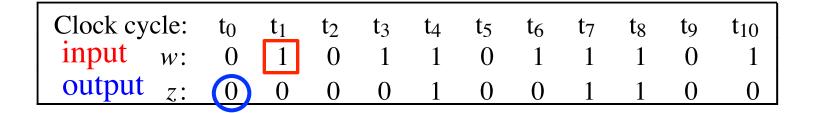

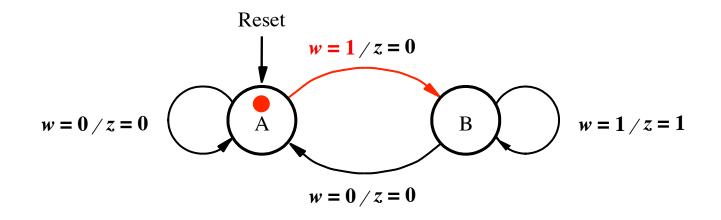

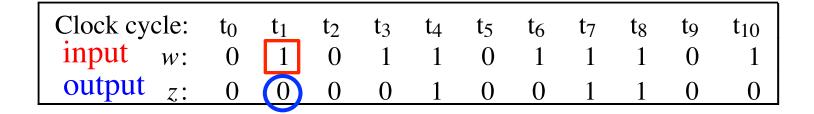

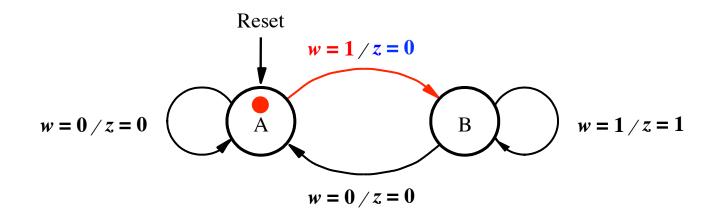

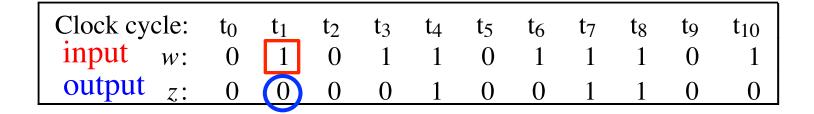

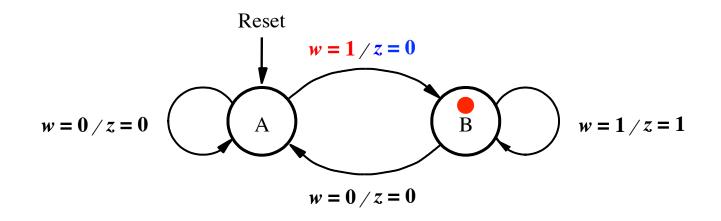

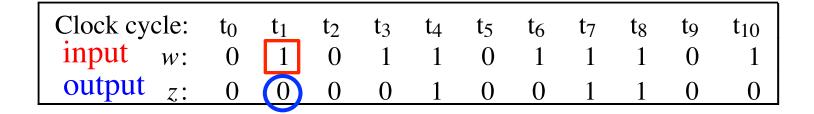

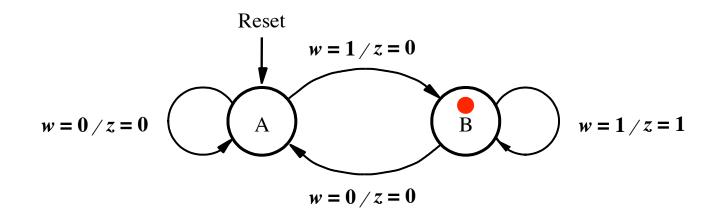

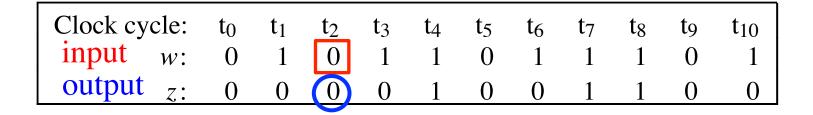

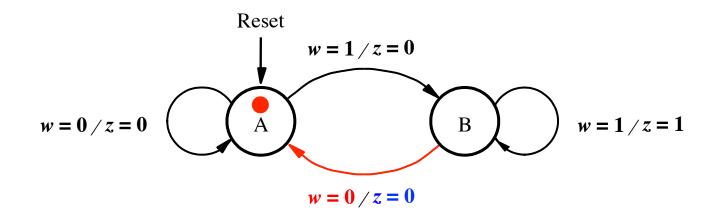

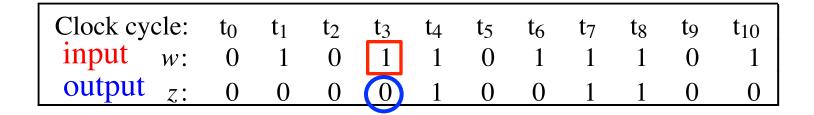

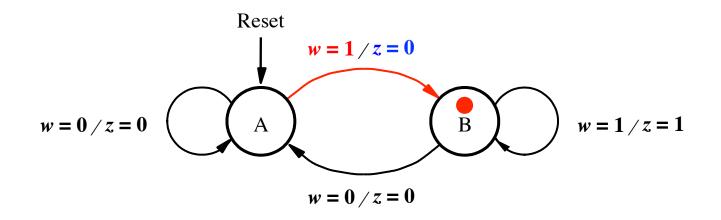

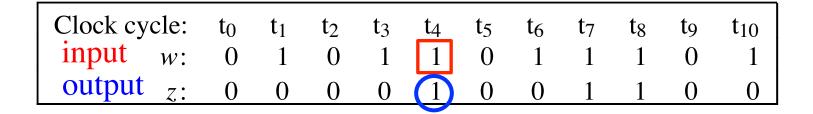

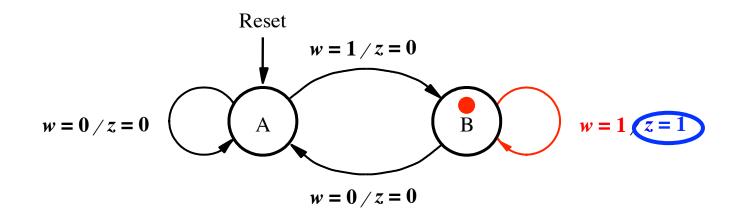

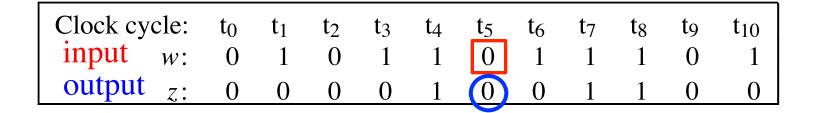

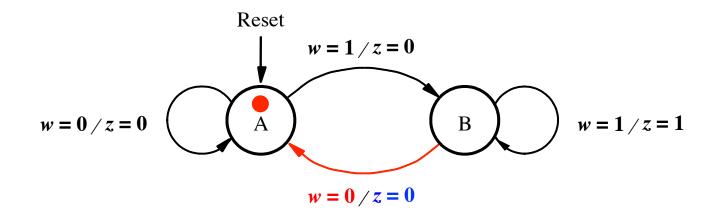

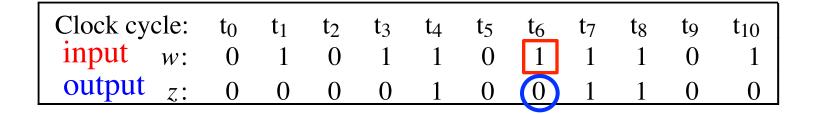

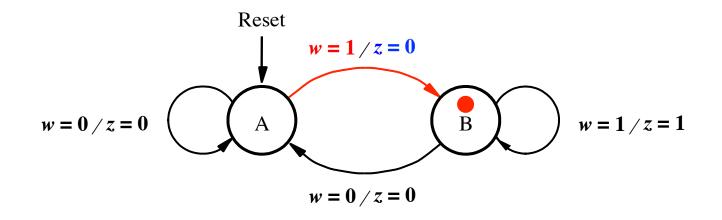

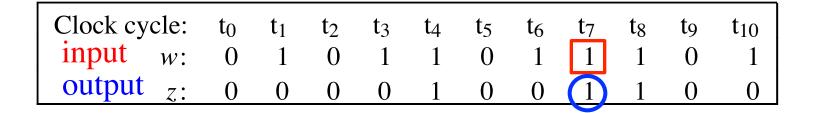

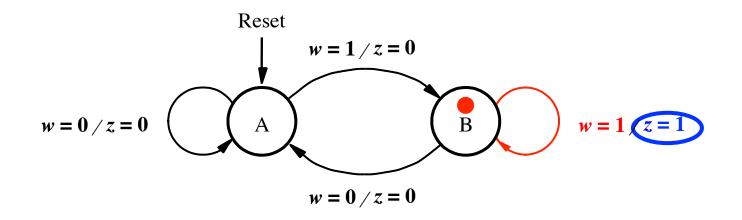

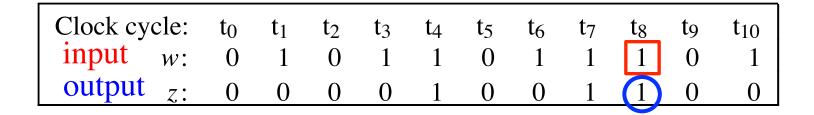

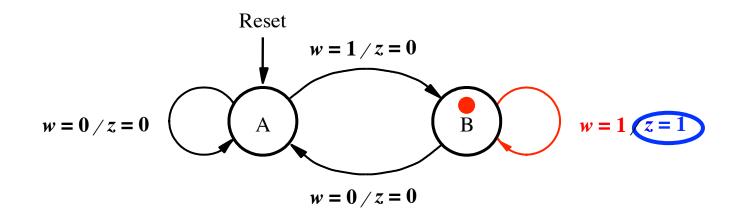

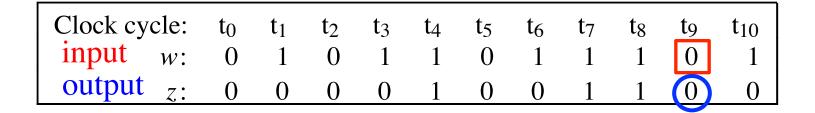

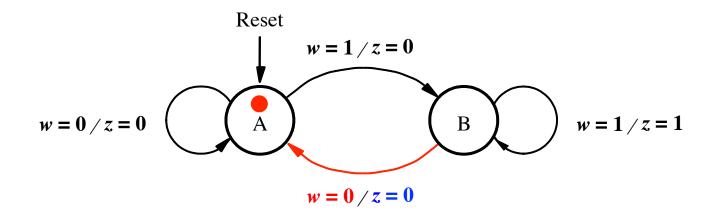

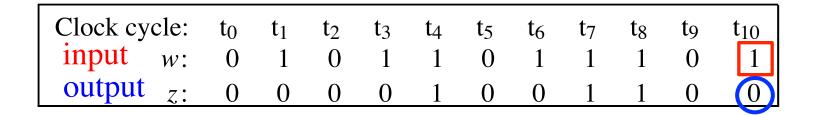

## Sample Problem

Implement a 11 detector. In other words, the output should be equal to 1 if two consecutive 1's have been detected on the input line. The output should become 1 as soon as the second 1 is detected in the input.

| Clock cycle:<br>w: | t <sub>0</sub> | $t_1$ | $t_2$ | t3 | t4 | t5 | t <sub>6</sub> | t7 | t <sub>8</sub> | t9 | t <sub>10</sub> |

|--------------------|----------------|-------|-------|----|----|----|----------------|----|----------------|----|-----------------|

| <i>w</i> :         | 0              | 1     | 0     | 1  | 1  | 0  | 1              | 1  | 1              | 0  | 1               |

|                    |                |       |       |    |    |    |                |    |                |    | 0               |

| Clock cycle:<br>input w: | t <sub>0</sub> | $t_1$ | $t_2$ | t3 | t4 | t5 | t <sub>6</sub> | t7 | t <sub>8</sub> | t9 | t <sub>10</sub> |

|--------------------------|----------------|-------|-------|----|----|----|----------------|----|----------------|----|-----------------|

| input w:                 | 0              | 1     | 0     | 1  | 1  | 0  | 1              | 1  | 1              | 0  | 1               |

| output <sub>z</sub> :    |                |       |       |    |    |    |                |    |                |    |                 |

| Clock cycle:<br>input w: | t <sub>0</sub> | $t_1$ | $t_2$ | t3 | t4 | t5 | t <sub>6</sub> | t7 | t <sub>8</sub> | t9 | t <sub>10</sub> |

|--------------------------|----------------|-------|-------|----|----|----|----------------|----|----------------|----|-----------------|

| input w:                 | 0              | 1     | 0     | 1  | 1  | 0  | 1              | 1  | 1              | 0  | 1               |

| output <sub>z</sub> :    | 0              | 0     | 0     | 0  | 1  | 0  | 0              | 1  | 1              | 0  | 0               |

| Clock cycle:          | $t_0$ | $t_1$ | $t_2$ | t3 | t4 | t5 |   |   | t <sub>8</sub> |   |   |

|-----------------------|-------|-------|-------|----|----|----|---|---|----------------|---|---|

| input w:              | 0     | 1     | 0     | 1  | 1  | 0  | 1 | 1 | 1              | 0 | 1 |

| output <sub>z</sub> : |       |       |       |    |    |    |   |   |                |   | 0 |

| Clock cycle:             | $t_0$ | $t_1$ | $t_2$ | t <sub>3</sub> | t4 | t5 | t <sub>6</sub> | t7 | t <sub>8</sub> | t9 | t <sub>10</sub> |

|--------------------------|-------|-------|-------|----------------|----|----|----------------|----|----------------|----|-----------------|

| Clock cycle:<br>input w: | 0     | 1     | 0     | 1              | 1  | 0  | 1              | 1  | 1              | 0  | 1               |

| output <sub>z</sub> :    | 0     | 0     | 0     | 0              | 1  | 0  | 0              | 1  | 1              | 0  | 0               |

| Clock cycle:          | $t_0$ | $t_1$ | $t_2$ | t <sub>3</sub> | t4 | t5 | t <sub>6</sub> | t7 | t <sub>8</sub> | t9 | t <sub>10</sub> |

|-----------------------|-------|-------|-------|----------------|----|----|----------------|----|----------------|----|-----------------|

| input w:              | 0     | 1     | 0     | 1              | 1  | 0  | 1              | 1  | 1              | 0  | 1               |

| output <sub>z</sub> : | 0     | 0     | 0     | 0              | 1  | 0  | 0              | 1  | 1              | 0  | 0               |

| Clock cycle:          | $t_0$ | $t_1$ | $t_2$ | t <sub>3</sub> | t4 | t5 | t <sub>6</sub> | t7 | t <sub>8</sub> | t9 | t <sub>10</sub> |

|-----------------------|-------|-------|-------|----------------|----|----|----------------|----|----------------|----|-----------------|

| input w:              | 0     | 1     | 0     | 1              | 1  | 0  | 1              | 1  | 1              | 0  | 1               |

| output <sub>z</sub> : |       |       |       |                |    |    |                |    |                |    |                 |

| Clock cycle:             | $t_0$ | $t_1$ | $t_2$ | t3 | t4 | t5 | t <sub>6</sub> | t7 | t <sub>8</sub> | t9 | t <sub>10</sub> |

|--------------------------|-------|-------|-------|----|----|----|----------------|----|----------------|----|-----------------|

| Clock cycle:<br>input w: | 0     | 1     | 0     | 1  | 1  | 0  | 1              | 1  | 1              | 0  | 1               |

| output <sub>z</sub> :    |       |       |       |    |    |    |                |    |                |    |                 |

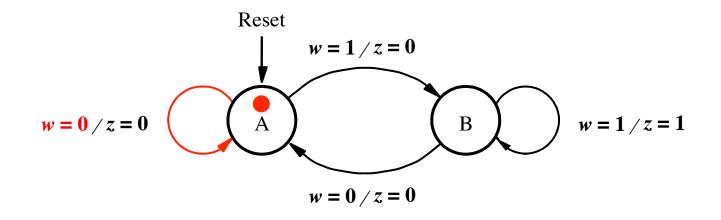

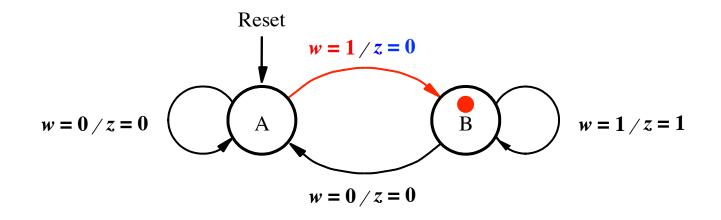

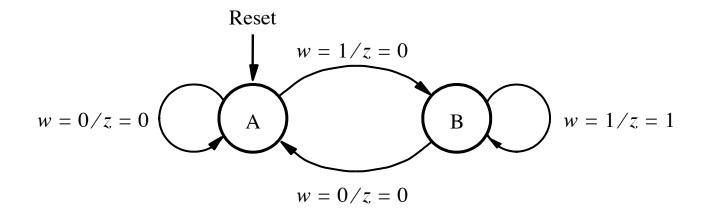

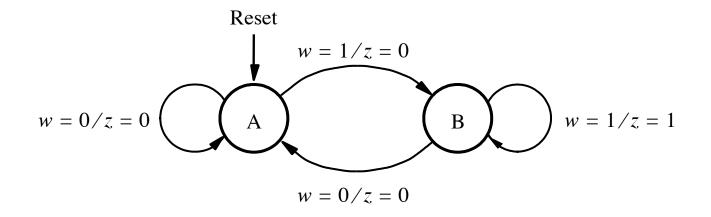

### State diagram of an FSM that realizes the task

[Figure 6.23 from the textbook]

#### Now Let's Do the State Table for this FSM

| Present | Next state |       | Output z |       |

|---------|------------|-------|----------|-------|

| state   | w = 0      | w = 1 | w = 0    | w = 1 |

| A       |            |       |          |       |

| В       |            |       |          |       |

#### Now Let's Do the State Table for this FSM

| Present | Next state |       | Output z |              |

|---------|------------|-------|----------|--------------|

| state   | w = 0      | w = 1 | w = 0    | <i>w</i> = 1 |

| A       | А          | В     | 0        | 0            |

| B       | A          | В     | 0        | 1            |

#### The State Table for this FSM

| Present | Next state |       | Output z |              |

|---------|------------|-------|----------|--------------|

| state   | w = 0      | w = 1 | w = 0    | <i>w</i> = 1 |

| A       | А          | В     | 0        | 0            |

| B       | A          | В     | 0        | 1            |

#### Let's Do the State-assigned Table

| Present | Next state    |   | Output z |       |

|---------|---------------|---|----------|-------|

| state   | w = 0 $w = 1$ |   | w = 0    | w = 1 |

| А       | А             | В | 0        | 0     |

| В       | A             | В | 0        | 1     |

|   | Present | Next state |       | Output |       |

|---|---------|------------|-------|--------|-------|

|   | state   | w = 0      | w = 1 | w = 0  | w = 1 |

|   | У       | Y          | Y     | Z      | Z.    |

| A | 0       |            |       |        |       |

| B | 1       |            |       |        |       |

#### Let's Do the State-assigned Table

| Present | Next state    |   | Output z |       |

|---------|---------------|---|----------|-------|

| state   | w = 0 $w = 1$ |   | w = 0    | w = 1 |

| А       | А             | В | 0        | 0     |

| В       | A             | В | 0        | 1     |

|   | Present | Next state |       | Output |       |

|---|---------|------------|-------|--------|-------|

|   | state   | w = 0      | w = 1 | w = 0  | w = 1 |

|   | У       | Y          | Y     | Z      | Z.    |

| A | 0       | 0          | 1     | 0      | 0     |

| B | 1       | 0          | 1     | 0      | 1     |

#### **The State-assigned Table**

|   | Present | Next state |       | Output |              |

|---|---------|------------|-------|--------|--------------|

|   | state   | w = 0      | w = 1 | w = 0  | <i>w</i> = 1 |

|   | У       | Y          | Y     | Z      | Z.           |

| A | 0       | 0          | 1     | 0      | 0            |

| В | 1       | 0          | 1     | 0      | 1            |

#### **The State-assigned Table**

|   | Present | Next state |       | Output |              |

|---|---------|------------|-------|--------|--------------|

|   | state   | w = 0      | w = 1 | w = 0  | <i>w</i> = 1 |

|   | У       | Y          | Y     | Z      | Z            |

| A | 0       | 0          | 1     | 0      | 0            |

| B | 1       | 0          | 1     | 0      | 1            |

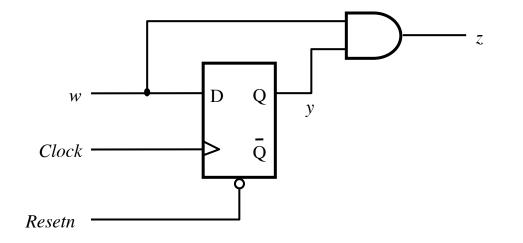

$$Y = D = w$$

$z = wy$

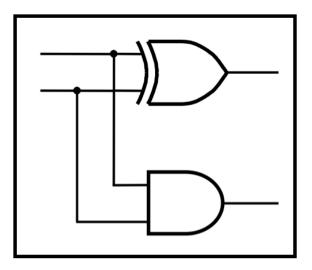

[ Figure 6.25 from the textbook ]

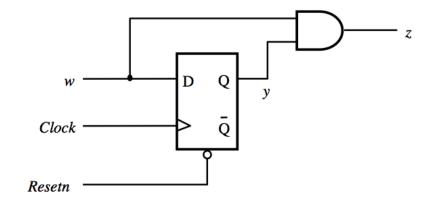

#### **The State-assigned Table**

|   | Present | Next state |       | Output |       |

|---|---------|------------|-------|--------|-------|

|   | state   | w = 0      | w = 1 | w = 0  | w = 1 |

|   | У       | Y          | Y     | Z      | Z     |

| A | 0       | 0          | 1     | 0      | 0     |

| В | 1       | 0          | 1     | 0      | 1     |

Y = D = w z = wy

This assumes D flip-flop

[Figure 6.25 from the textbook]

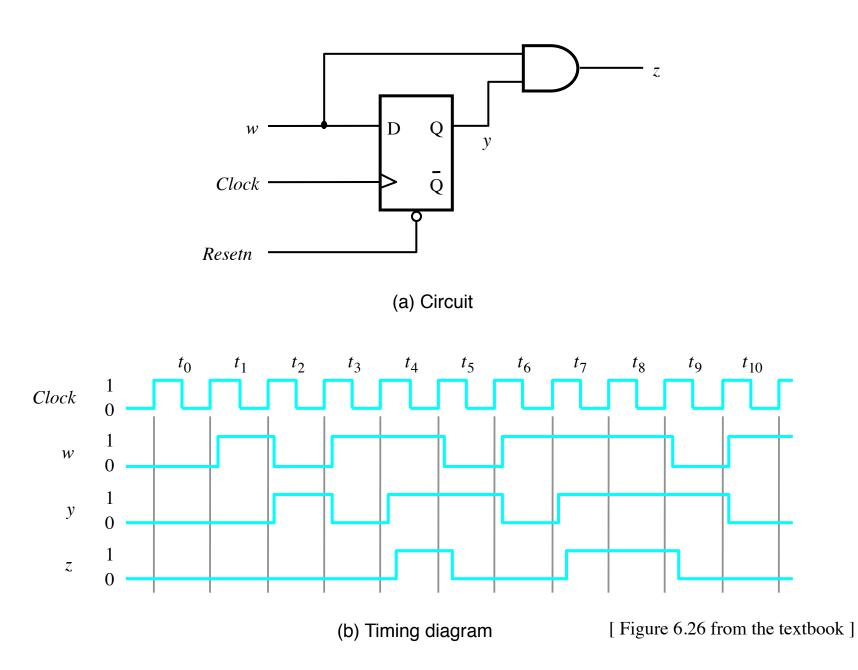

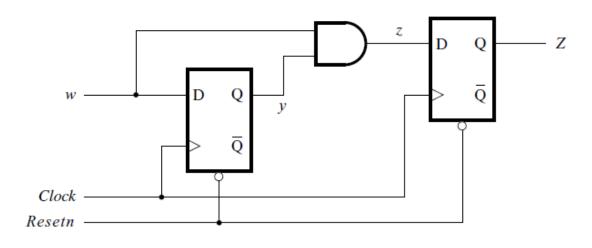

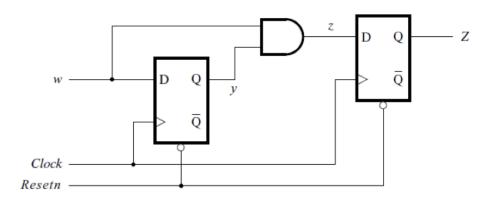

#### **Circuit Implementation of the FSM**

$$Y = D = w$$

$z = wy$

[Figure 6.26 from the textbook]

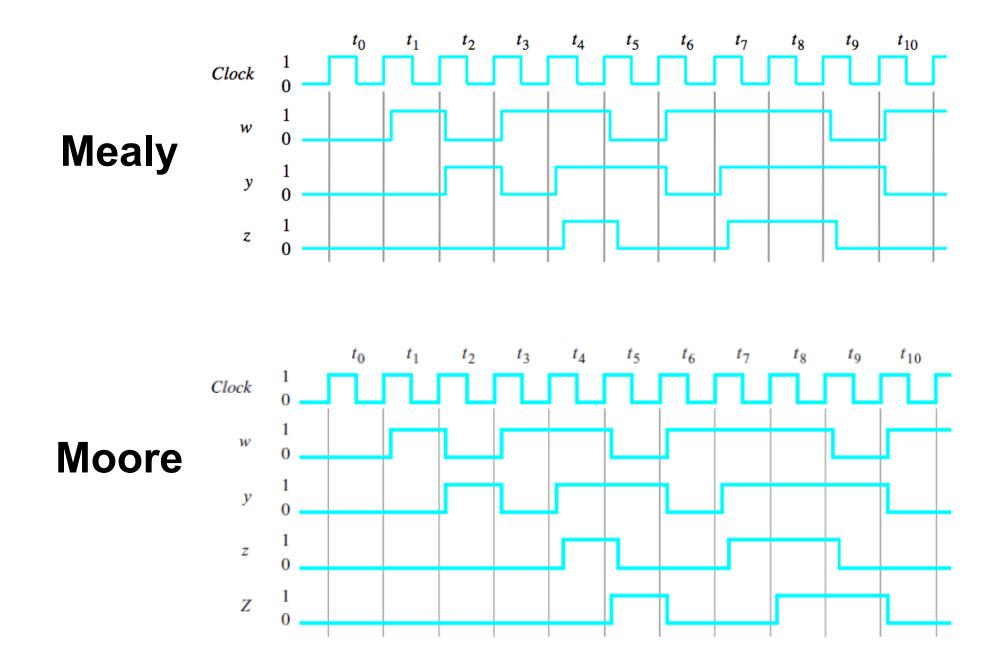

#### **Circuit & Timing Diagram**

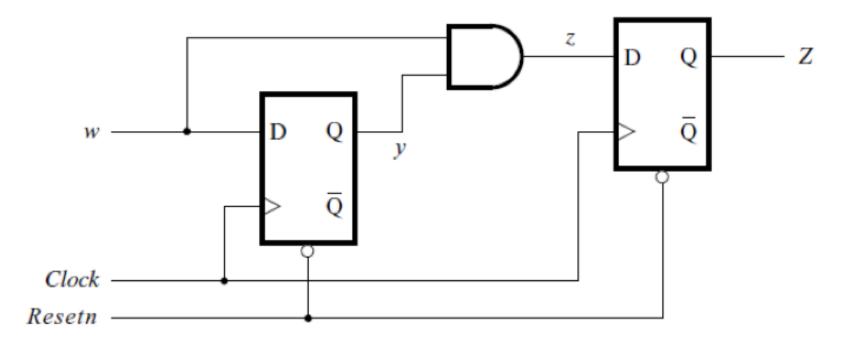

# What if we wanted the output signal to be delayed by 1 clock cycle?

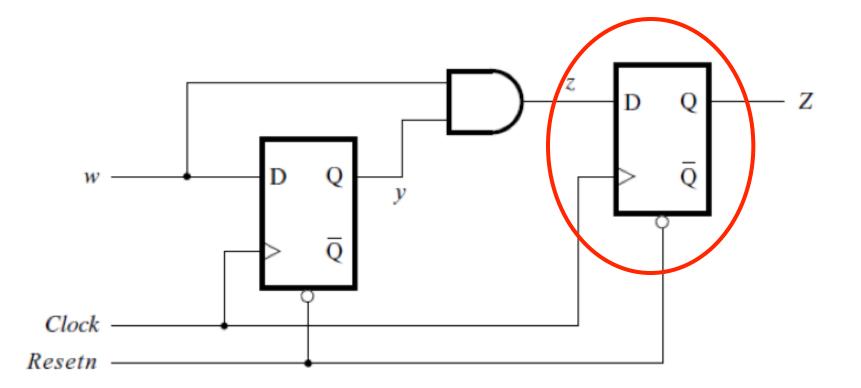

#### **Circuit Implementation of the Modified FSM**

[Figure 6.27a from the textbook]

#### **Circuit Implementation of the Modified FSM**

## This flip-flop delays the output signal by one clock cycle

[Figure 6.27a from the textbook]

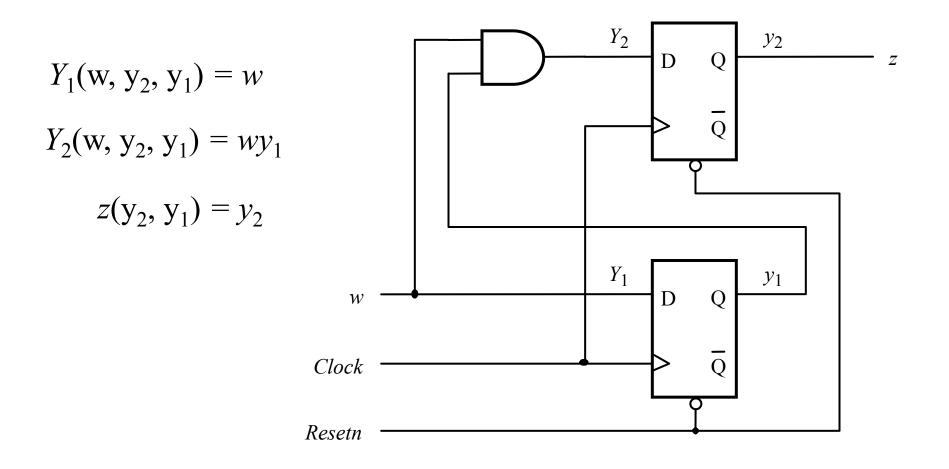

### We Have Seen This Diagram Before

[Figure 6.17 from the textbook]

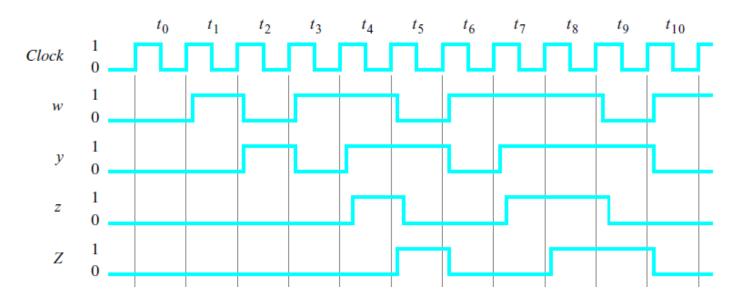

#### **Circuit & Timing Diagram**

(a) Circuit

<sup>[</sup> Figure 6.27 from the textbook ]

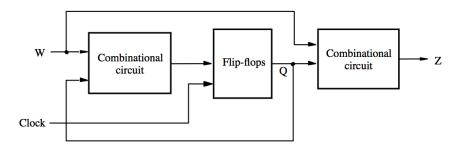

#### The general form of a synchronous sequential circuit

[Figure 6.1 from the textbook]

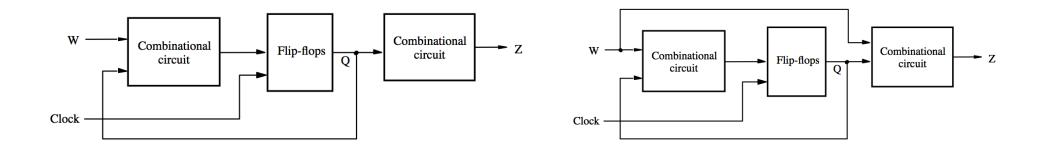

#### **Moore Type**

#### **Mealy Type**

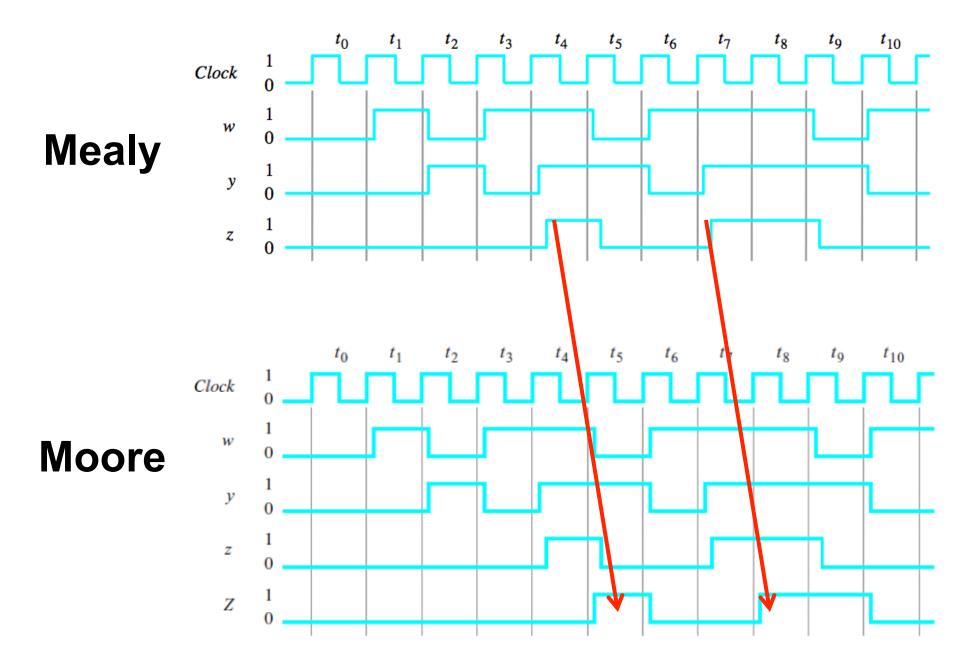

#### Moore

#### Mealy

Mealy

Notice that the output of the Moore machine is delayed by one clock cycle

#### **Questions?**

#### THE END