# **CprE 281: Digital Logic**

Instructor: Alexander Stoytchev

http://www.ece.iastate.edu/~alexs/classes/

### **Registers and Counters**

CprE 281: Digital Logic Iowa State University, Ames, IA Copyright © Alexander Stoytchev

#### **Administrative Stuff**

- The second midterm is this Friday.

- Homework 8 is due today.

- Homework 9 is out. It is due on Mon Nov 5.

- No HW due next Monday

#### **Administrative Stuff**

Midterm Exam #2

When: Friday October 26 @ 4pm.

Where: This classroom

What: Chapters 1, 2, 3, 4 and 5.1-5.8

The exam will be open book and open notes (you can bring up to 3 pages of handwritten notes).

# Registers

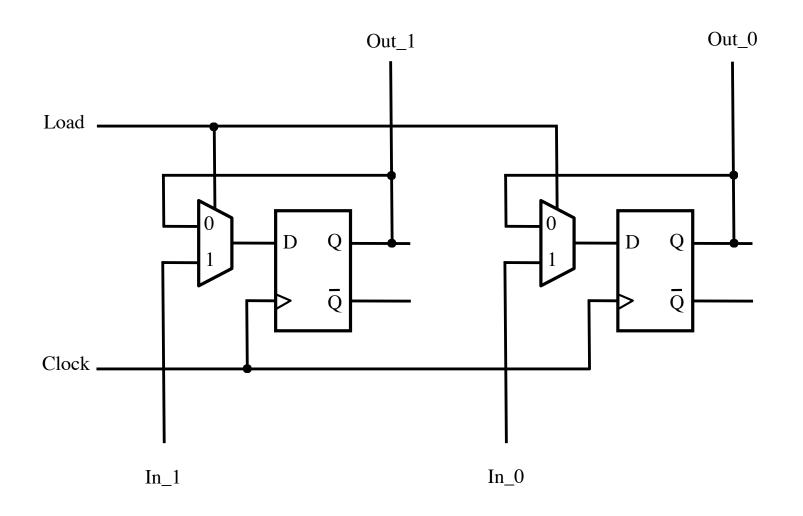

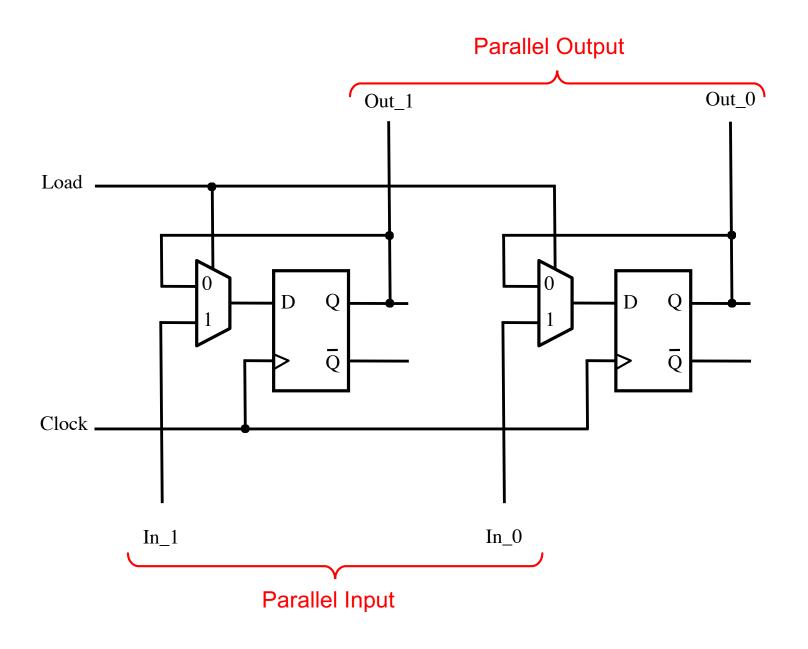

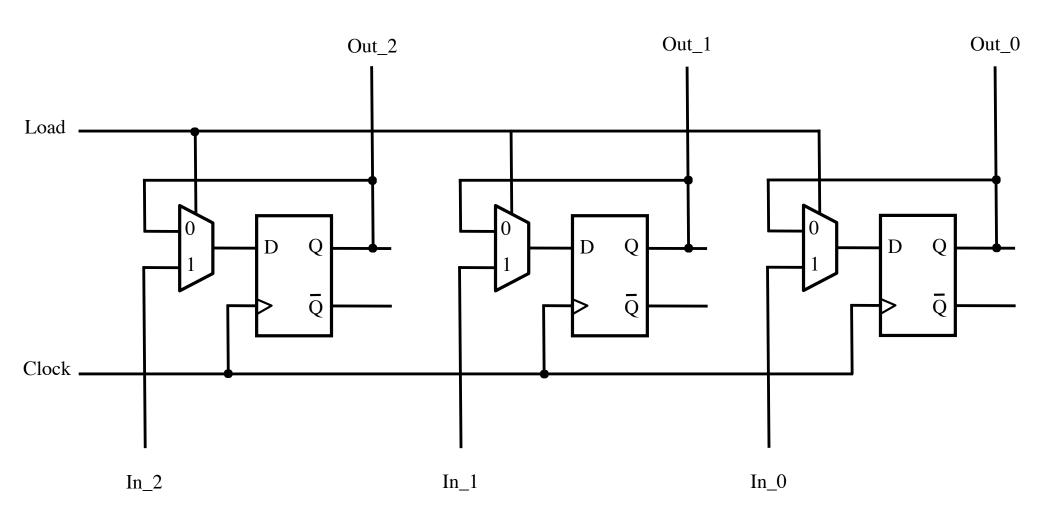

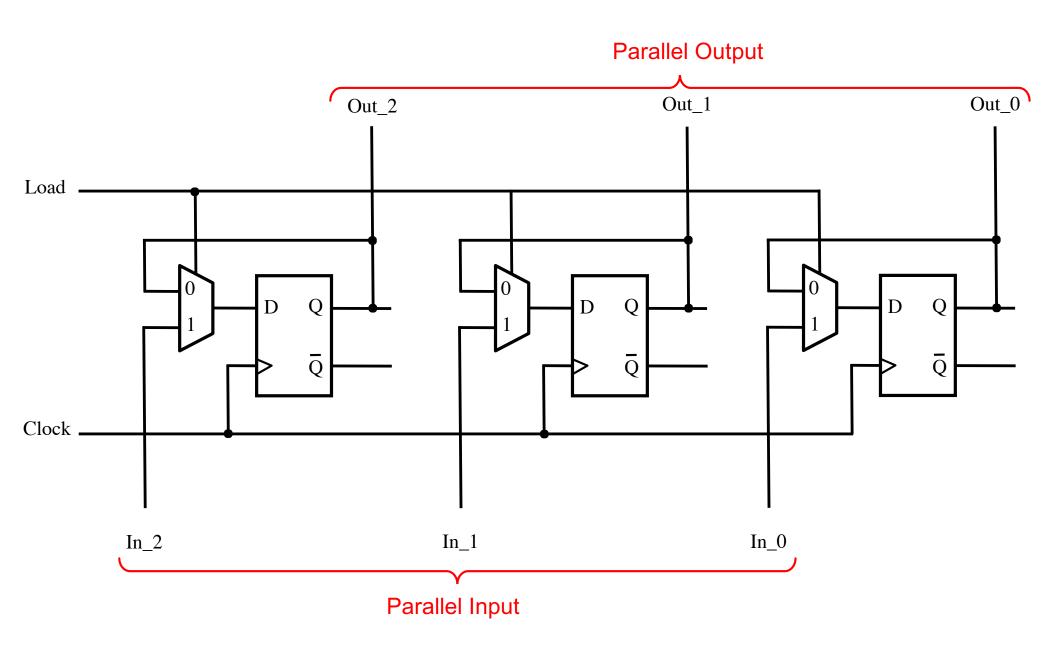

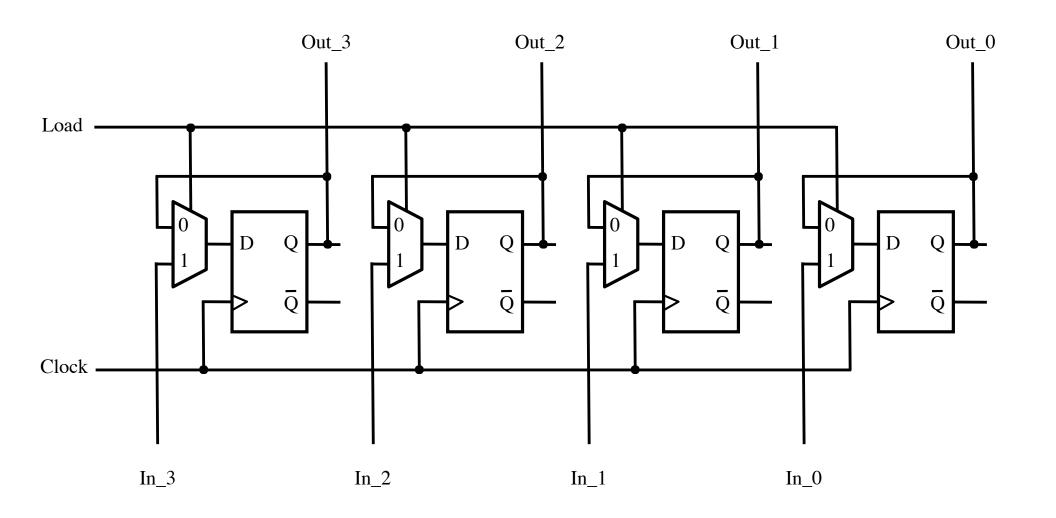

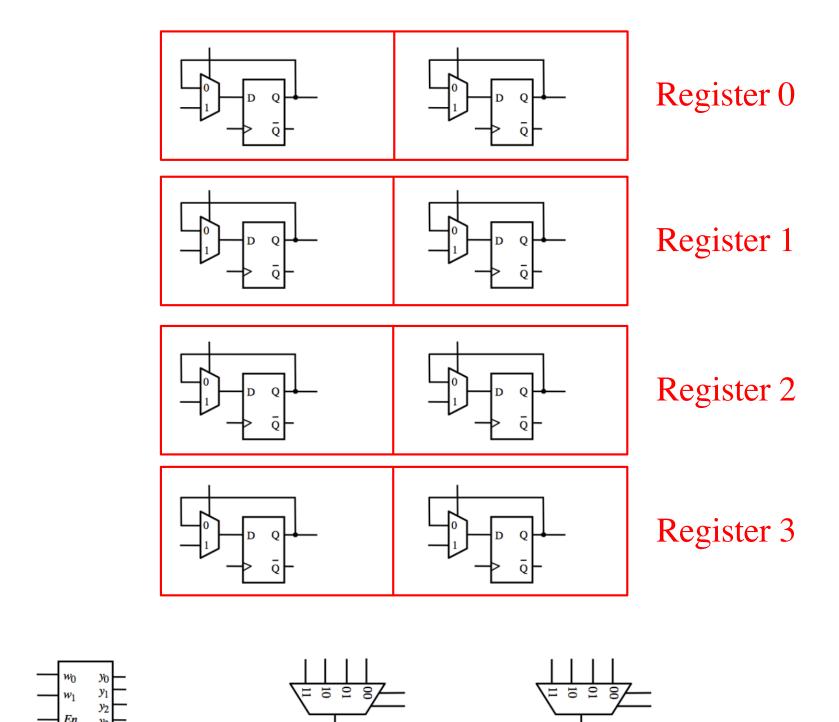

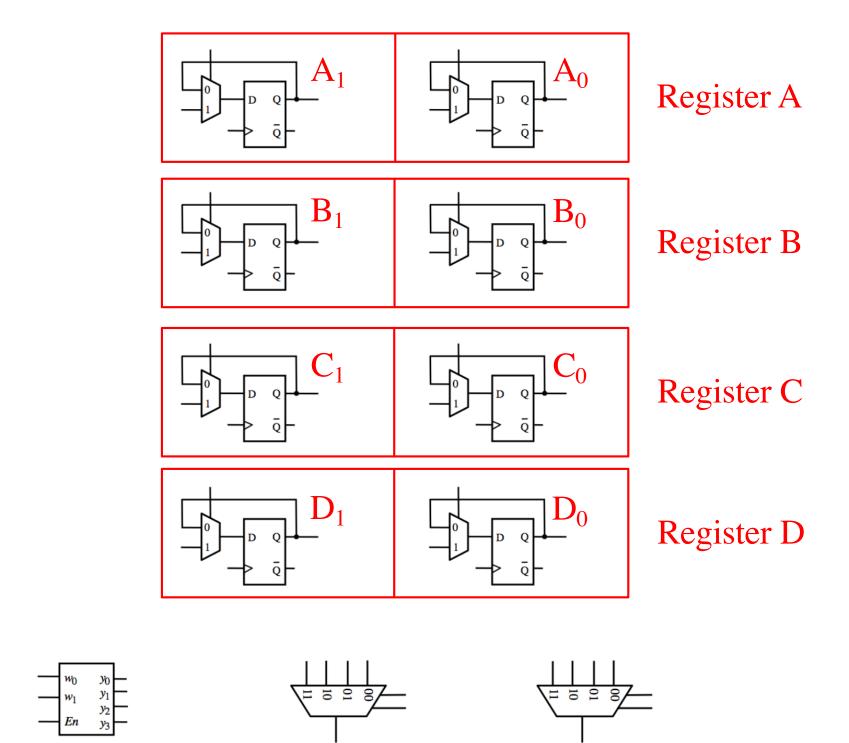

# Register (Definition)

An n-bit structure consisting of flip-flops

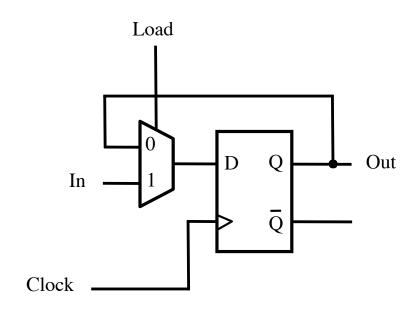

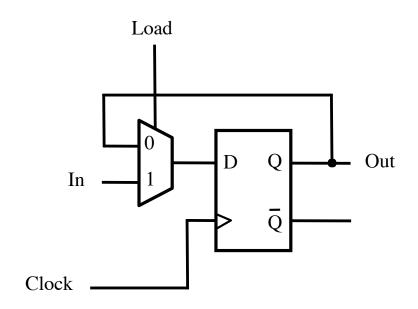

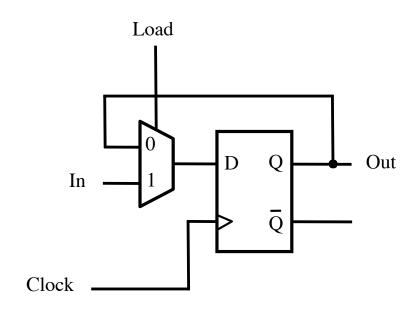

The 2-to-1 multiplexer is used to select whether to load a new value into the D flip-flop or to retain the old value.

The output of this circuit is the Q output of the flip-flop.

If Load = 0, then retain the old value.

If Load = 1, then load the new value from In.

Notice that all flip-flops are on the same clock cycle.

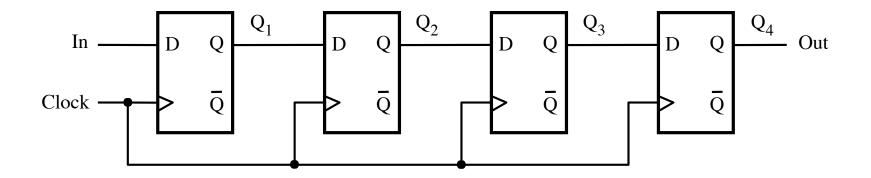

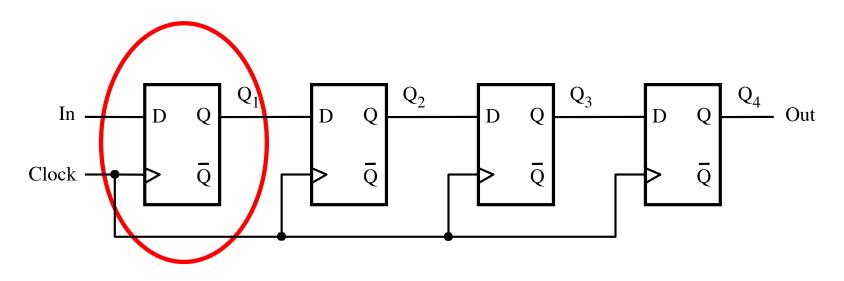

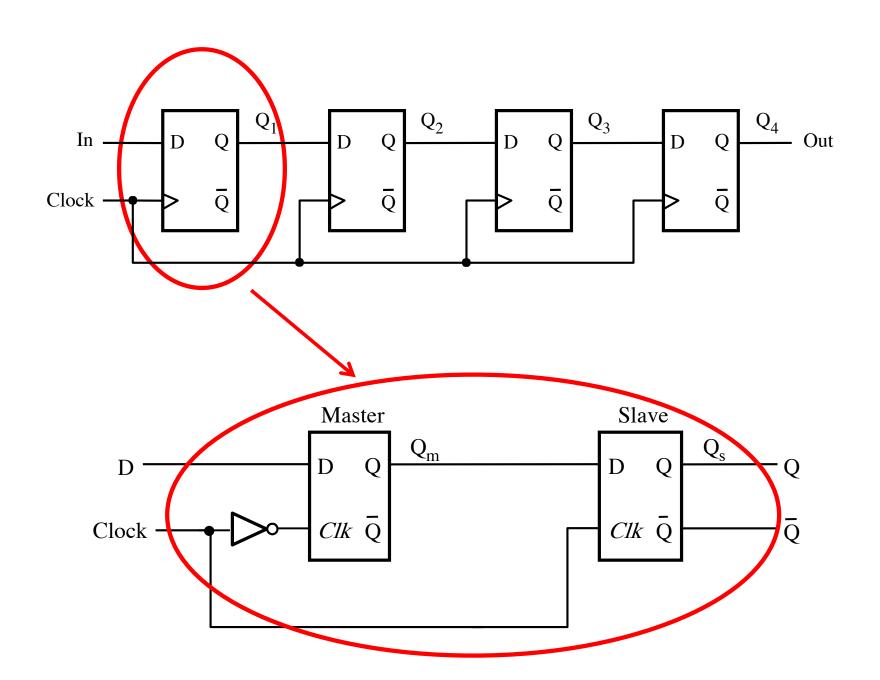

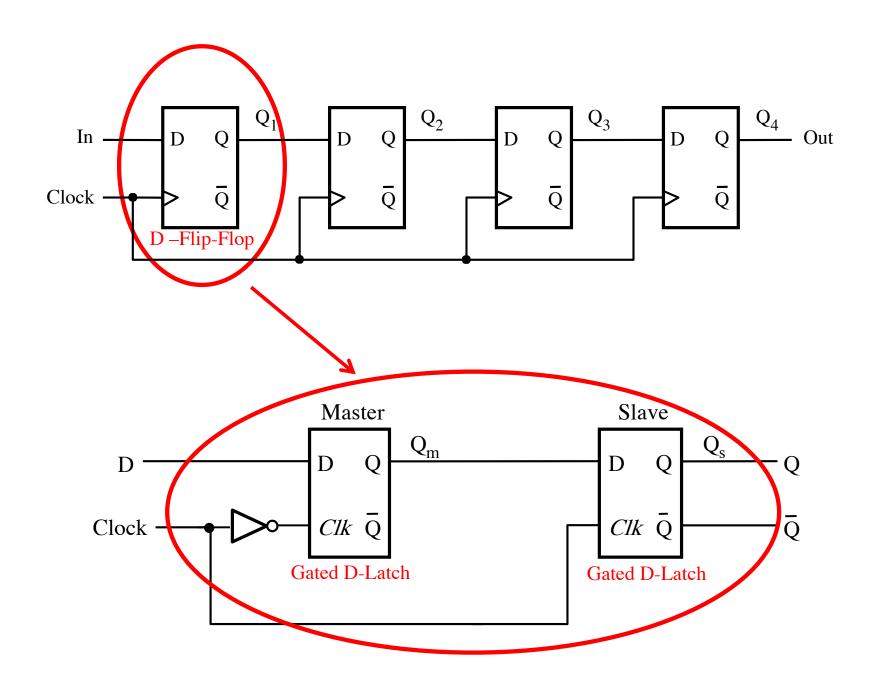

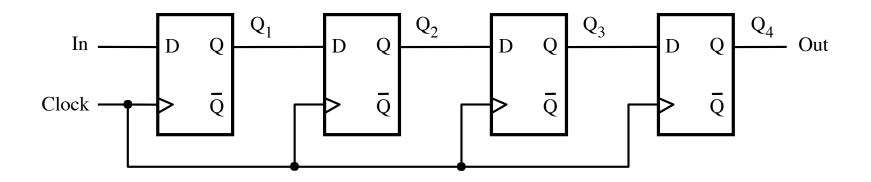

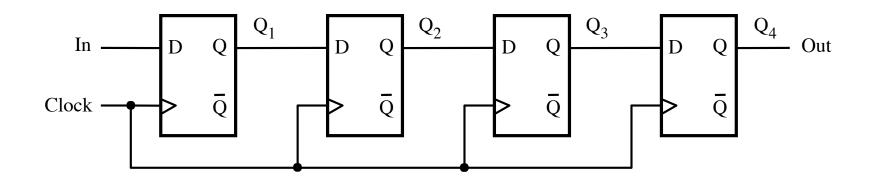

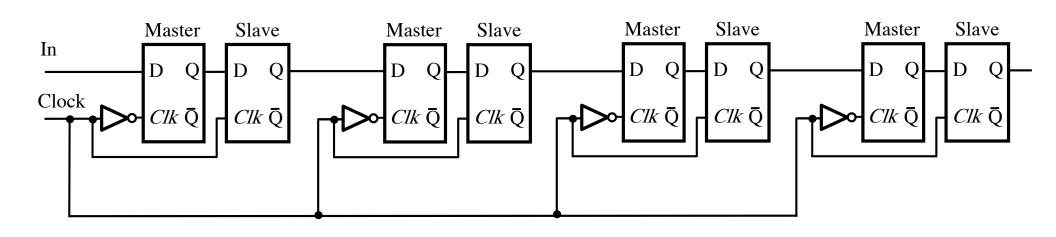

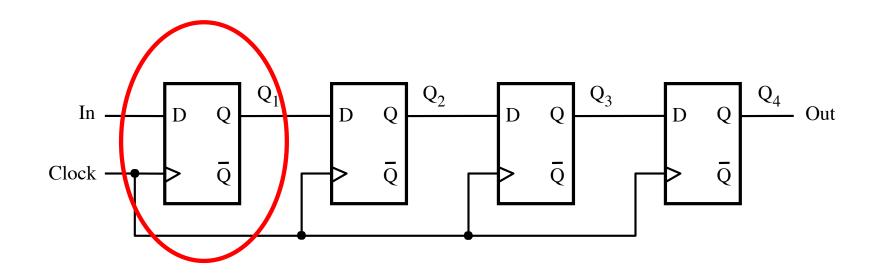

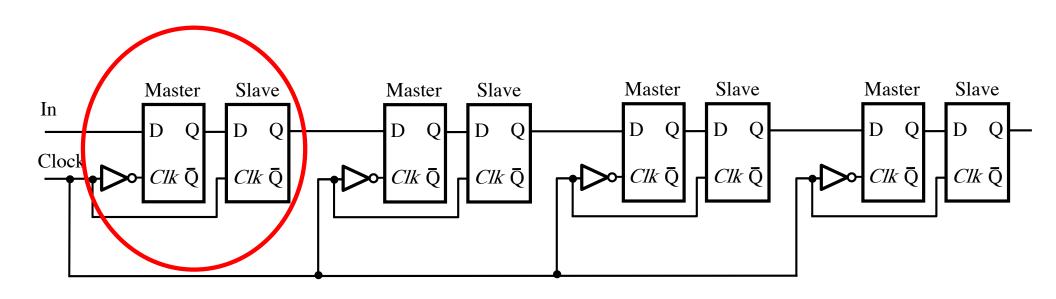

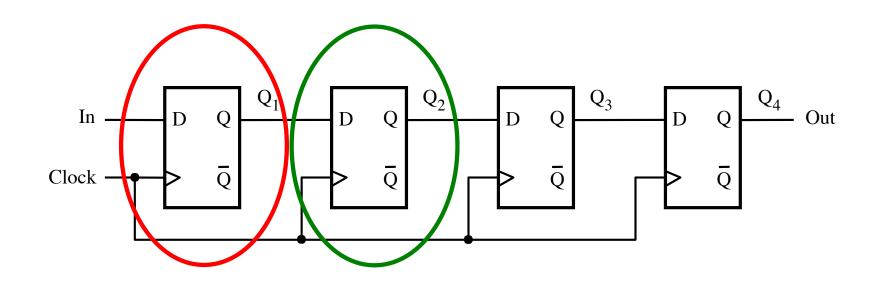

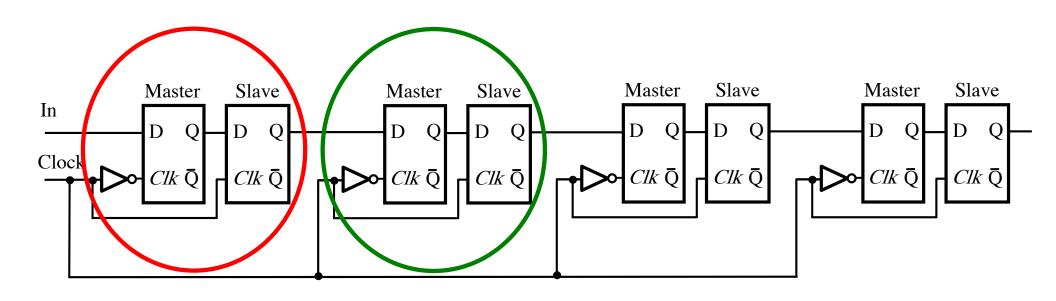

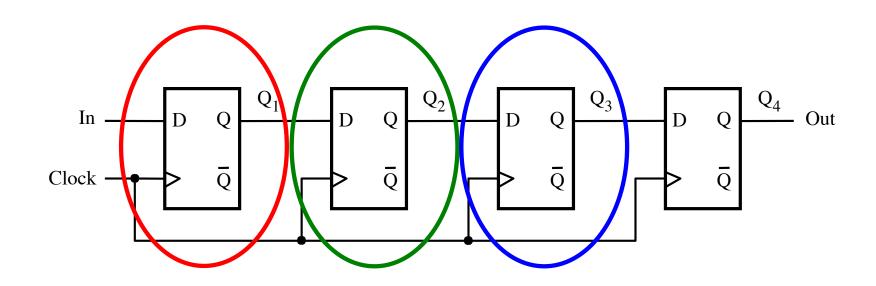

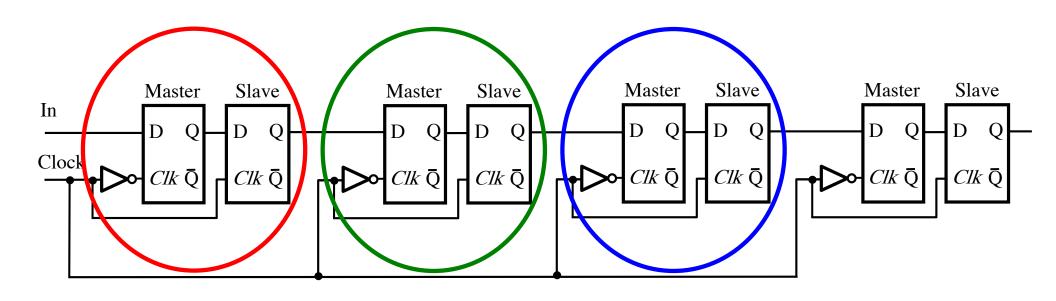

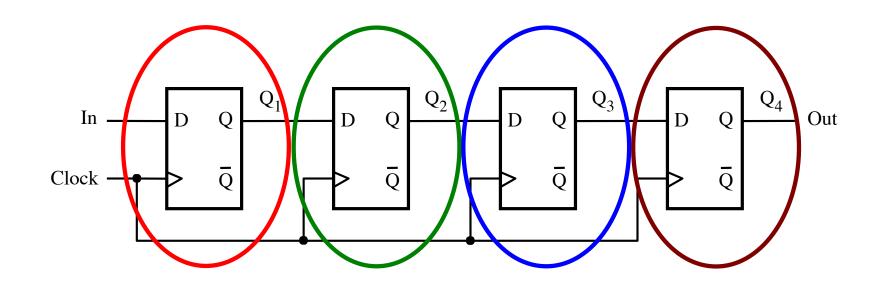

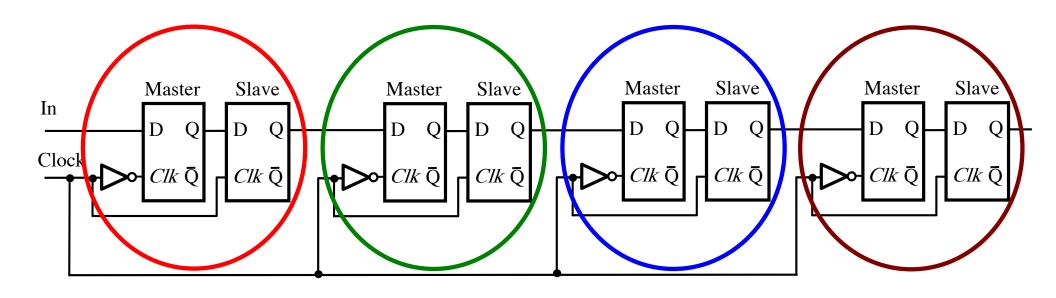

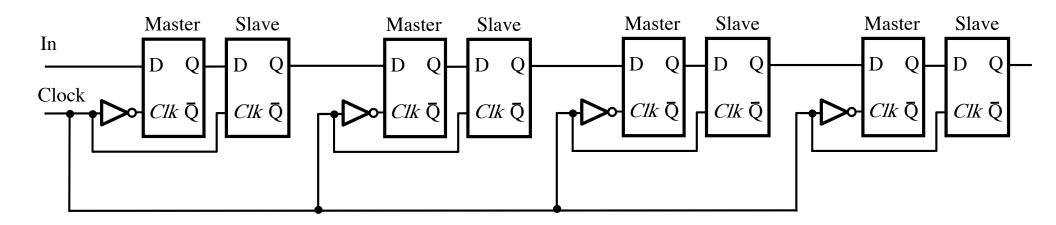

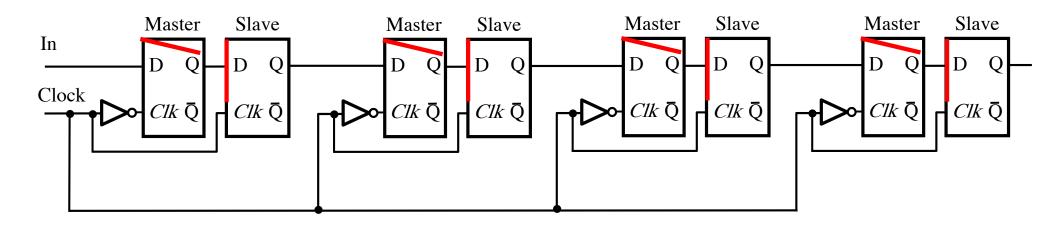

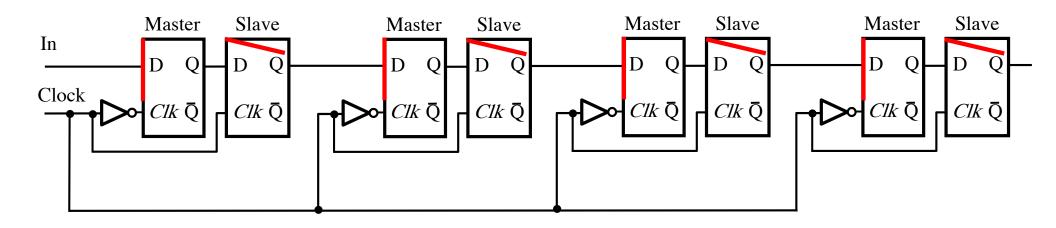

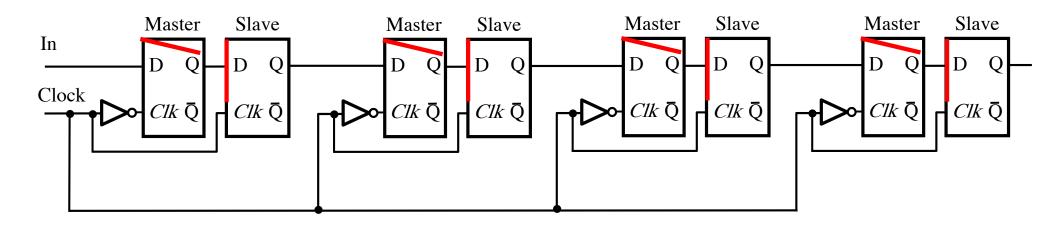

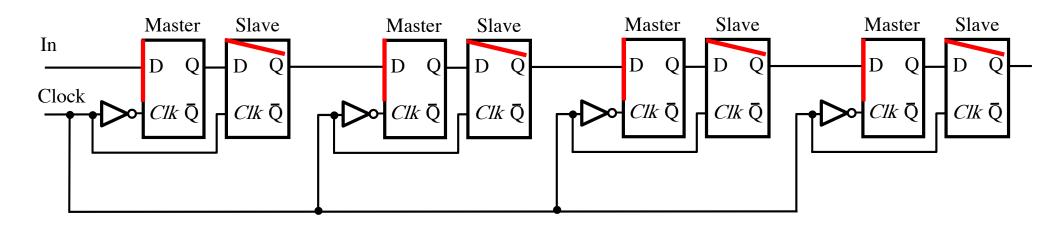

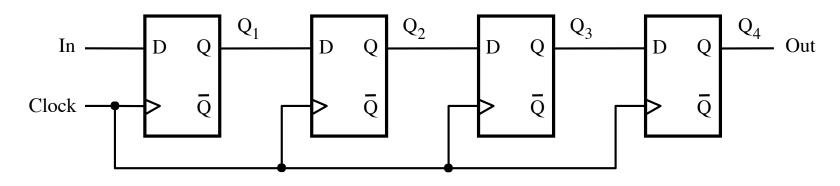

# **Shift Register**

Positive-edge-triggered D Flip-Flop

Clock

Clock

Clock

(a) Circuit

In

$$Q_1$$

$Q_2$   $Q_3$   $Q_4$  = Out  $t_0$  1 0 0 0 0 0  $t_1$  0 1 0 0 0  $t_2$  1 0 1 0 0 0  $t_3$  1 1 0 1 0  $t_4$  1 1 1 0 1  $t_5$  0 1 1 1 0  $t_6$  0 0 0 1 1 1  $t_7$  0 0 0 0 1 1

(b) A sample sequence

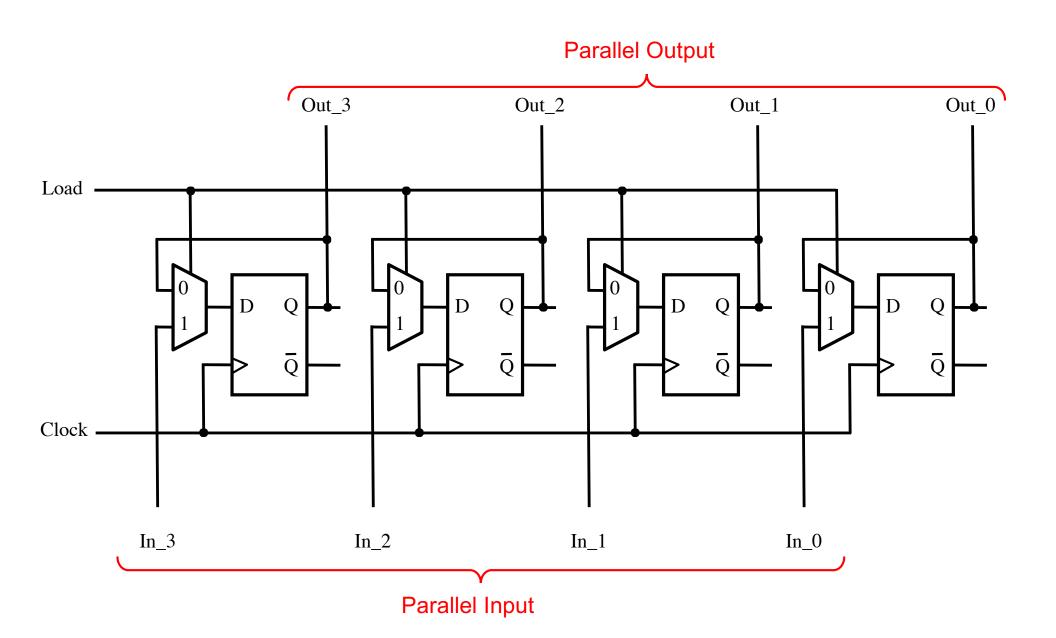

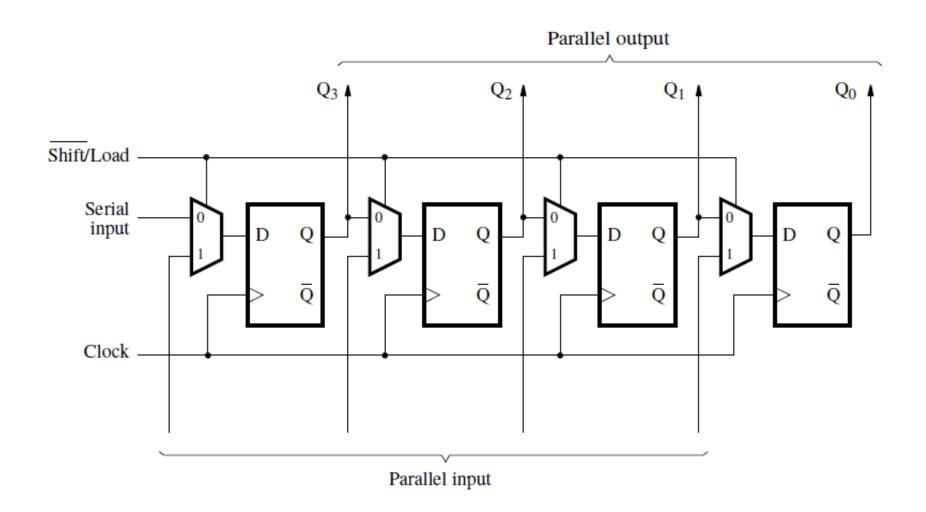

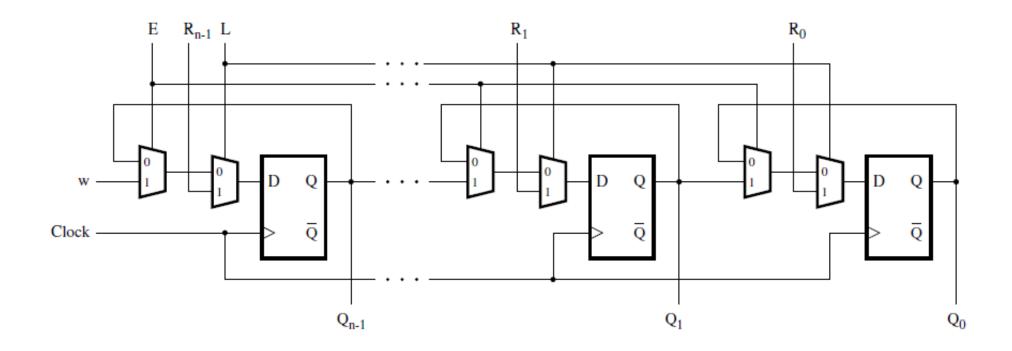

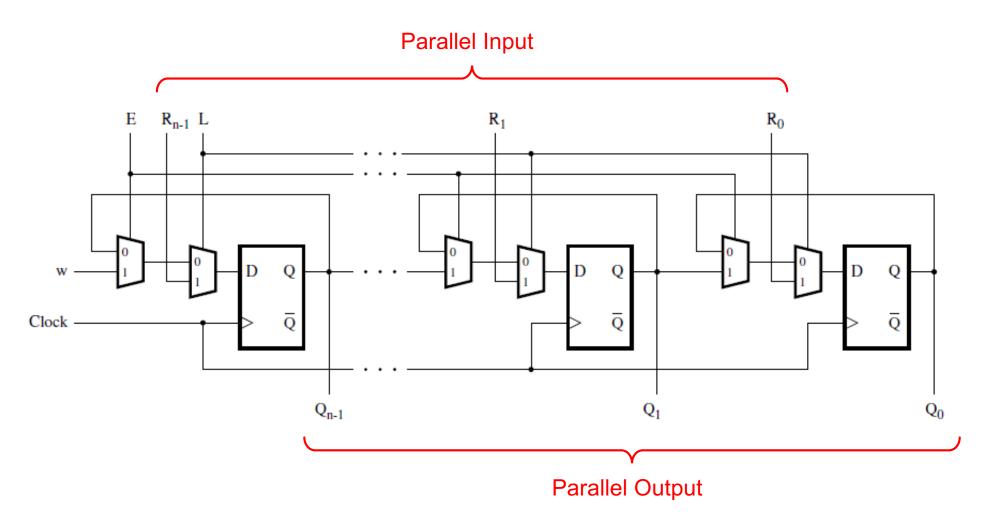

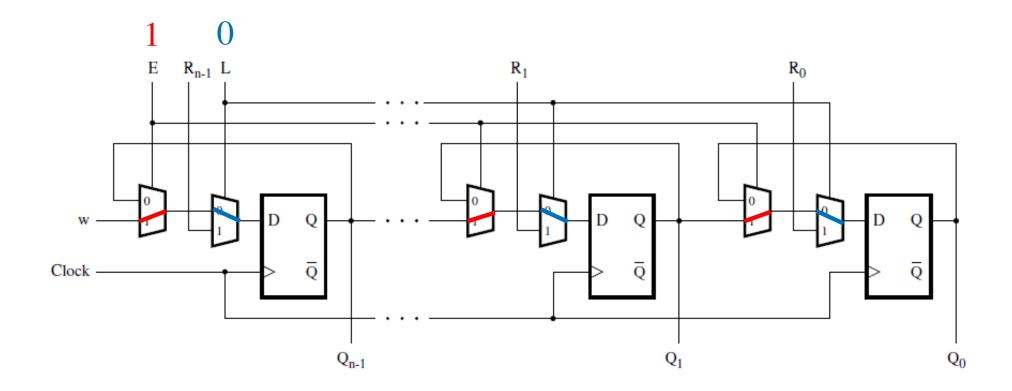

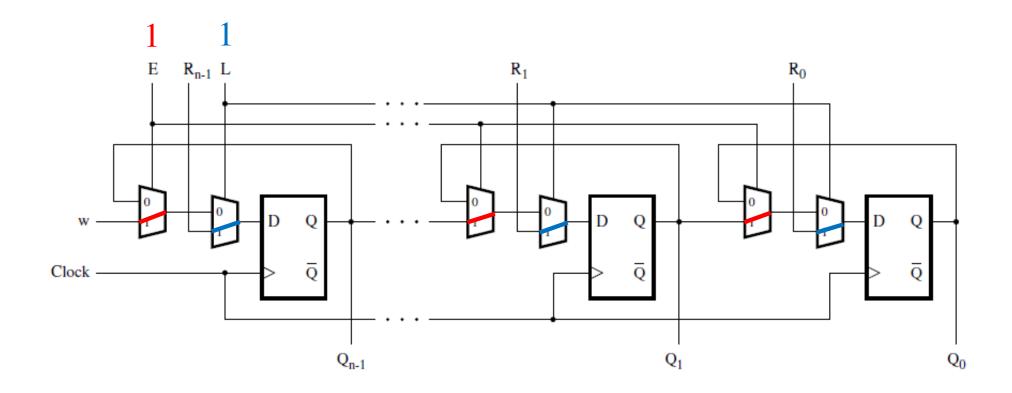

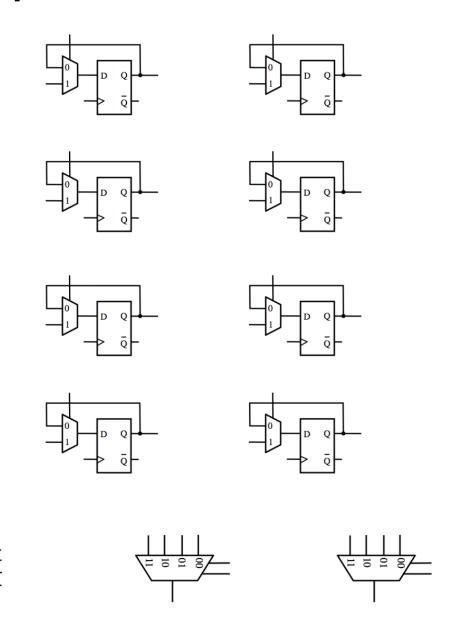

# Parallel-Access Shift Register

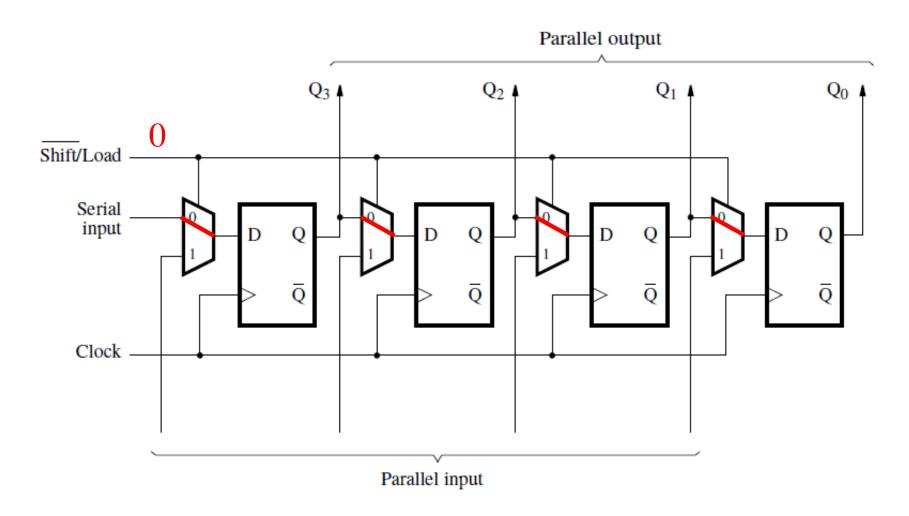

#### Parallel-access shift register

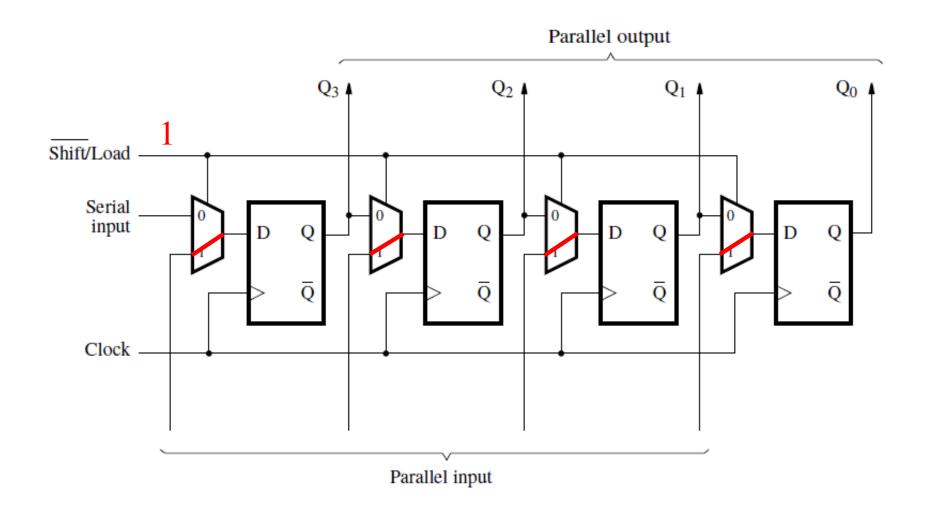

#### Parallel-access shift register

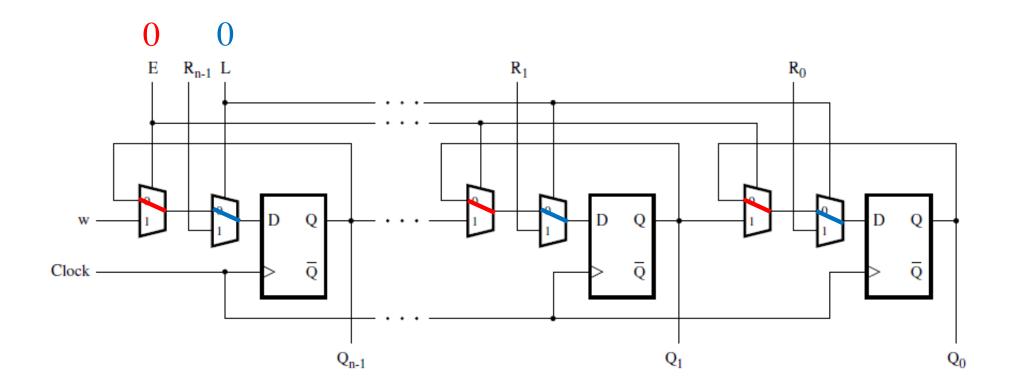

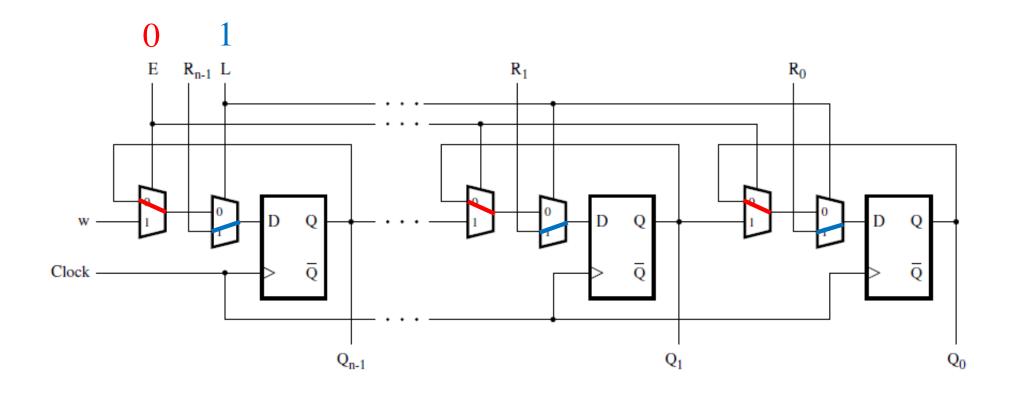

When Load=0, this behaves like a shift register.

### Parallel-access shift register

When Load=1, this behaves like a parallel-access register.

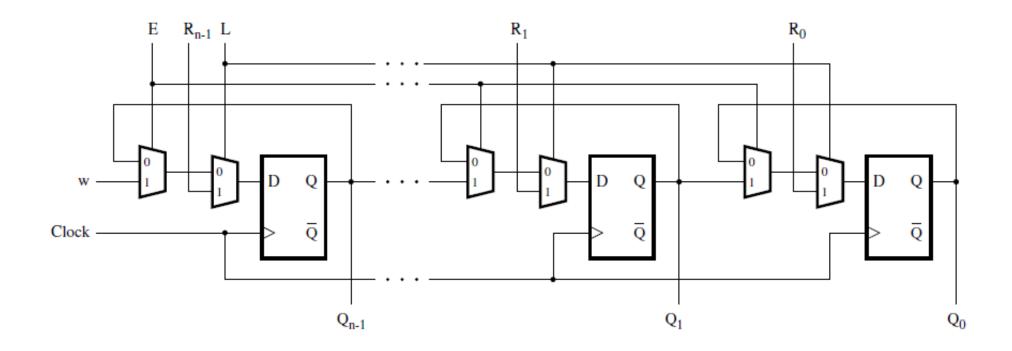

## Shift Register With Parallel Load and Enable

The directions of the input and output lines are switched relative to the previous slides.

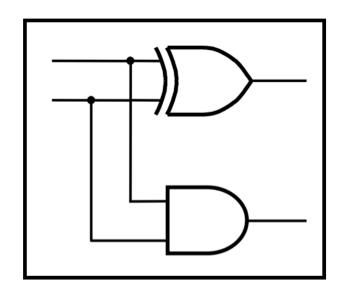

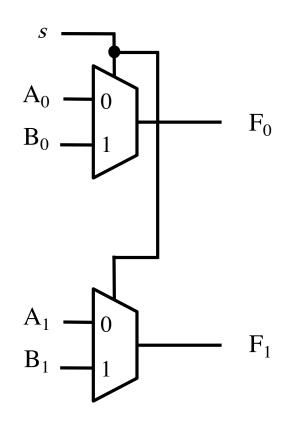

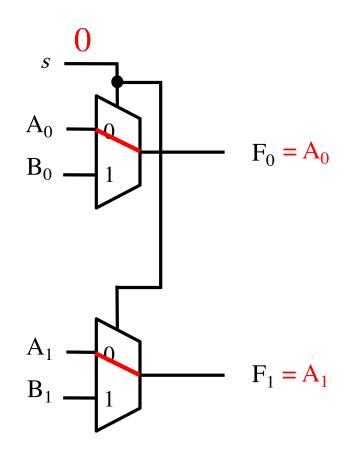

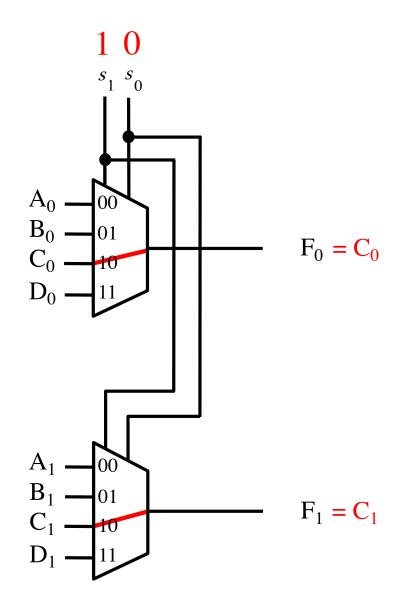

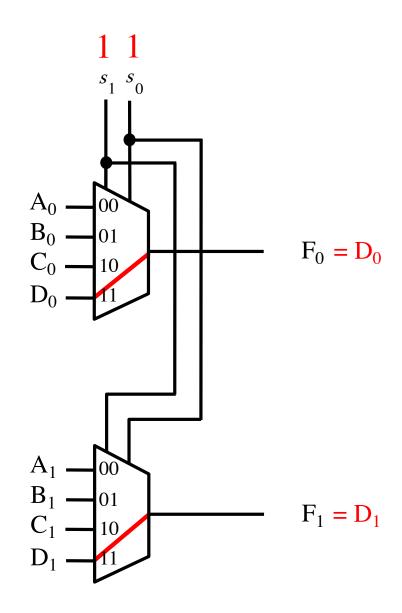

# Multiplexer Tricks (select one of two 2-bit numbers)

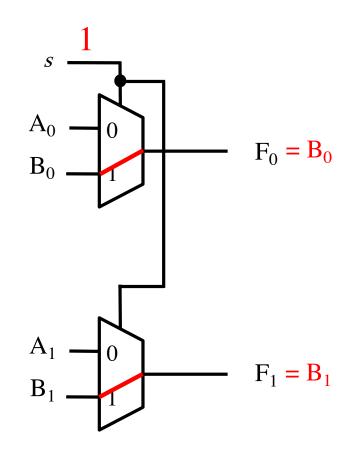

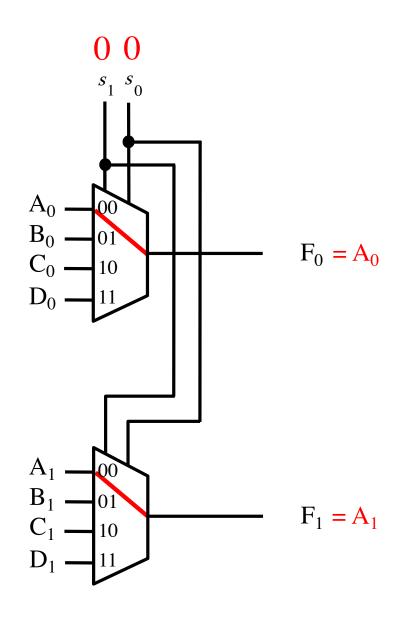

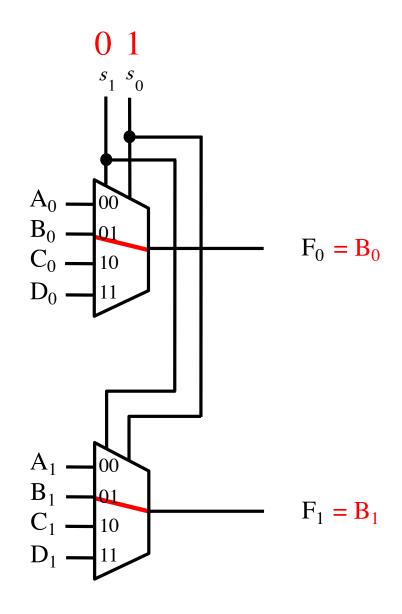

### Select Either $A=A_1A_0$ or $B=B_1B_0$

### Select Either $A=A_1A_0$ or $B=B_1B_0$

### Select Either $A=A_1A_0$ or $B=B_1B_0$

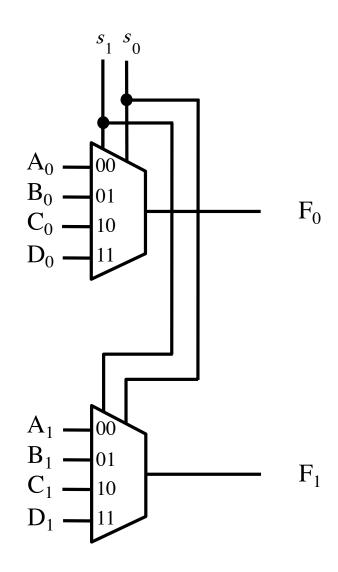

# Multiplexer Tricks (select one of four 2-bit numbers)

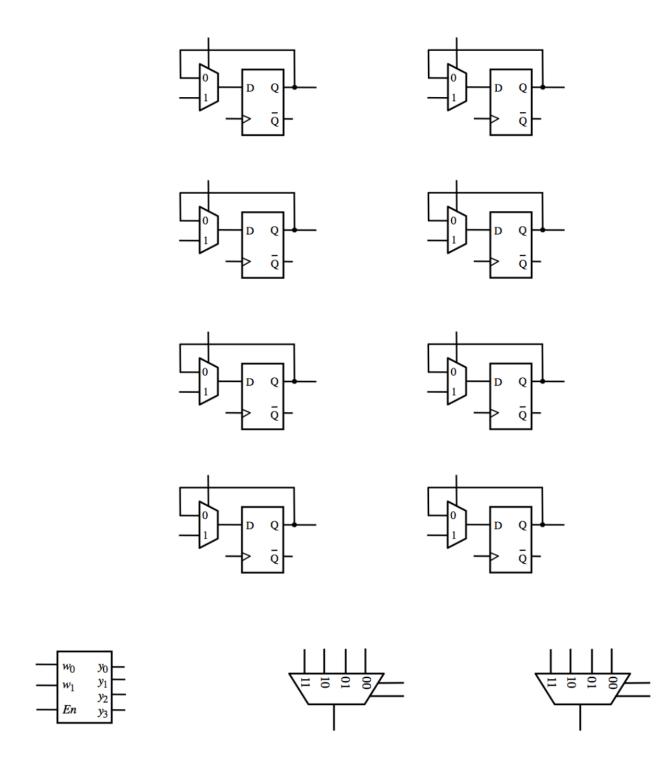

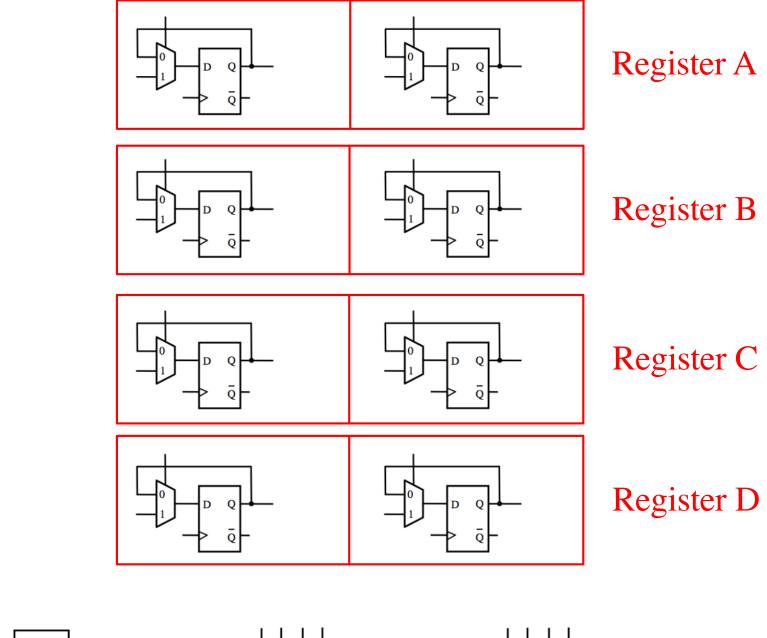

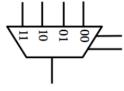

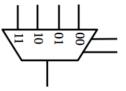

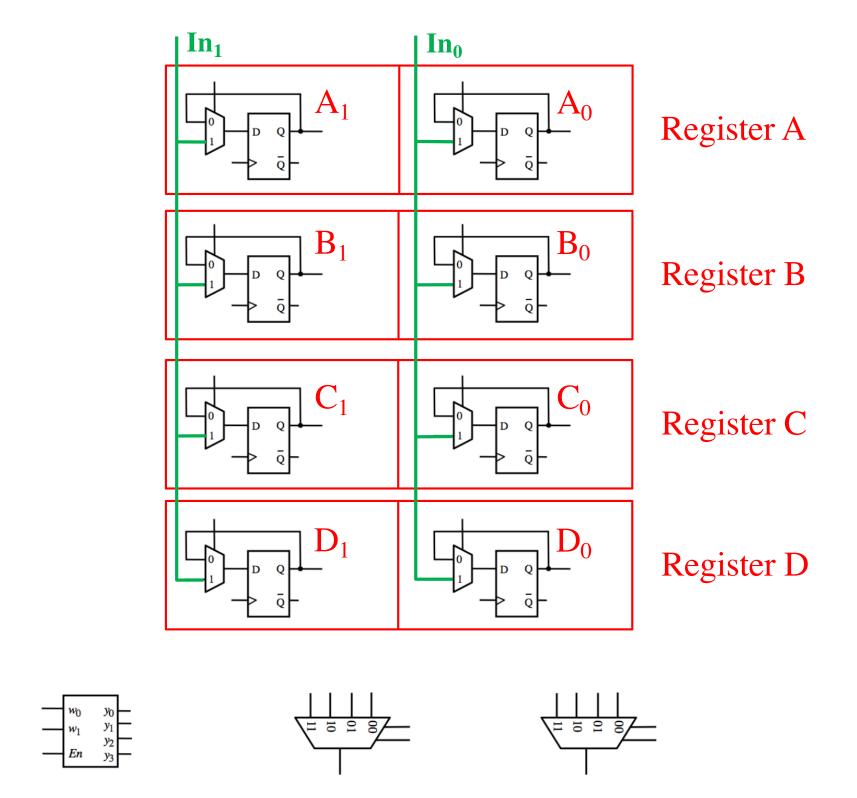

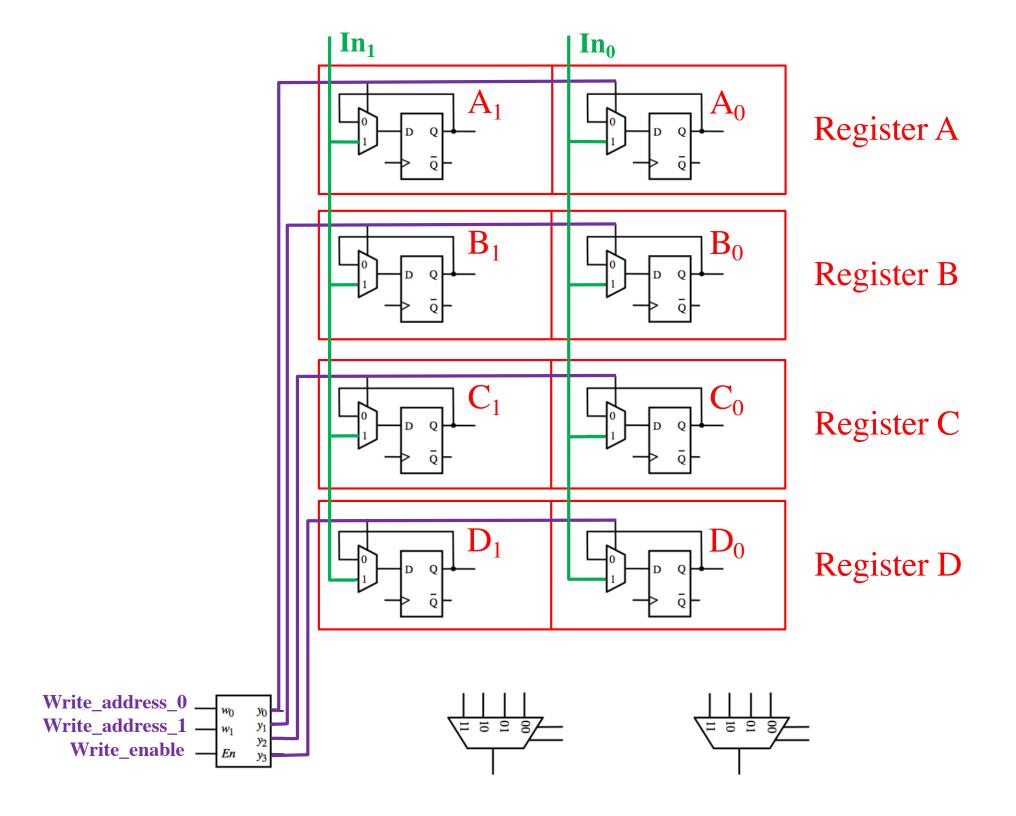

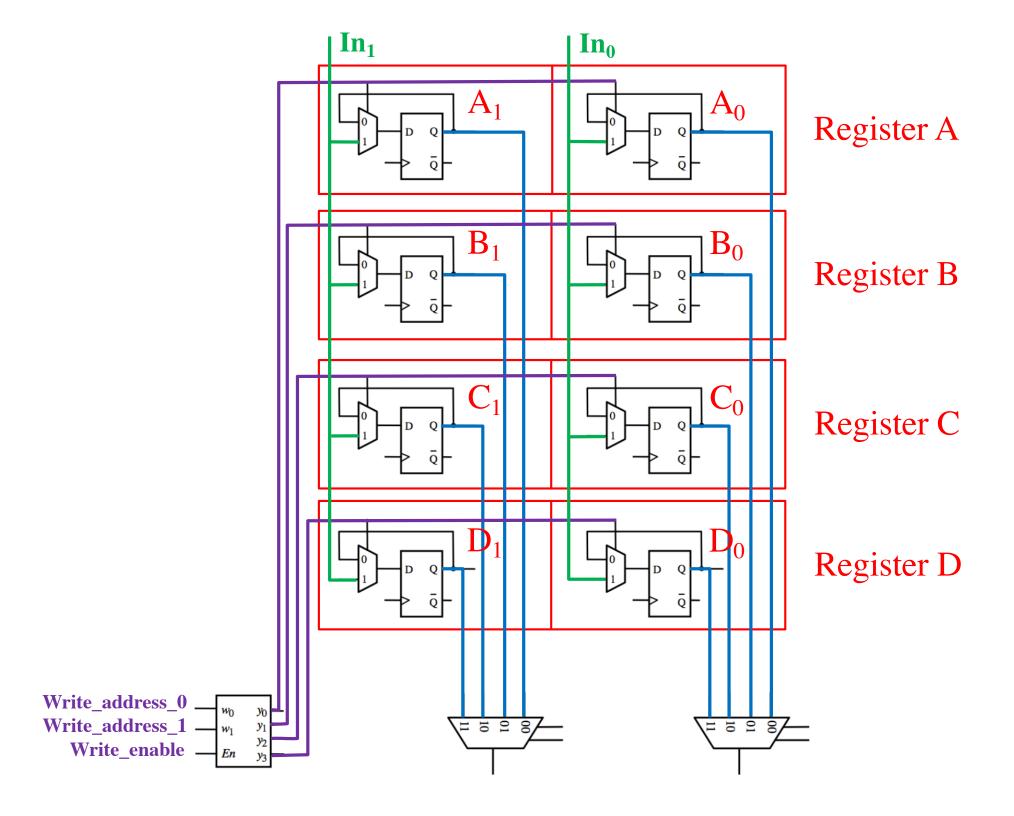

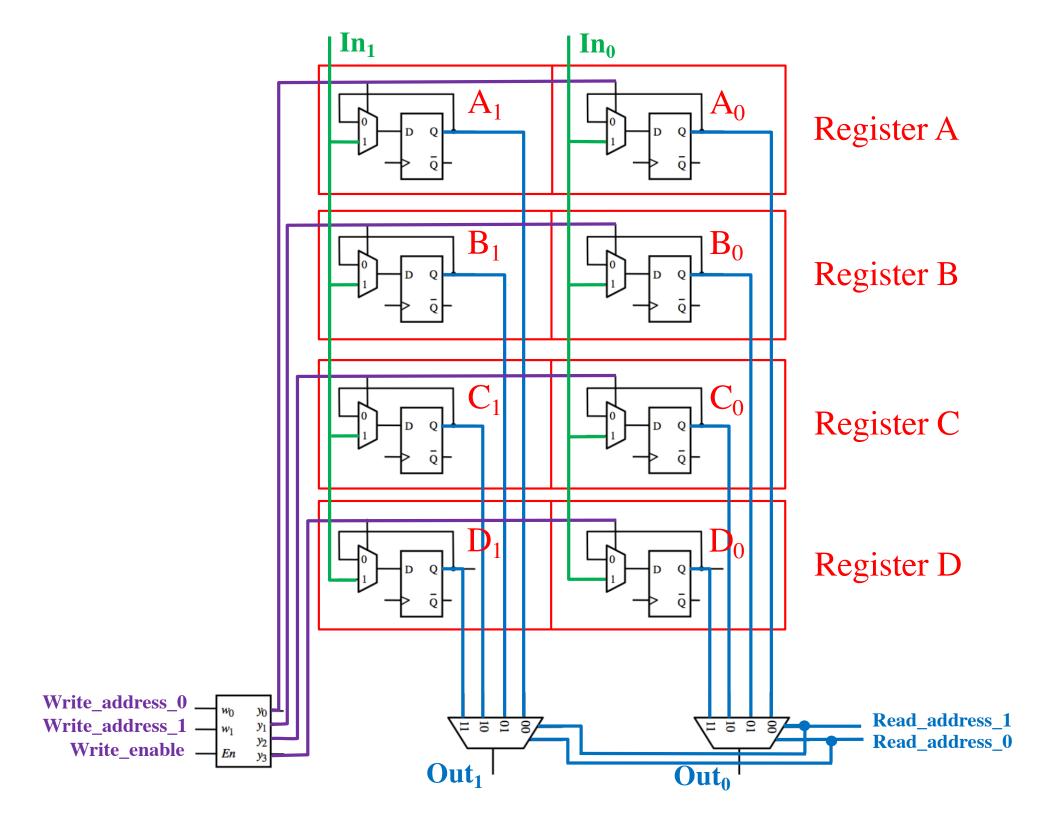

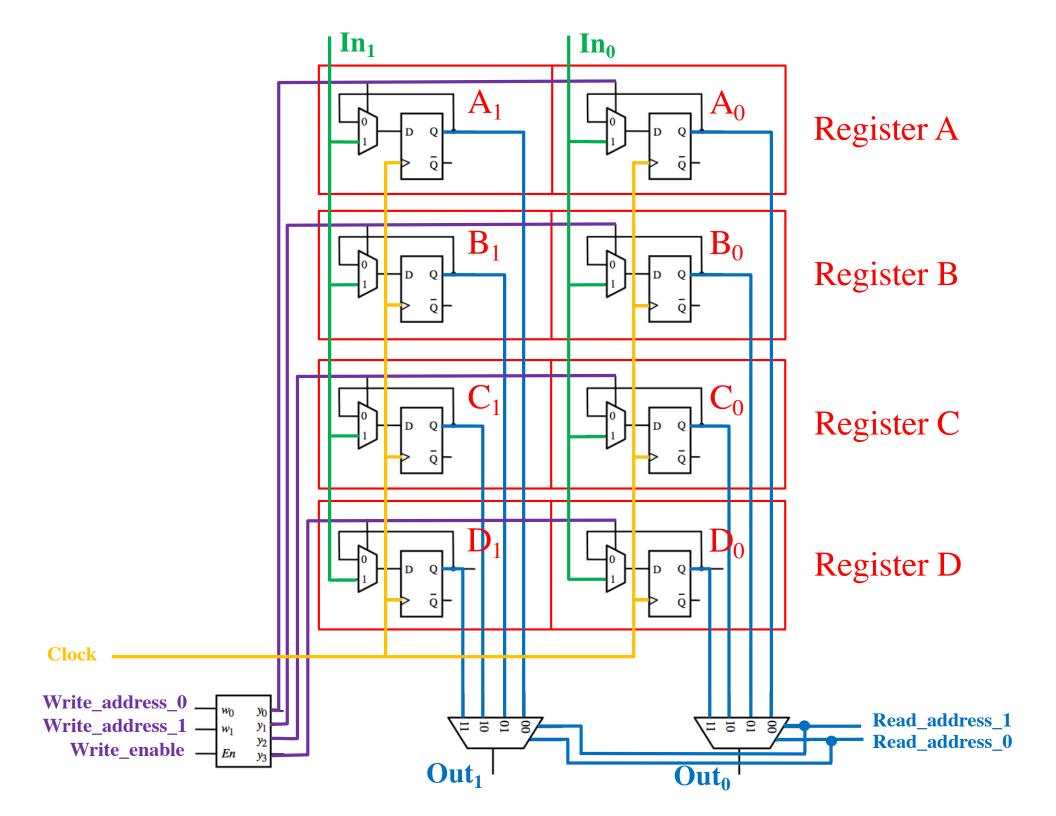

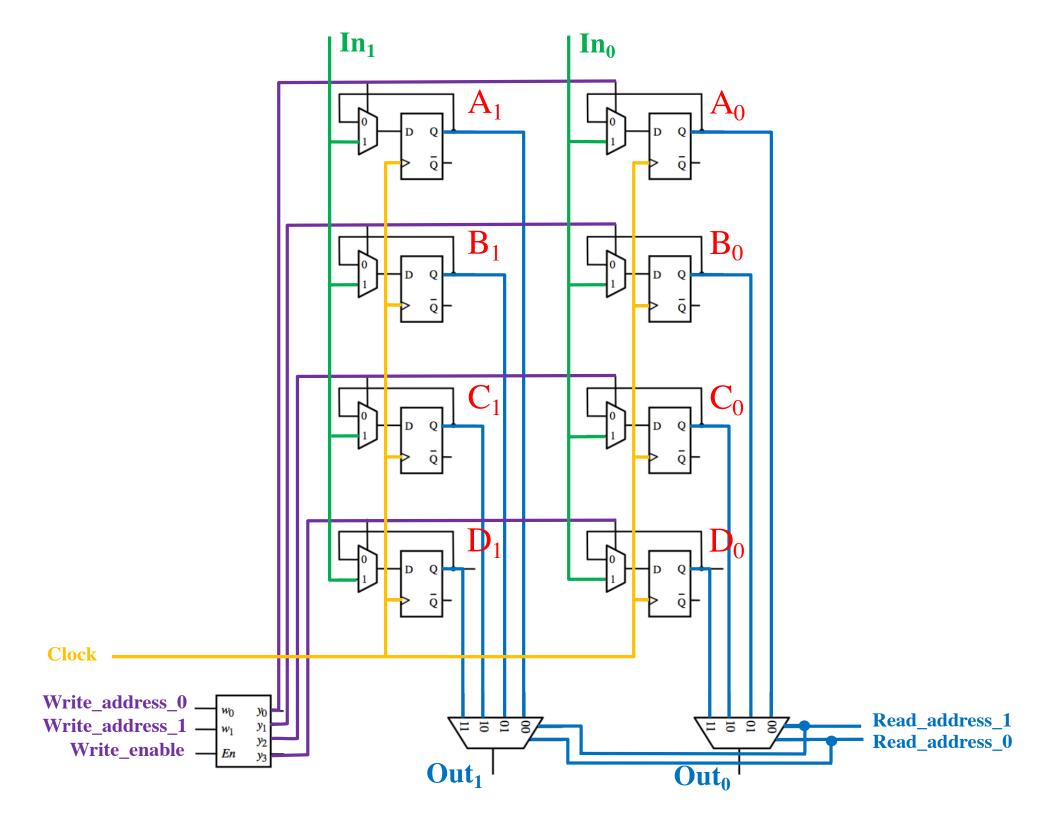

### Register File

# Complete the following circuit diagram to implement a register file with four 2-bit registers, one write port, one read port, and one write enable line.

### **Counters**

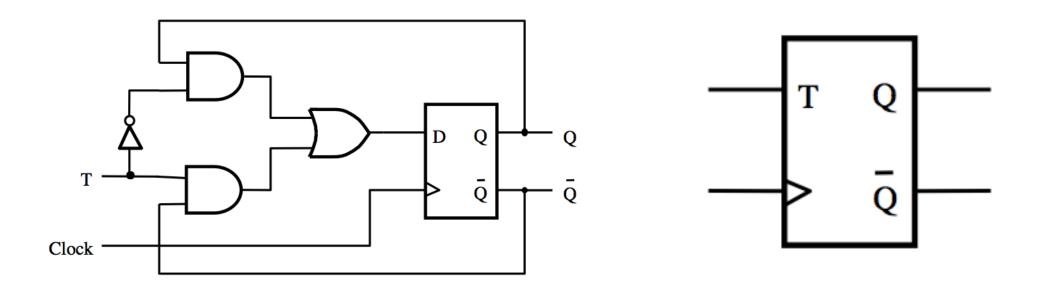

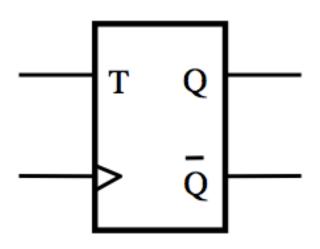

### T Flip-Flop (circuit and graphical symbol)

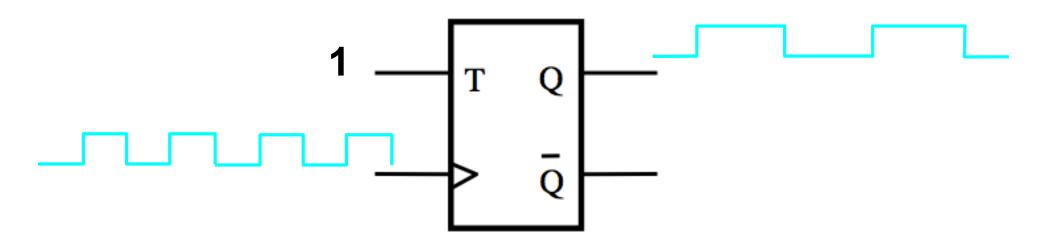

### The output of the T Flip-Flop divides the frequency of the clock by 2

### The output of the T Flip-Flop divides the frequency of the clock by 2

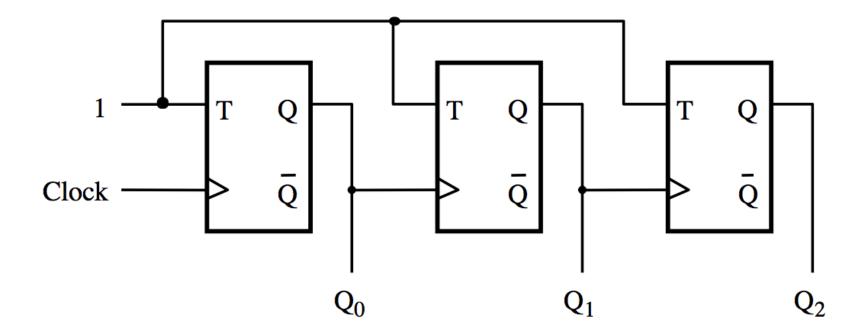

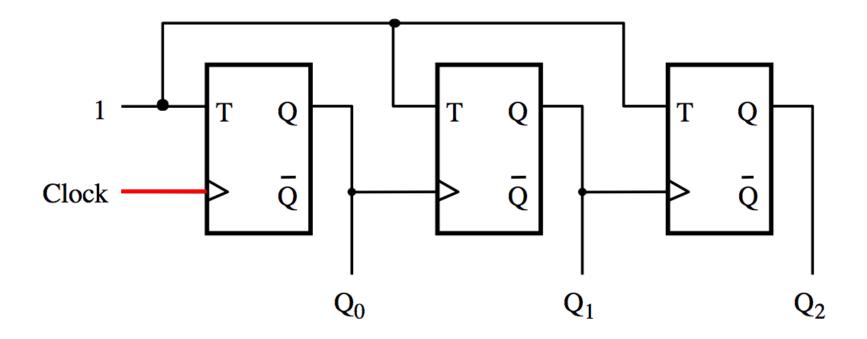

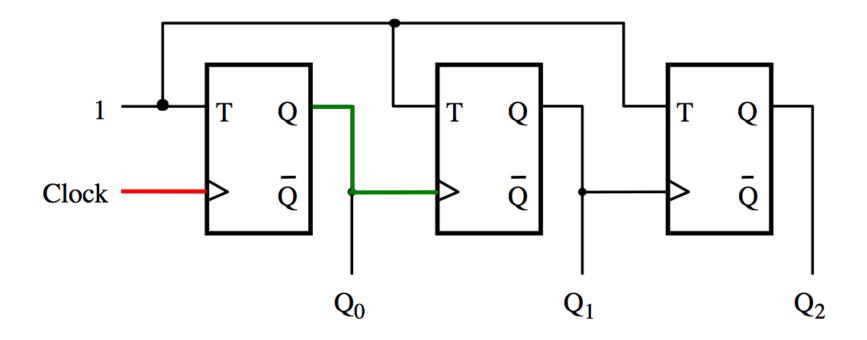

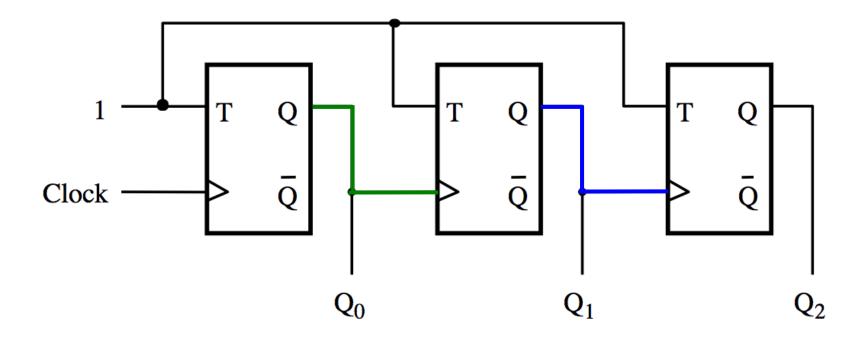

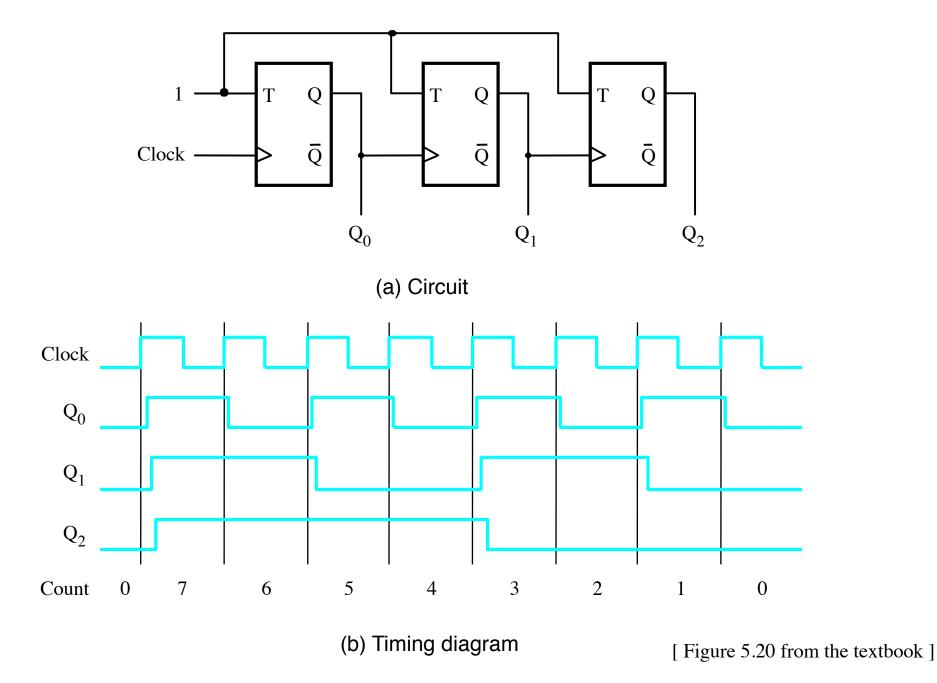

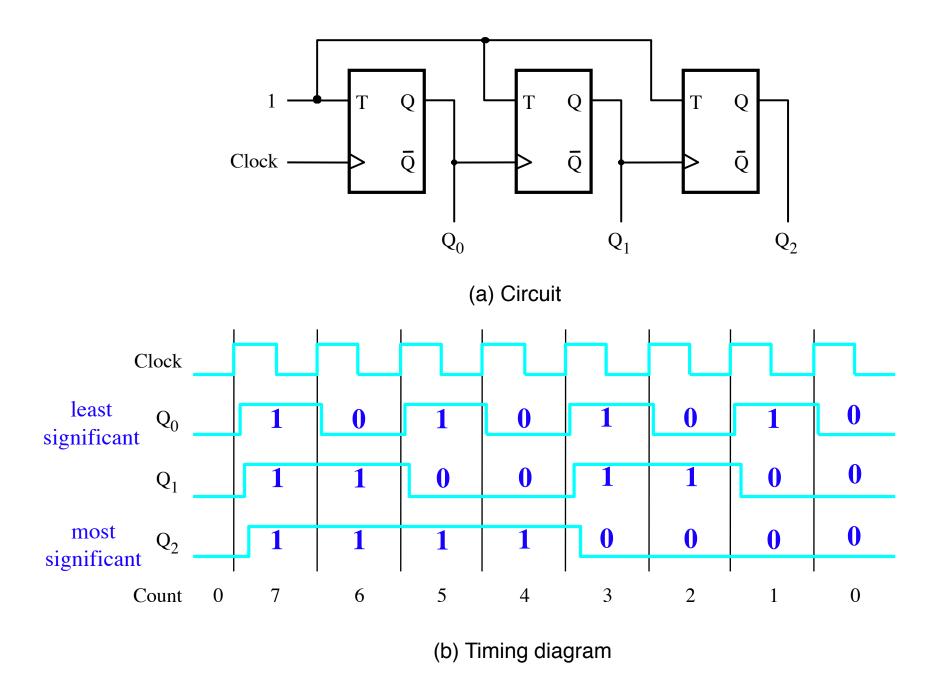

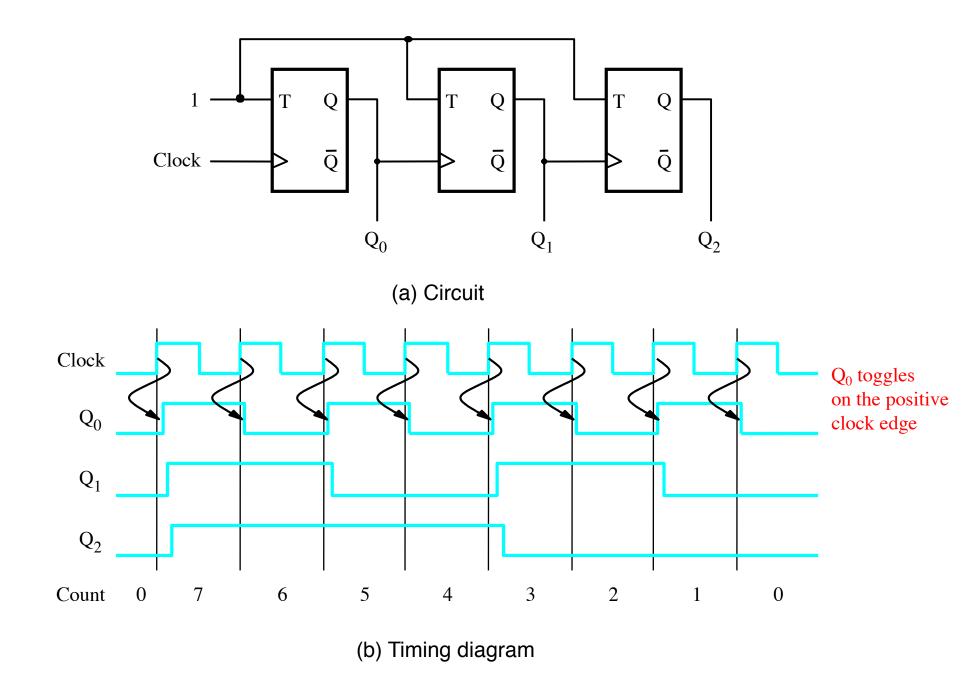

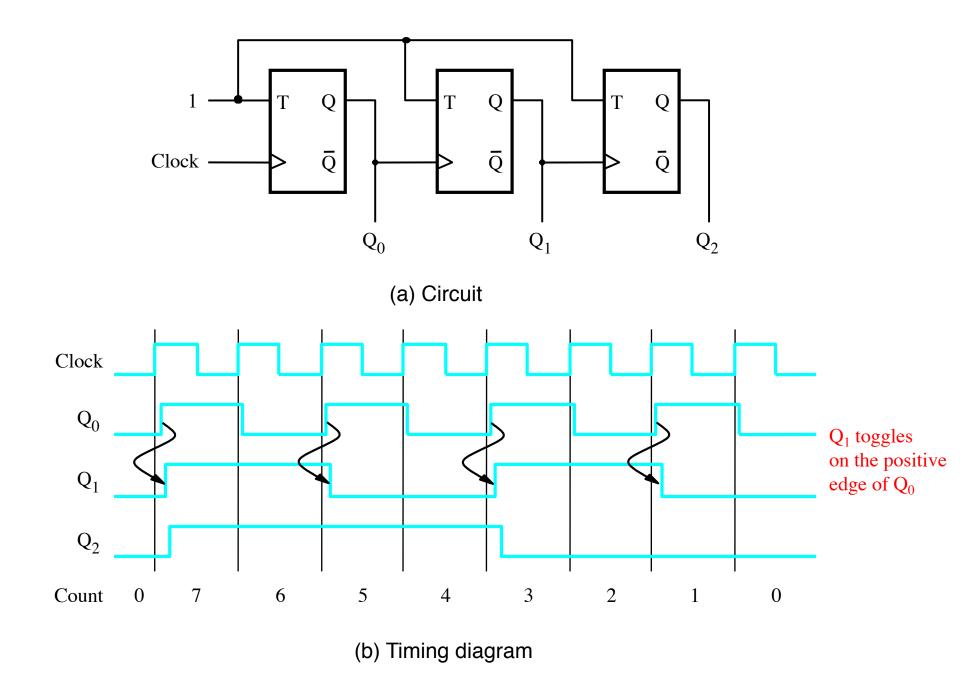

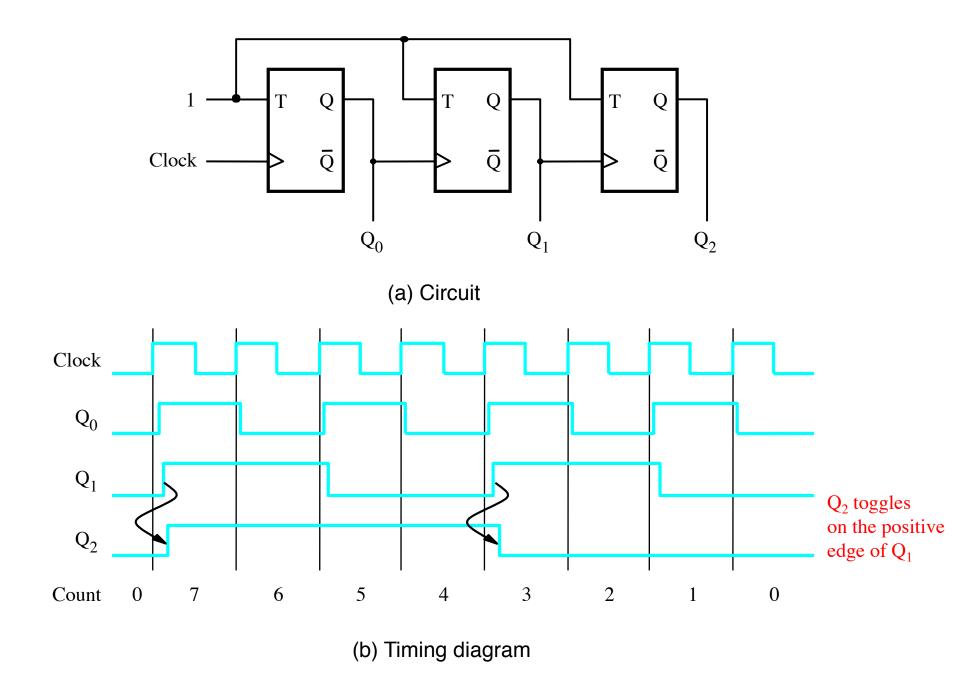

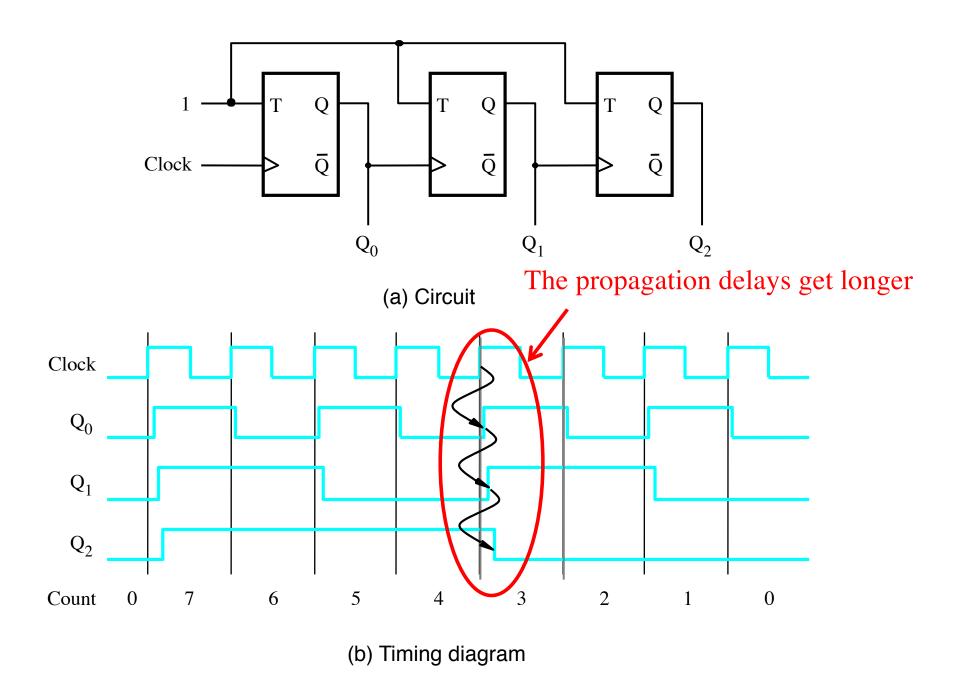

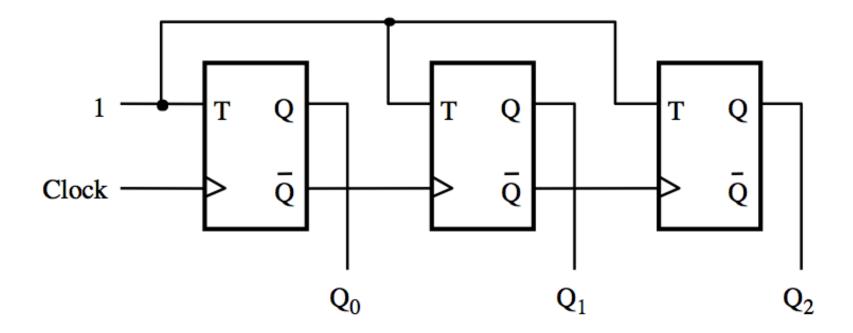

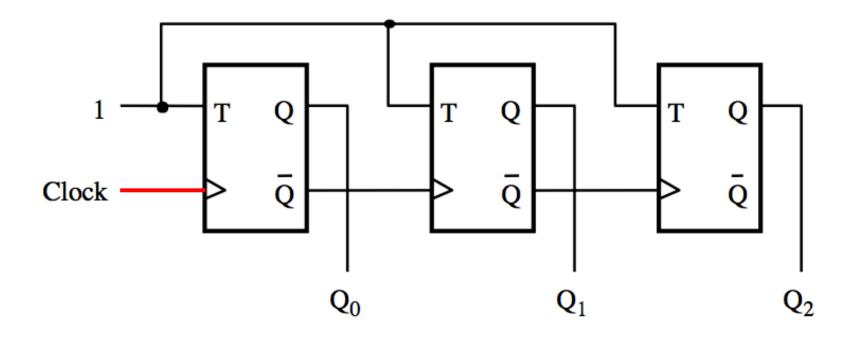

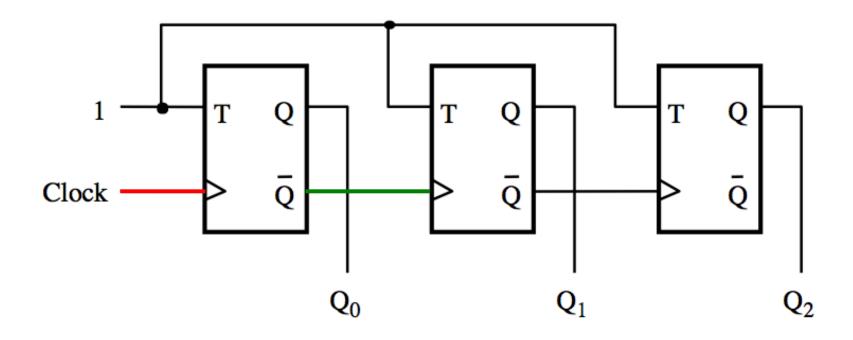

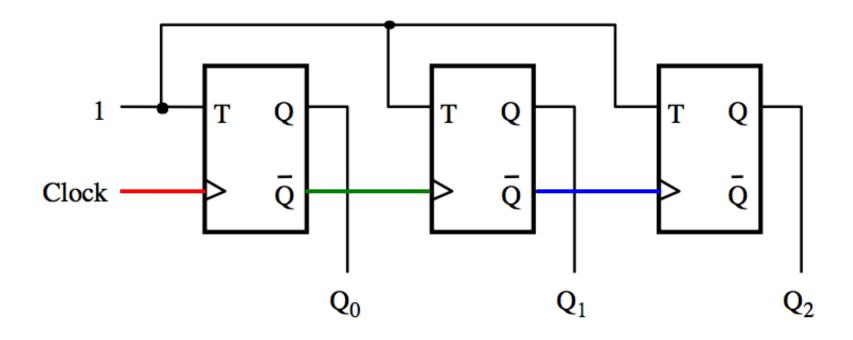

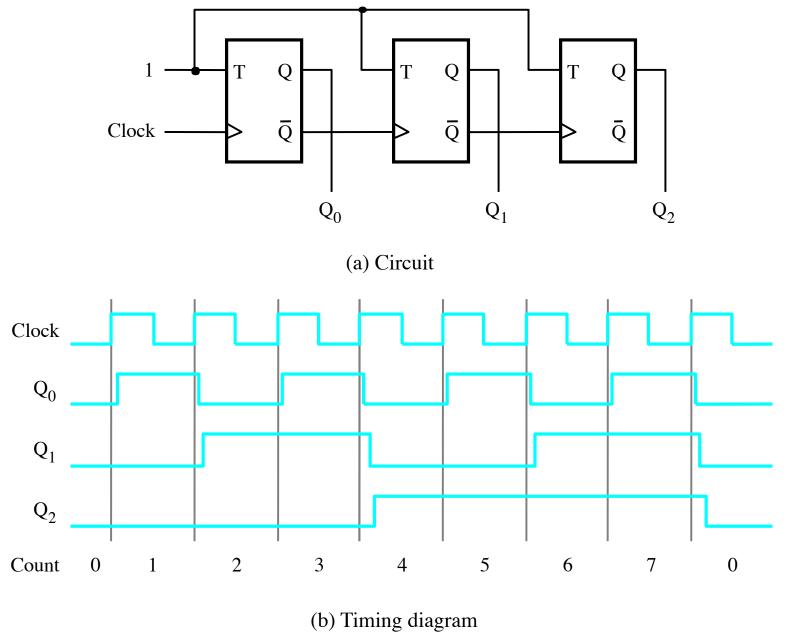

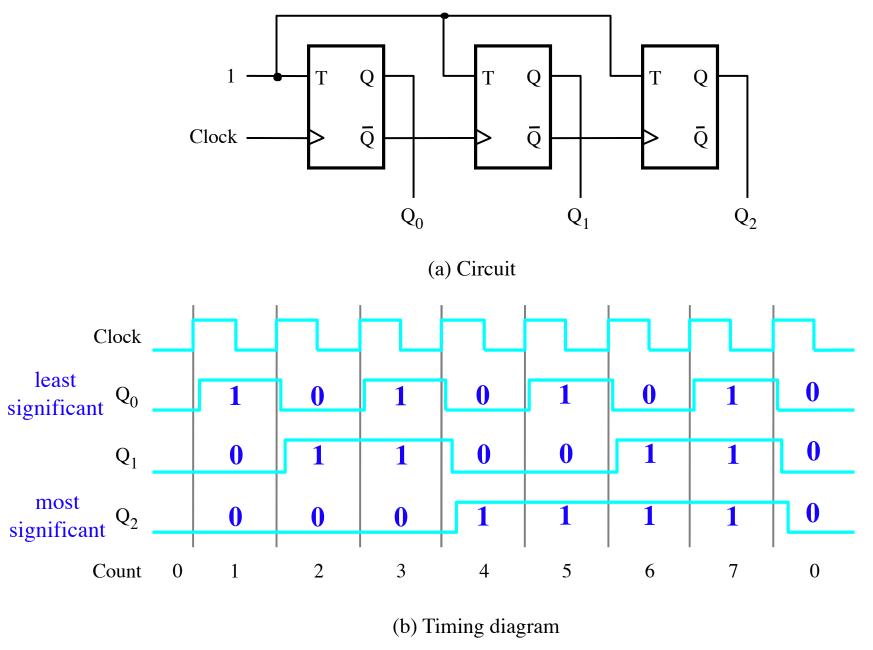

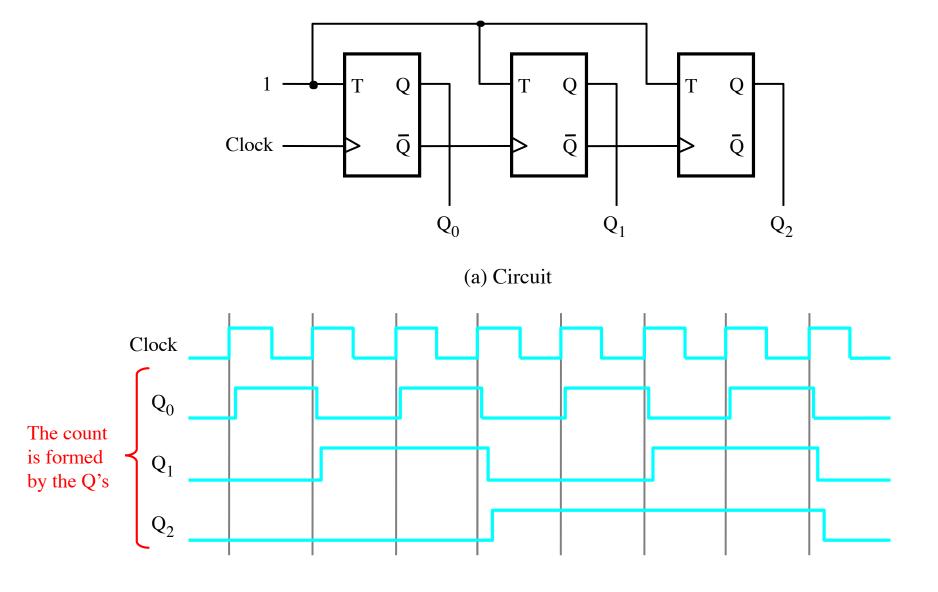

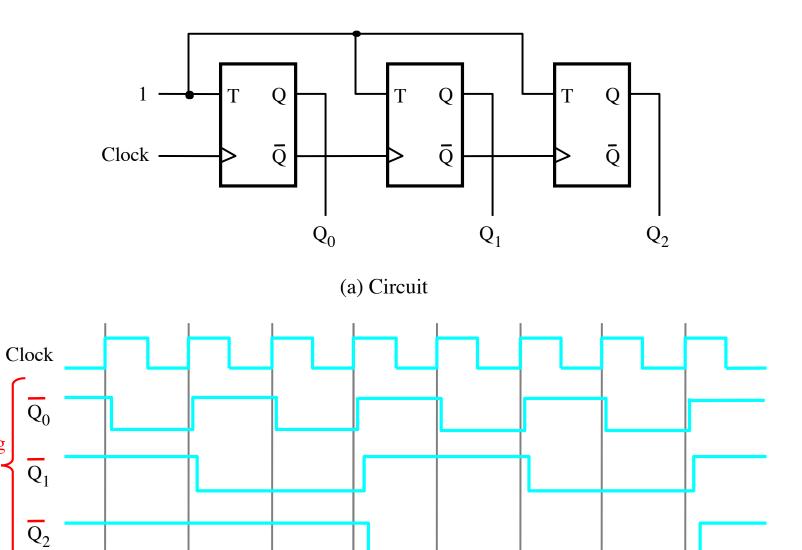

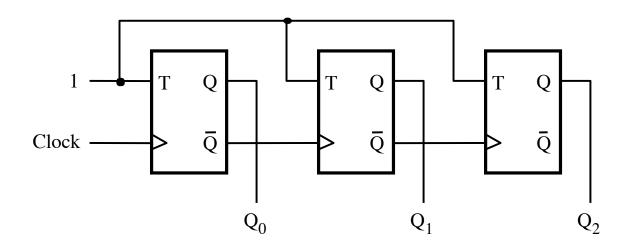

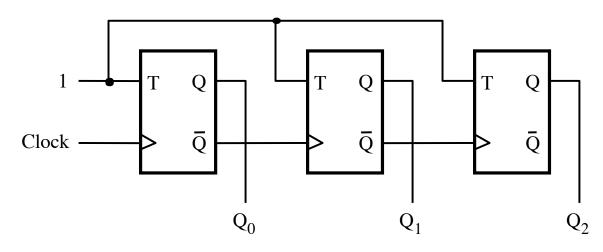

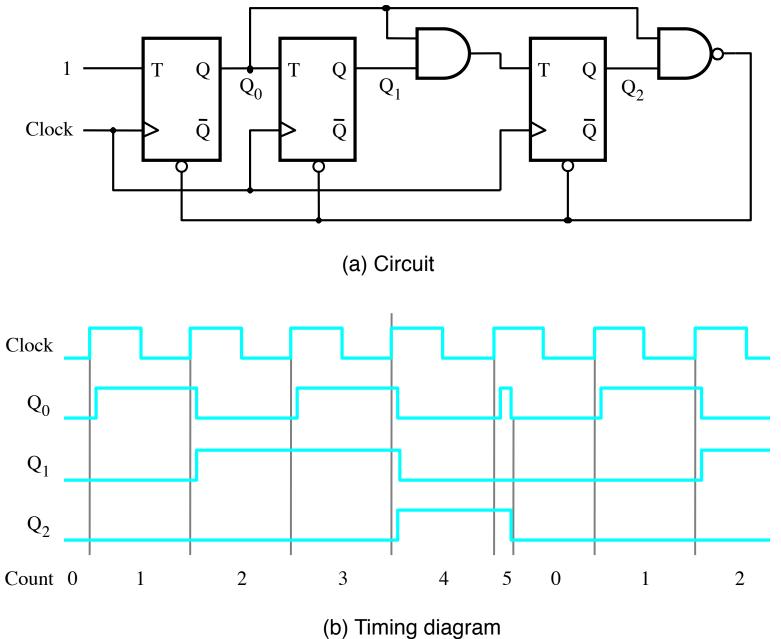

#### A three-bit down-counter

The first flip-flop changes on the positive edge of the clock

The first flip-flop changes on the positive edge of the clock

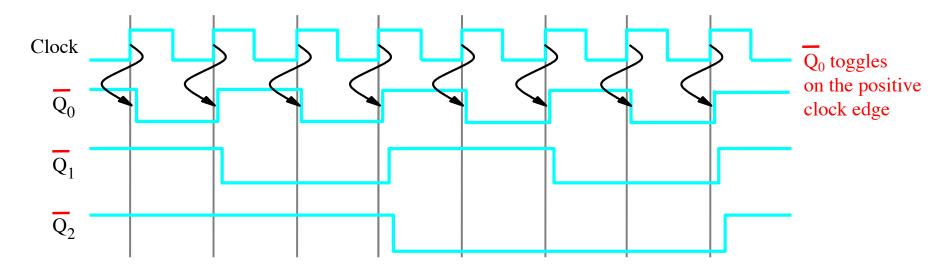

The second flip-flop changes on the positive edge of  $Q_0$

The first flip-flop changes on the positive edge of the clock

The second flip-flop changes on the positive edge of  $Q_0$

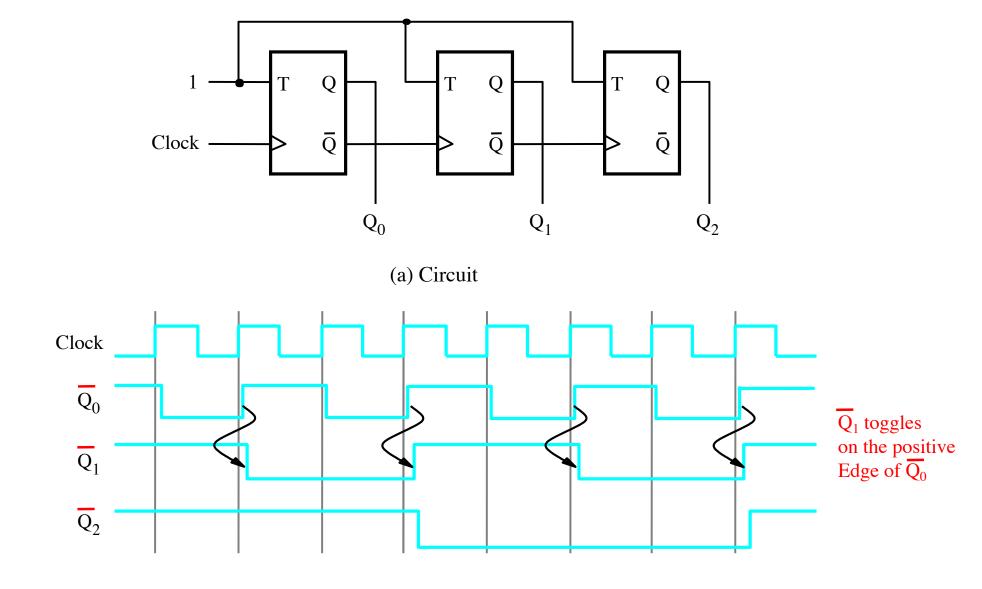

The third flip-flop changes on the positive edge of  $Q_1$

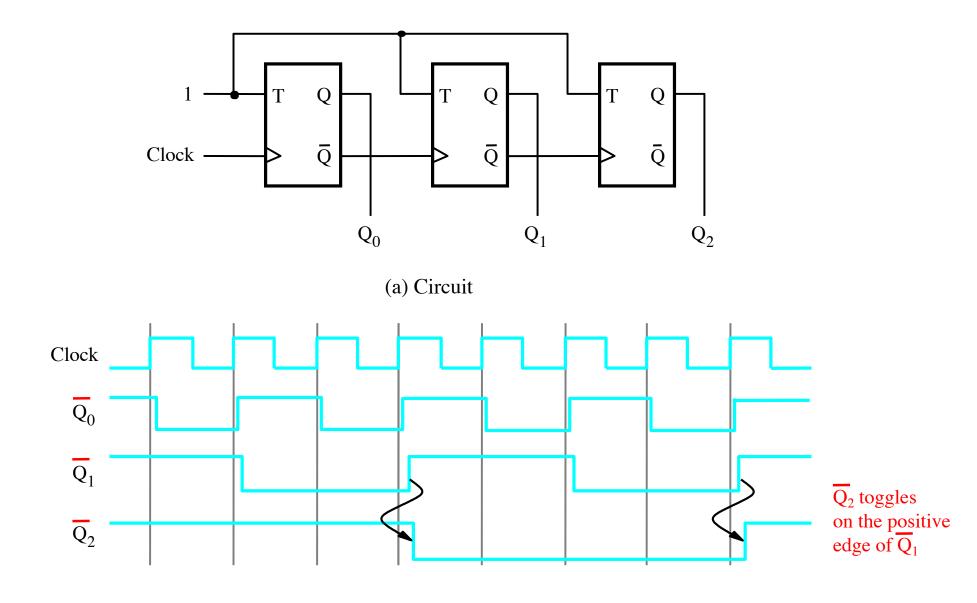

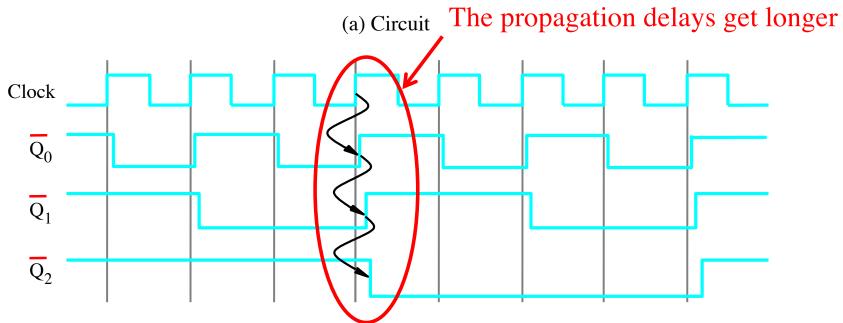

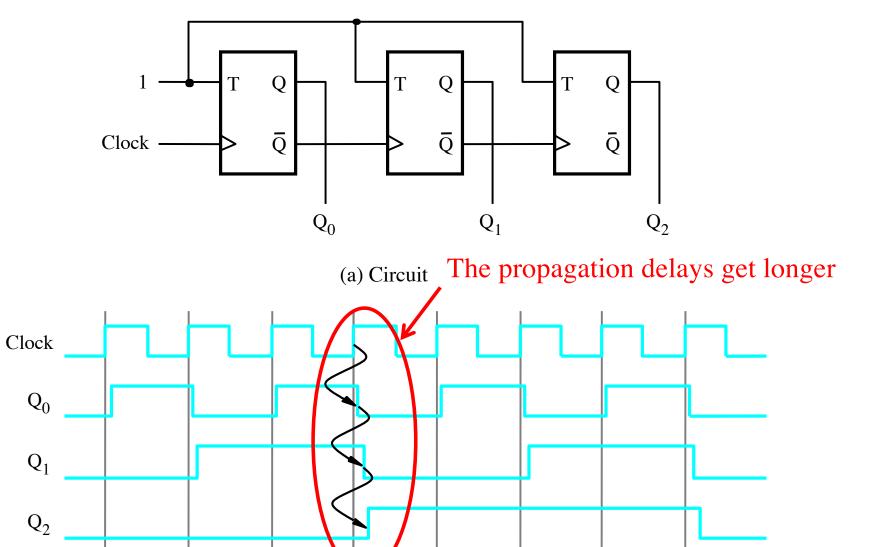

The first flip-flop changes on the positive edge of the clock

The first flip-flop changes on the positive edge of the clock

The second flip-flop changes on the positive edge of  $\overline{\mathbb{Q}}_0$

The first flip-flop changes on the positive edge of the clock

on the positive edge of  $\overline{\mathbb{Q}}_0$

The second flip-flop changes The third flip-flop changes on the positive edge of  $\overline{Q}_1$

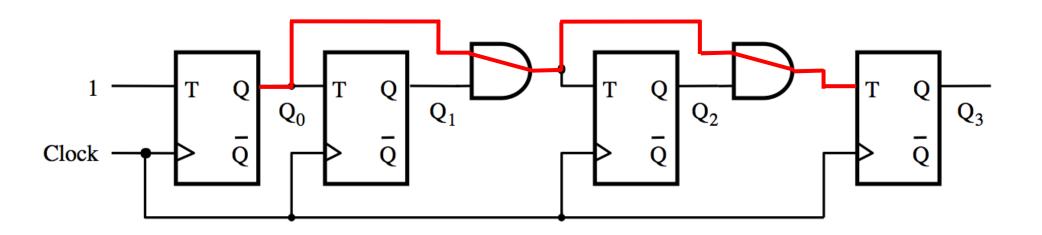

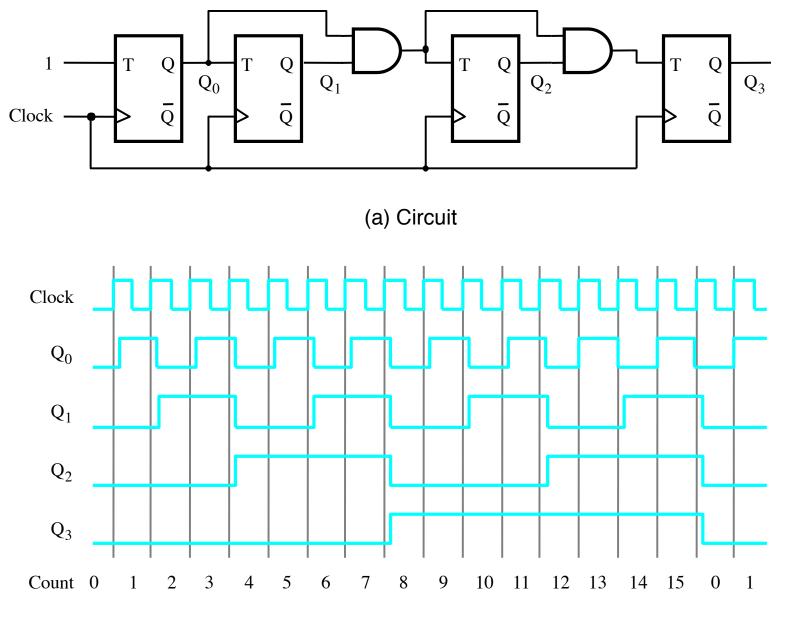

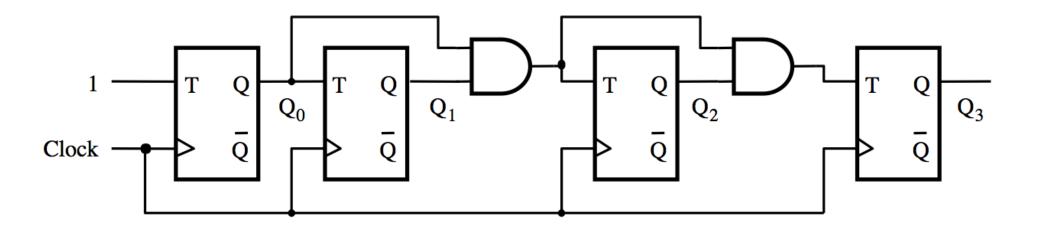

[ Figure 5.19 from the textbook ]

[ Figure 5.19 from the textbook ]

(b) Timing diagram

The toggling

is done

by the Q's

(a) Circuit

(b) Timing diagram

(b) Timing diagram

(b) Timing diagram

5

6

(b) Timing diagram

2

Count

[ Figure 5.19 from the textbook ]

0

7

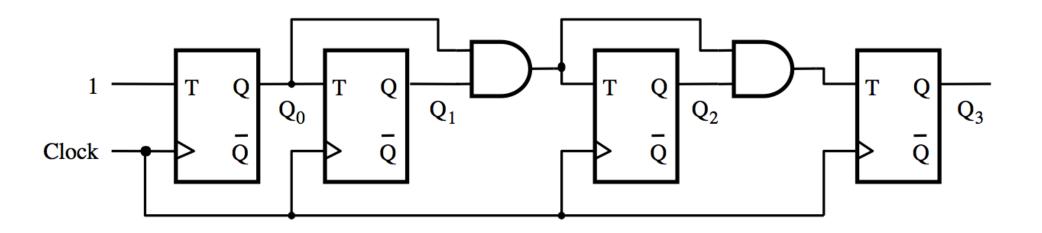

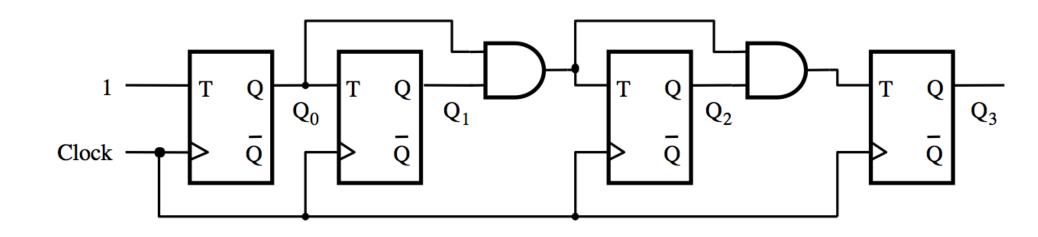

## **Synchronous Counters**

The propagation delay through all AND gates combined must not exceed the clock period minus the setup time for the flip-flops

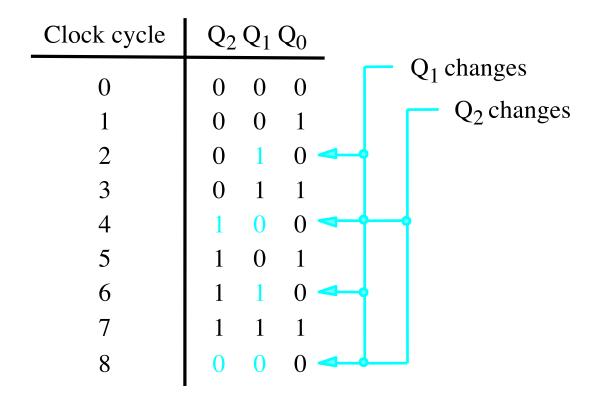

#### Derivation of the synchronous up-counter

#### Derivation of the synchronous up-counter

| Clock cycle                     | $Q_2 Q_1 Q_0$                                                                                                                                                                                                                                                                                 |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>1<br>2<br>3<br>4<br>5<br>6 | $Q_2 \ Q_1 \ Q_0$ $Q_1 \ Changes$ $Q_2 \ Q_1 \ Q_2 \ Changes$ $Q_2 \ Changes$ $Q_3 \ Changes$ $Q_4 \ Changes$ $Q_5 \ Changes$ $Q_7 \ Changes$ |

| 7<br>8                          | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                          |

|                                 |                                                                                                                                                                                                                                                                                               |

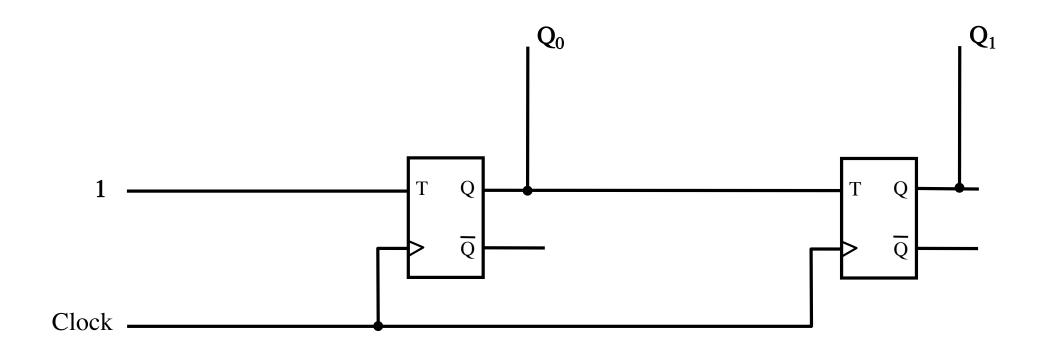

$$T_0=1$$

$$T_1=Q_0$$

$$T_2=Q_0 Q_1$$

$$T_0=1$$

$$T_1=Q_0$$

$$T_2=Q_0 Q_1$$

### In general we have

$$T_0 = 1$$

$T_1 = Q_0$

$T_2 = Q_0 Q_1$

$T_3 = Q_0 Q_1 Q_2$

...

$T_n = Q_0 Q_1 Q_2 ... Q_{n-1}$

# 2-Bit Synchronous Up-Counter (without clear capability)

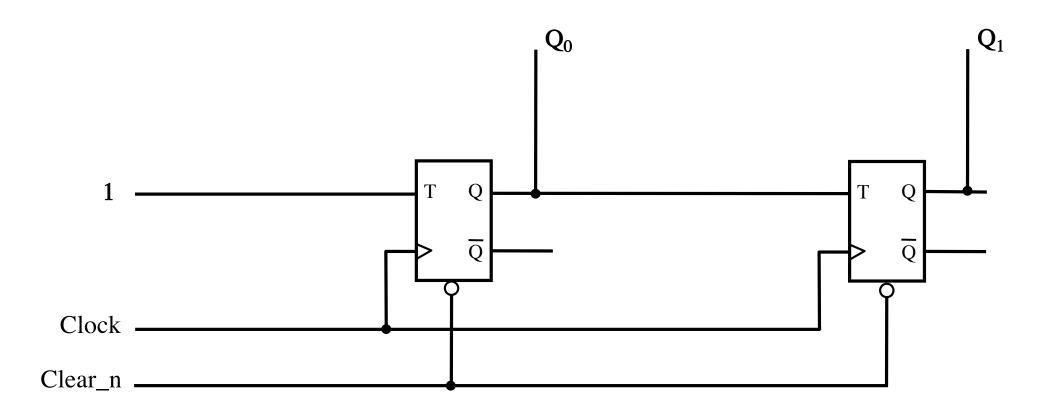

# 2-Bit Synchronous Up-Counter (with asynchronous clear)

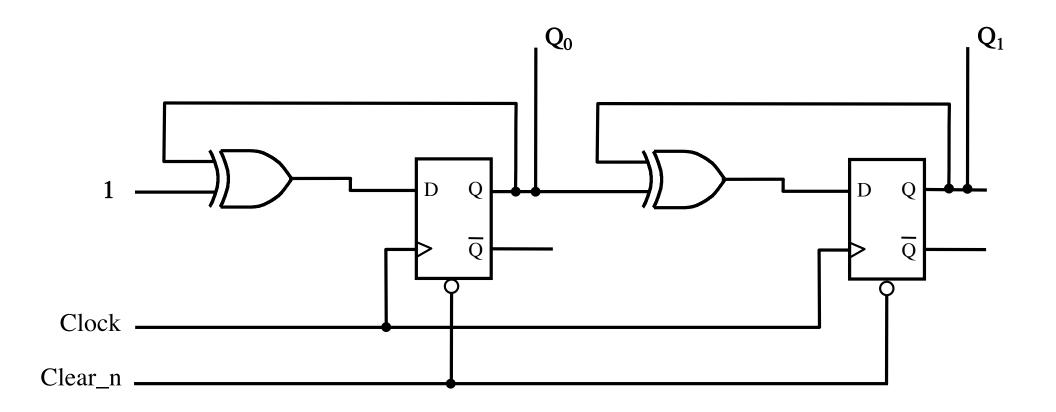

# 2-Bit Synchronous Up-Counter (with asynchronous clear)

This is the same circuit but uses D Flip-Flops.

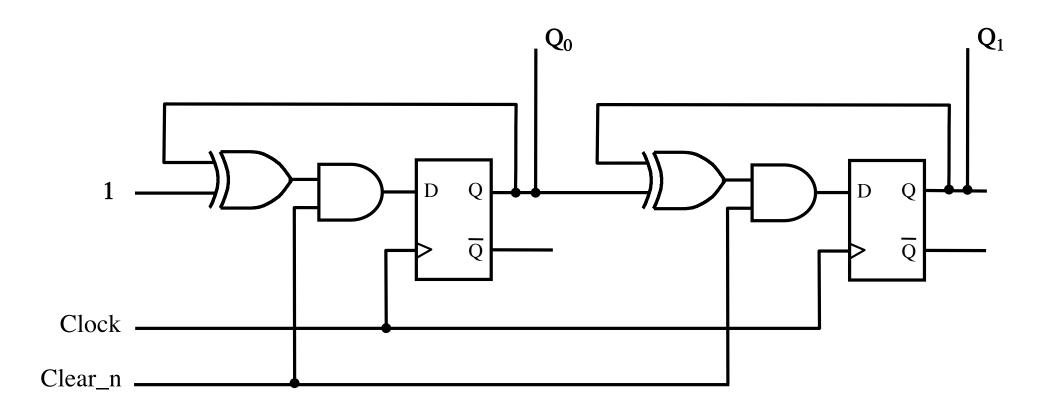

# 2-Bit Synchronous Up-Counter (with synchronous clear)

This counter can be cleared only on the positive clock edge.

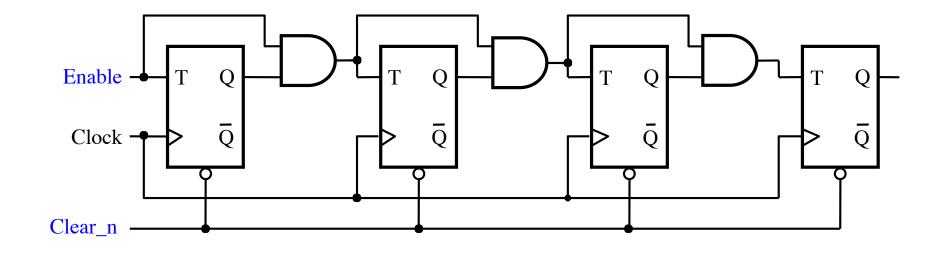

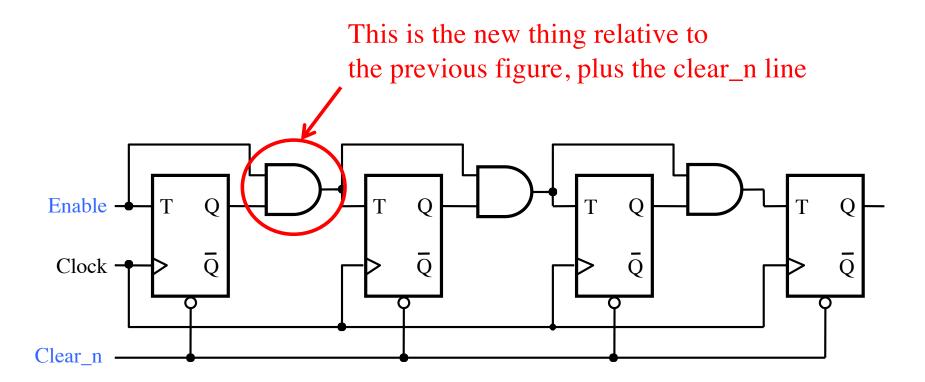

## **Adding Enable Capability**

## A four-bit synchronous up-counter

## Inclusion of Enable and Clear Capability

## Inclusion of Enable and Clear Capability

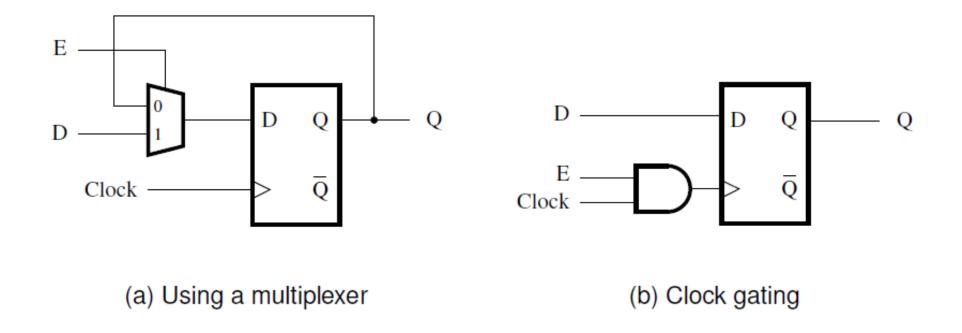

#### Providing an enable input for a D flip-flop

# Synchronous Counter (with D Flip-Flops)

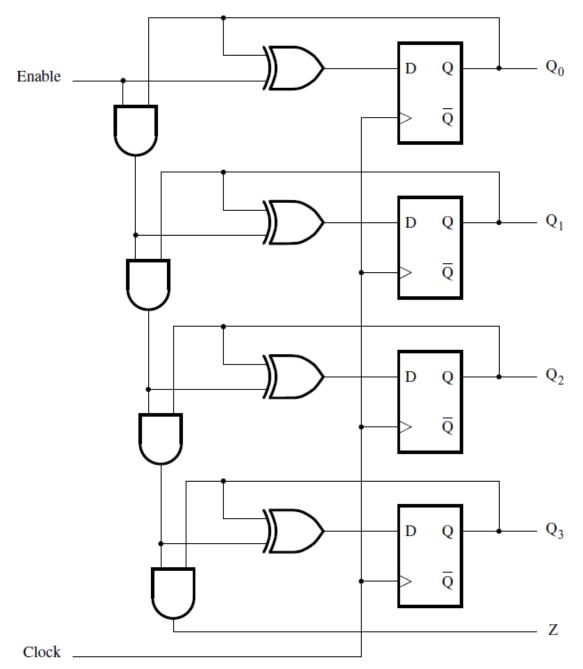

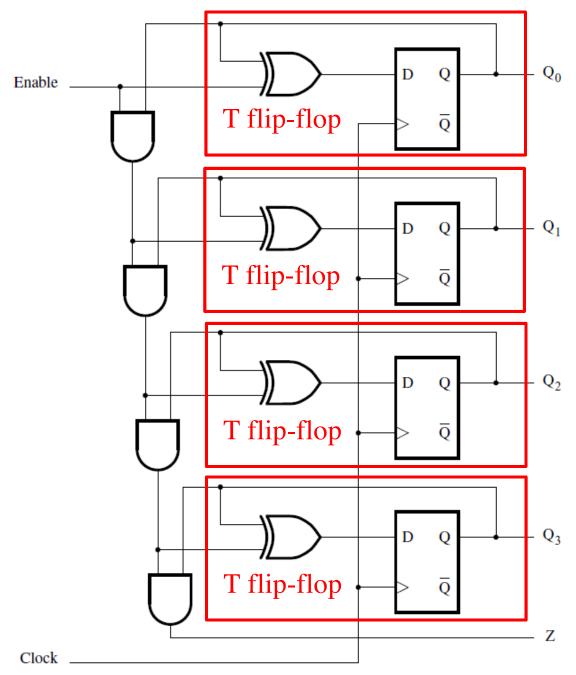

## A 4-bit up-counter with D flip-flops

## A 4-bit up-counter with D flip-flops

[ Figure 5.23 from the textbook ]

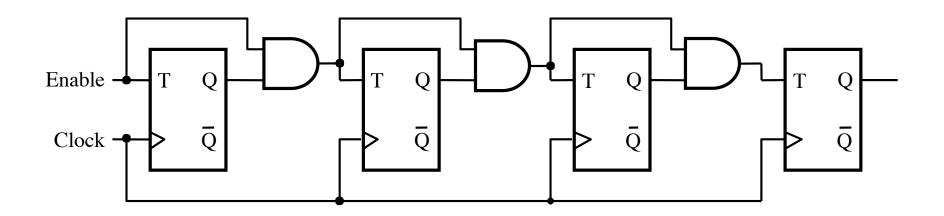

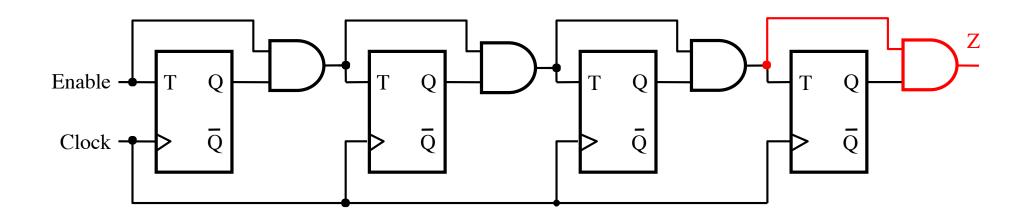

## Equivalent to this circuit with T flip-flops

## Equivalent to this circuit with T flip-flops

But has one extra output called Z, which can be used to connect two 4-bit counters to make an 8-bit counter.

When Z=1 the counter will go 0000 on the next clock edge, i.e., the outputs of all flip-flops are currently 1 (maximum count value).

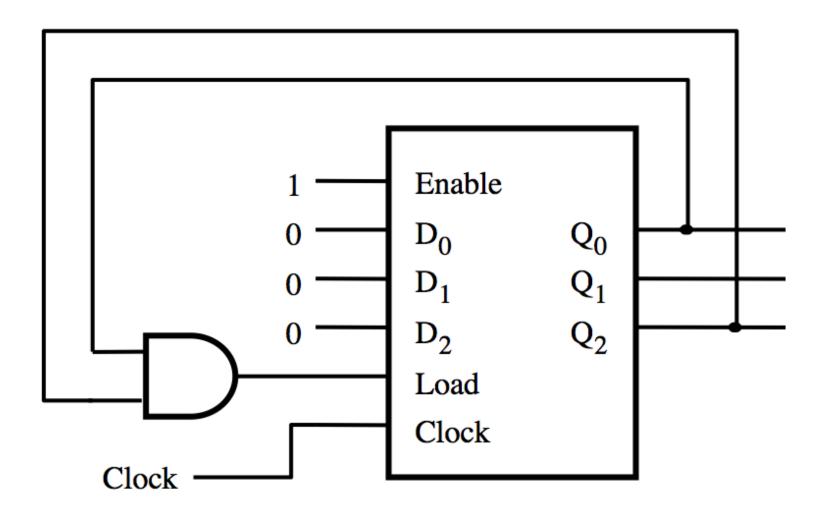

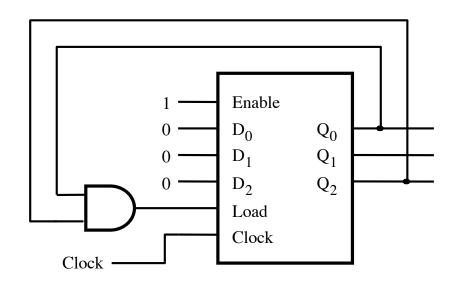

### **Counters with Parallel Load**

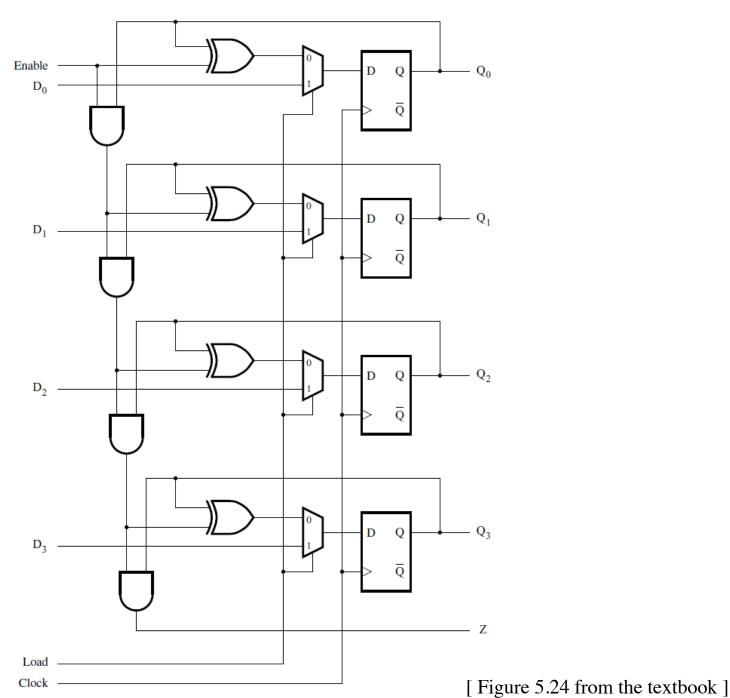

## A counter with parallel-load capability

#### How to load the initial count value

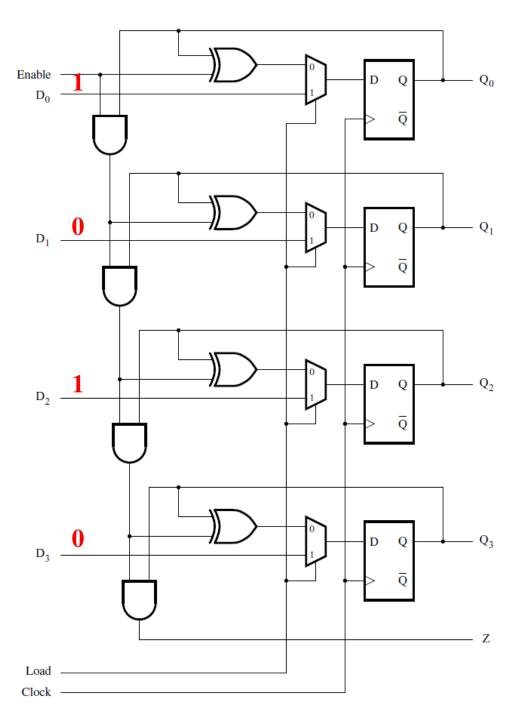

Set the initial count on the parallel load lines (in this case 5).

#### How to zero a counter

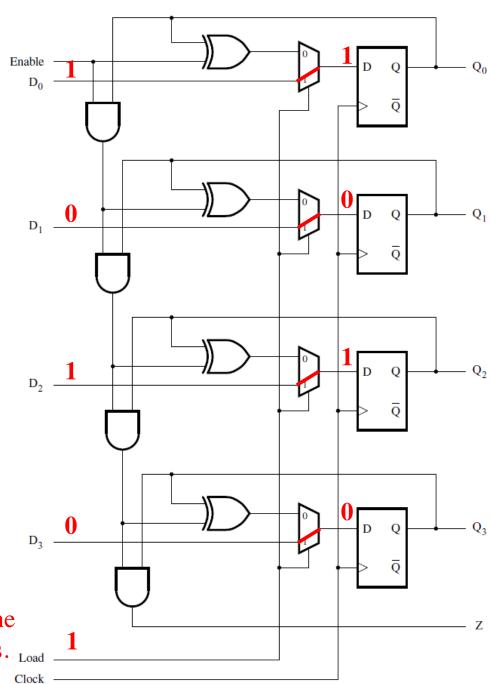

Set "Load" to 1, to open the "1" line of the multiplexers. Load

#### How to zero a counter

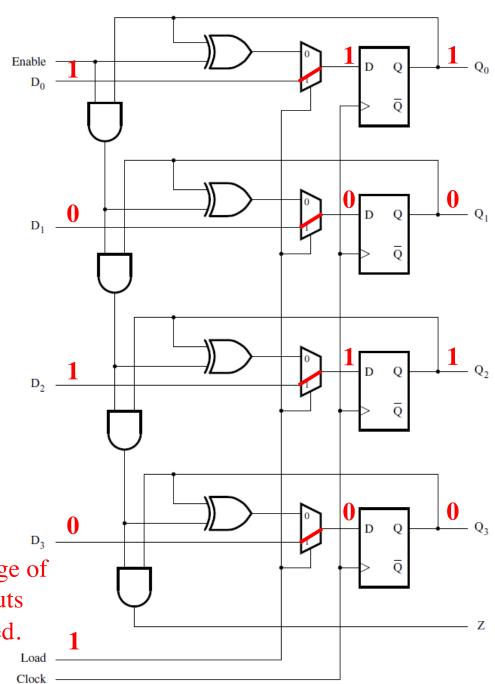

When the next positive edge of the clock arrives, the outputs of the flip-flops are updated.

## **Reset Synchronization**

#### **Motivation**

- An n-bit counter counts from 0, 1, ..., 2<sup>n</sup>-1

- For example a 3-bit counter counts up as follow

- **0**, 1, 2, 3, 4, 5, 6, 7, 0, 1, 2, ...

- What if we want it to count like this

- **0**, 1, 2, 3, 4, 5, 0, 1, 2, 3, 4, 5, 0, 1, ...

- In other words, what is the cycle is not a power of 2?

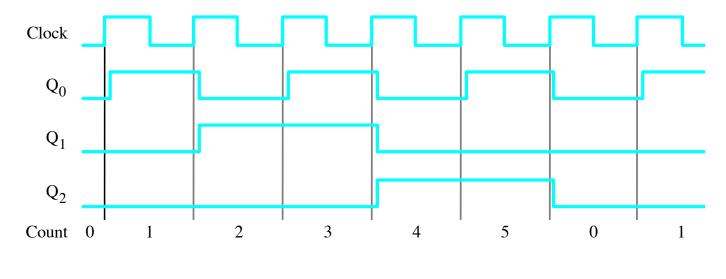

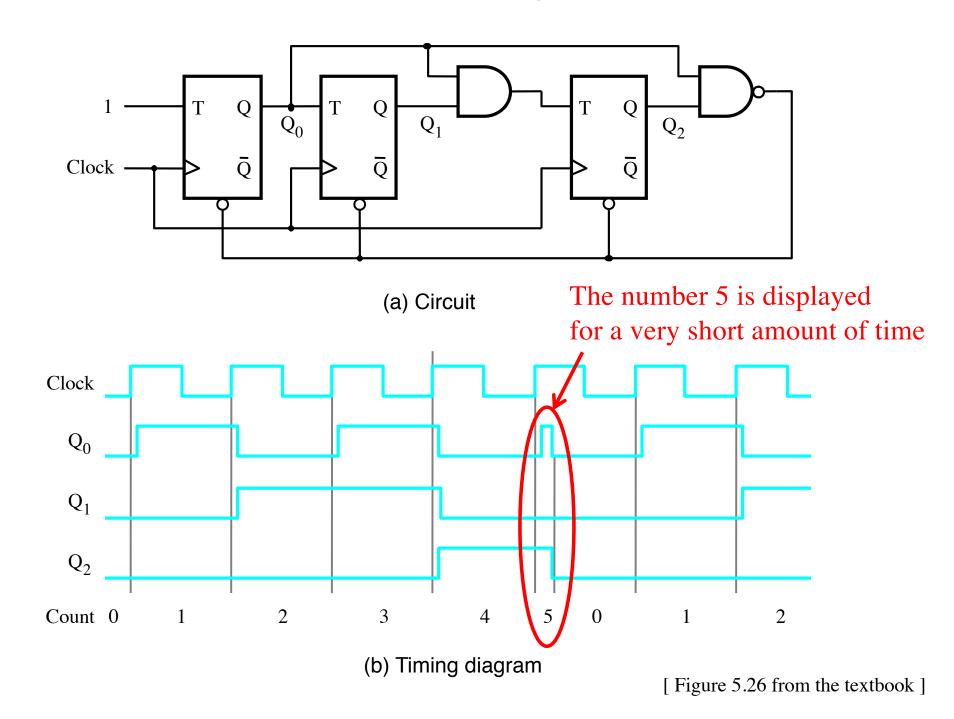

#### What does this circuit do?

#### A modulo-6 counter with synchronous reset

(a) Circuit

(b) Timing diagram

[ Figure 5.25 from the textbook ]

#### A modulo-6 counter with asynchronous reset

[ Figure 5.26 from the textbook ]

#### A modulo-6 counter with asynchronous reset

## **Questions?**

## THE END