# **CprE 281: Digital Logic**

Instructor: Alexander Stoytchev

http://www.ece.iastate.edu/~alexs/classes/

# NAND and NOR Logic Networks

CprE 281: Digital Logic Iowa State University, Ames, IA Copyright © Alexander Stoytchev

### **Administrative Stuff**

HW2 is due on Monday Aug 31 @ 4pm

#### **Administrative Stuff**

- HW3 is due on Monday Sep 7 @ 4pm

- Please write clearly on the first page the following three things:

- Your First and Last Name

- Your Student ID Number

- Your Lab Section Letter

- Submit on Canvas as \*one\* PDF file.

- Please orient your pages such that the text can be read without the need to rotate the page.

### **Quick Review**

| X | у | f <sub>00</sub> |

|---|---|-----------------|

| 0 | 0 | 1               |

| 0 | 1 | 0               |

| 1 | 0 | 0               |

| 1 | 1 | 0               |

| x | у | <b>f</b> <sub>01</sub> |

|---|---|------------------------|

| 0 | 0 | 0                      |

| 0 | 1 | 1                      |

| 1 | 0 | 0                      |

| 1 | 1 | 0                      |

| X | у | f <sub>10</sub> |

|---|---|-----------------|

| 0 | 0 | 0               |

| 0 | 1 | 0               |

| 1 | 0 | 1               |

| 1 | 1 | 0               |

| X | у | f <sub>11</sub> |

|---|---|-----------------|

| 0 | 0 | 0               |

| 0 | 1 | 0               |

| 1 | 0 | 0               |

| 1 | 1 | 1               |

$$f_{00}(x, y)$$

$$f_{01}(x, y)$$

$$f_{10}(x, y)$$

$$f_{11}(x, y)$$

| X | у | f <sub>00</sub> |

|---|---|-----------------|

| 0 | 0 | 1               |

| 0 | 1 | 0               |

| 1 | 0 | 0               |

| 1 | 1 | 0               |

| X | у | f <sub>01</sub> |

|---|---|-----------------|

| 0 | 0 | 0               |

| 0 | 1 | 1               |

| 1 | 0 | 0               |

| 1 | 1 | 0               |

| X | у | f <sub>10</sub> |

|---|---|-----------------|

| 0 | 0 | 0               |

| 0 | 1 | 0               |

| 1 | 0 | 1               |

| 1 | 1 | 0               |

| X | у | f <sub>11</sub> |

|---|---|-----------------|

| 0 | 0 | 0               |

| 0 | 1 | 0               |

| 1 | 0 | 0               |

| 1 | 1 | 1               |

$$f_{00}(x, y)$$

$$f_{01}(x, y)$$

$$f_{10}(x, y)$$

$$f_{11}(x, y)$$

| X | у | f <sub>00</sub> (x, y) | f <sub>01</sub> (x, y) | f <sub>10</sub> (x, y) | f <sub>11</sub> (x, y) |

|---|---|------------------------|------------------------|------------------------|------------------------|

| 0 | 0 | 1                      | 0                      | 0                      | 0                      |

| 0 | 1 | 0                      | 1                      | 0                      | 0                      |

| 1 | 0 | 0                      | 0                      | 1                      | 0                      |

| 1 | 1 | 0                      | 0                      | 0                      | 1                      |

| X | у | x y | <del>x</del> y | x <del>y</del> | ху |

|---|---|-----|----------------|----------------|----|

| 0 | 0 | 1   | 0              | 0              | 0  |

| 0 | 1 | 0   | 1              | 0              | 0  |

| 1 | 0 | 0   | 0              | 1              | 0  |

| 1 | 1 | 0   | 0              | 0              | 1  |

### Circuits for the four basis functions

$$f_{00}(x, y) = \overline{x} \overline{y}$$

$$x$$

$y$

$$f_{01}(x, y) = \overline{x} y$$

$$f_{10}(x, y) = x \overline{y}$$

$$\begin{array}{cccc} x & & \\ y & & \\ \end{array}$$

$$f_{11}(x, y) = x y$$

| X | у | f <sub>00</sub> |

|---|---|-----------------|

| 0 | 0 | 1               |

| 0 | 1 | 0               |

| 1 | 0 | 0               |

| 1 | 1 | 0               |

| X | у | <b>f</b> <sub>01</sub> |

|---|---|------------------------|

| 0 | 0 | 0                      |

| 0 | 1 | 1                      |

| 1 | 0 | 0                      |

| 1 | 1 | 0                      |

| X | У | f <sub>10</sub> |

|---|---|-----------------|

| 0 | 0 | 0               |

| 0 | 1 | 0               |

| 1 | 0 | 1               |

| 1 | 1 | 0               |

$$f_{00}(x, y) = \overline{x} \overline{y}$$

$f_{01}(x, y) = \overline{x} y$   $f_{10}(x, y) = x \overline{y}$   $f_{11}(x, y) = x y$

$$f_{01}(x, y) = \overline{x} y$$

$$f_{10}(x, y) = x \overline{y}$$

$$f_{11}(x, y) = x y$$

| X | у | f <sub>00</sub> |

|---|---|-----------------|

| 0 | 0 | 1               |

| 0 | 1 | 0               |

| 1 | 0 | 0               |

| 1 | 1 | 0               |

| x | у | <b>f</b> <sub>01</sub> |

|---|---|------------------------|

| 0 | 0 | 0                      |

| 0 | 1 | 1                      |

| 1 | 0 | 0                      |

| 1 | 1 | 0                      |

| x | У | f <sub>10</sub> |

|---|---|-----------------|

| 0 | 0 | 0               |

| 0 | 1 | 0               |

| 1 | 0 | 1               |

| 1 | 1 | 0               |

$$f_{00}(x, y) = \overline{x} \overline{y}$$

$f_{01}(x, y) = \overline{x} y$   $f_{10}(x, y) = x \overline{y}$   $f_{11}(x, y) = x y$

$$f_{01}(x, y) = \overline{x} y$$

$$f_{10}(x, y) = x \overline{y}$$

$$f_{11}(x, y) = x y$$

$$m_0$$

$$m_1$$

$$m_2$$

$$m_3$$

### **Minterms and Maxterms**

| Row<br>number                              | $x_1$            | $x_2$            | Minterm                                                                                                     | Maxterm                                                                                                             |

|--------------------------------------------|------------------|------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| $egin{array}{c} 0 \ 1 \ 2 \ 3 \end{array}$ | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | $m_0 = \overline{x}_1 \overline{x}_2$ $m_1 = \overline{x}_1 x_2$ $m_2 = x_1 \overline{x}_2$ $m_3 = x_1 x_2$ | $M_0 = x_1 + x_2$ $M_1 = x_1 + \overline{x_2}$ $M_2 = \overline{x_1} + x_2$ $M_3 = \overline{x_1} + \overline{x_2}$ |

### **Minterms and Maxterms**

| Row<br>number                              | $x_1$            | $x_2$                                         | Minterm | Maxterm                                                                                                                                     |

|--------------------------------------------|------------------|-----------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------|

| $egin{array}{c} 0 \ 1 \ 2 \ 3 \end{array}$ | 0<br>0<br>1<br>1 | $egin{array}{c} 0 \\ 1 \\ 0 \\ 1 \end{array}$ |         | $M_{0} = x_{1} + x_{2}$ $M_{1} = x_{1} + \overline{x_{2}}$ $M_{2} = \overline{x_{1}} + x_{2}$ $M_{3} = \overline{x_{1}} + \overline{x_{2}}$ |

Use these for Sum-of-Products Minimization (1's of the function) Use these for Product-of-Sums Minimization (0's of the function)

(uses the ones of the function)

| Row<br>number    | $x_1$            | $x_2$                                            | Minterm | $f(x_1, x_2)$                           |

|------------------|------------------|--------------------------------------------------|---------|-----------------------------------------|

| 0<br>1<br>2<br>3 | 0<br>0<br>1<br>1 | $egin{array}{c} 0 \\ 1 \\ 0 \\ 1 \\ \end{array}$ |         | $\begin{matrix} 1\\1\\0\\1\end{matrix}$ |

| Row<br>number | $x_1$ | $x_2$ | Minterm | $f(x_1, x_2)$ |

|---------------|-------|-------|---------|---------------|

| 0             | 0     | 0     |         | 1             |

| 1             | 0     | 1     |         | 1             |

| 2             | 1     | 0     |         | 0             |

| 3             | 1     | 1     |         | 1             |

| Row<br>number | $x_1$ | $x_2$ | Minterm                                                          | $f(x_1, x_2)$ |

|---------------|-------|-------|------------------------------------------------------------------|---------------|

| 0             | 0     | 0     | $m_0 = \overline{x}_1 \overline{x}_2$                            | 1             |

| 1             | 0     | 1     | $m_0 = \overline{x}_1 \overline{x}_2$ $m_1 = \overline{x}_1 x_2$ | 1             |

| 2             | 1     | 0     | $m_2 = x_1 \overline{x}_2$                                       | 0             |

| 3             | 1     | 1     | $m_2 = x_1 \overline{x_2}$ $m_3 = x_1 x_2$                       | 1             |

$$f = m_0 \cdot 1 + m_1 \cdot 1 + m_2 \cdot 0 + m_3 \cdot 1$$

=  $m_0 + m_1 + m_3$

=  $\bar{x}_1 \bar{x}_2 + \bar{x}_1 x_2 + x_1 x_2$

### **Product-of-Sums Form**

(uses the zeros of the function)

# Product-of-Sums Form (for this logic function)

| Row<br>number | $x_1$ | $x_2$ | Maxterm | $f(x_1, x_2)$ |

|---------------|-------|-------|---------|---------------|

| 0             | 0     | 0     |         | 0             |

| 1             | 0     | 1     |         | 1             |

| 2             | 1     | 0     |         | 0             |

| 3             | 1     | 1     |         | 1             |

# Product-of-Sums Form (for this logic function)

| Row<br>number                              | $x_1$            | $x_2$            | <br>  Maxterm                                                                                                                               | $f(x_1, x_2)$    |

|--------------------------------------------|------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| $egin{array}{c} 0 \ 1 \ 2 \ 3 \end{array}$ | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | $M_{0} = x_{1} + x_{2}$ $M_{1} = x_{1} + \overline{x_{2}}$ $M_{2} = \overline{x_{1}} + x_{2}$ $M_{3} = \overline{x_{1}} + \overline{x_{2}}$ | 0<br>1<br>0<br>1 |

# Product-of-Sums Form (for this logic function)

| Row<br>number                              | $x_1$            | $x_2$            | Maxterm                                                                                                                 | $f(x_1, x_2)$    |

|--------------------------------------------|------------------|------------------|-------------------------------------------------------------------------------------------------------------------------|------------------|

| $egin{array}{c} 0 \ 1 \ 2 \ 3 \end{array}$ | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | $M_{0} = x_{1} + x_{2}$ $M_{1} = x_{1} + \bar{x}_{2}$ $M_{2} = \bar{x}_{1} + x_{2}$ $M_{3} = \bar{x}_{1} + \bar{x}_{2}$ | 0<br>1<br>0<br>1 |

$$f(x_1, x_2) = M_0 \bullet M_2 = (x_1 + x_2) \bullet (\overline{x_1} + x_2)$$

# **Two New Logic Gates**

### The Three Basic Logic Gates

$$X_1$$

$X_2$

$X_1 \cdot X_2$

$$X_1$$

$X_2$

$X_1 + X_2$

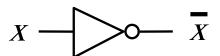

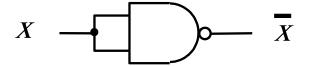

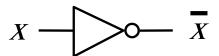

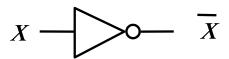

NOT gate

AND gate

**OR** gate

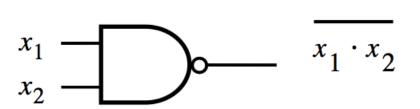

# **NAND Gate**

| $x_1$ | $x_2$ | f |

|-------|-------|---|

| 0     | 0     | 1 |

| 0     | 1     | 1 |

| 1     | 0     | 1 |

| 1     | 1     | 0 |

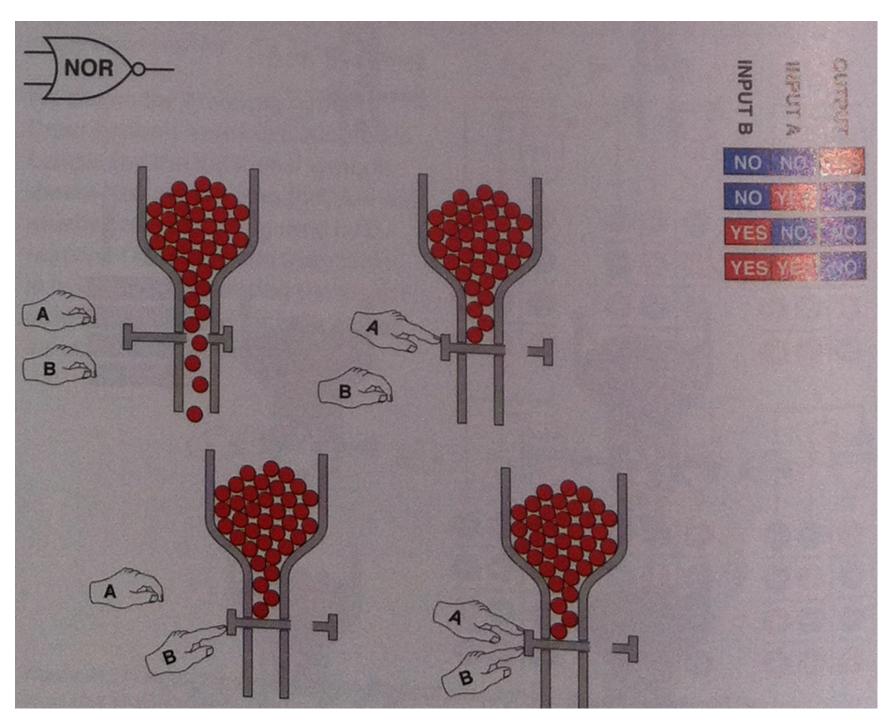

# **NOR Gate**

| $x_2$ | f           |

|-------|-------------|

| 0     | 1           |

| 1     | 0           |

| 0     | 0           |

| 1     | 0           |

|       | 0<br>1<br>0 |

### **AND vs NAND**

$$X_1$$

$X_2$   $X_1 \cdot X_2$

$$X_1$$

$X_2$

$X_1 \cdot X_2$

| $x_1$ | $x_2$ | f |

|-------|-------|---|

| 0     | 0     | 0 |

| 0     | 1     | 0 |

| 1     | 0     | 0 |

| 1     | 1     | 1 |

$$\begin{array}{c|ccc} x_1 & x_2 & f \\ \hline 0 & 0 & 1 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 0 \\ \end{array}$$

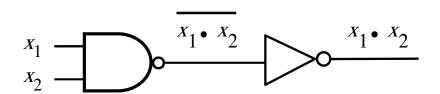

# **AND followed by NOT = NAND**

$$X_1$$

$X_2$

$X_1 \cdot X_2$

| $x_1$ | $x_2$ | <b>†</b> | İ |

|-------|-------|----------|---|

| 0     | 0     | 0        | 1 |

| 0     | 1 0   | 0        | 1 |

| 1     | 0     | 0        | 1 |

| 1     | 1     | 1        | 0 |

| $x_1$ | $x_2$ | f |

|-------|-------|---|

| 0     | 0     | 1 |

| 0     | 1     | 1 |

| 1     | 0     | 1 |

| 1     | 1     | 0 |

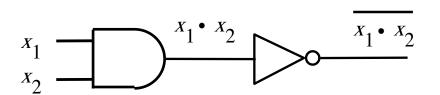

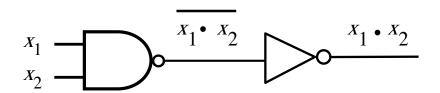

## NAND followed by NOT = AND

$$X_1$$

$X_2$

$X_1 \cdot X_2$

| $x_1$ | $x_2$ | f | <u>f</u> |

|-------|-------|---|----------|

| 0     | 0     | 1 | 0        |

| 0     | 1     | 1 | 0        |

| 1     | 0     | 1 | 0        |

| 1     | 1     | 0 | 1        |

$$egin{array}{c|cccc} x_1 & x_2 & \mathbf{f} \\ \hline 0 & 0 & 0 \\ 0 & 1 & 0 \\ 1 & 0 & 0 \\ 1 & 1 & 1 \\ \hline \end{array}$$

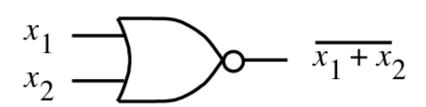

### OR vs NOR

$$\begin{array}{c} x_1 \\ x_2 \end{array} \longrightarrow \begin{array}{c} x_1 + x_2 \end{array}$$

$$x_1$$

$x_2$

$\overline{x_1 + x_2}$

| $x_1$ | $x_2$ | f |

|-------|-------|---|

| 0     | 0     | 0 |

| 0     | 1     | 1 |

| 1     | 0     | 1 |

| 1     | 1     | 1 |

$$egin{array}{c|cccc} x_1 & x_2 & \mathbf{f} \\ \hline 0 & 0 & 1 \\ 0 & 1 & 0 \\ 1 & 0 & 0 \\ 1 & 1 & 0 \\ \hline \end{array}$$

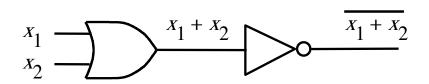

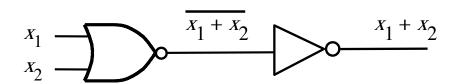

## OR followed by NOT = NOR

$$x_1$$

$x_2$

$\overline{x_1 + x_2}$

| $x_{I}$ | $x_2$            | f | f |

|---------|------------------|---|---|

| 0       | 0                | 0 | 1 |

| 0       | 0<br>1<br>0<br>1 | 1 | 0 |

| 1       | 0                | 1 | 0 |

| 1       | 1                | 1 | 0 |

$$egin{array}{c|cccc} x_1 & x_2 & \mathbf{f} \\ \hline 0 & 0 & 1 \\ 0 & 1 & 0 \\ 1 & 0 & 0 \\ 1 & 1 & 0 \\ \hline \end{array}$$

# NOR followed by NOT = OR

$$X_1$$

$X_2$

$X_1 + X_2$

| $x_1$ | $x_2$  | 1 | İ |

|-------|--------|---|---|

| 0     | 0      | 1 | 0 |

| 0     | 1<br>0 | 0 | 1 |

| 1     | 0      | 0 | 1 |

| 1     | 1      | 0 | 1 |

$$egin{array}{c|cccc} x_1 & x_2 & \mathbf{f} \\ \hline 0 & 0 & 0 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 1 \\ \hline \end{array}$$

# Why do we need two more gates?

### Why do we need two more gates?

They can be implemented with fewer transistors.

# They are simpler to implement, but are they also useful?

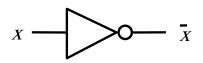

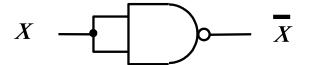

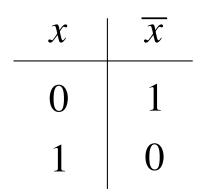

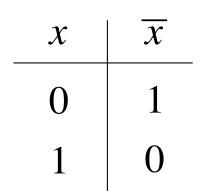

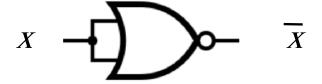

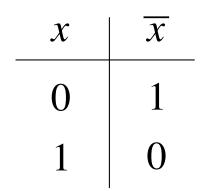

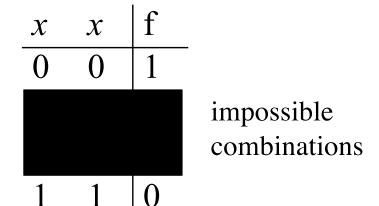

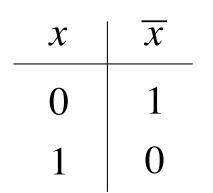

# **Building a NOT Gate with NAND**

| $\mathcal{X}$ | $\boldsymbol{\mathcal{X}}$ | f |

|---------------|----------------------------|---|

| 0             | 0                          | 1 |

| 0             | 1                          | 1 |

| 1             | 0                          | 1 |

| 1             | 1                          | 0 |

### **Building a NOT Gate with NAND**

### **Building a NOT Gate with NAND**

Thus, the two truth tables are equal!

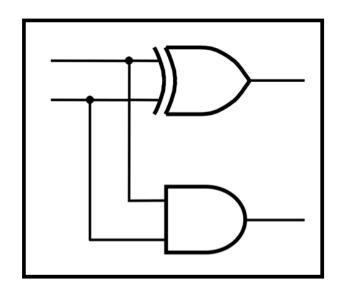

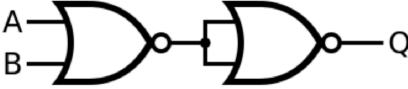

### Building an AND gate with NAND gates

| Input A | Input B | Output Q |

|---------|---------|----------|

| 0       | 0       | 0        |

| 0       | 1       | 0        |

| 1       | 0       | 0        |

| 1       | 1       | 1        |

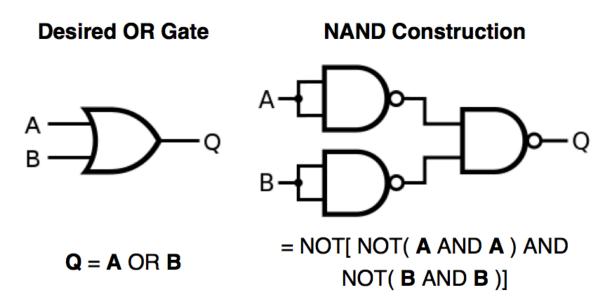

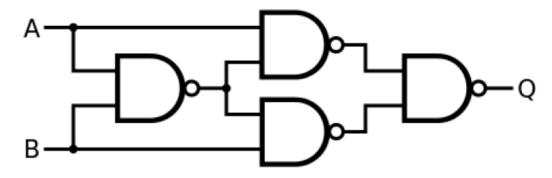

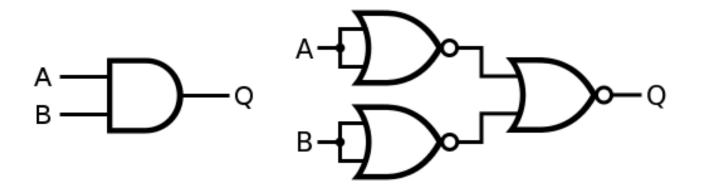

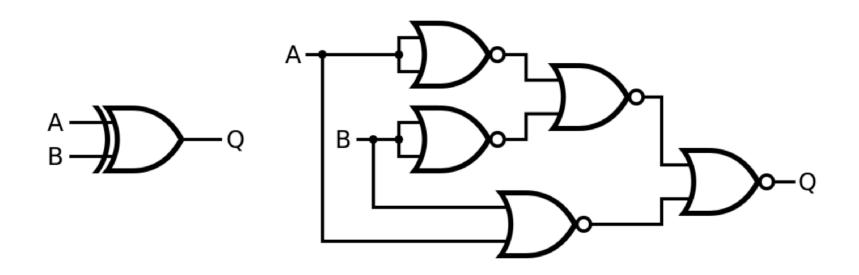

### **Building an OR gate with NAND gates**

| Input A | Input B | Output Q |

|---------|---------|----------|

| 0       | 0       | 0        |

| 0       | 1       | 1        |

| 1       | 0       | 1        |

| 1       | 1       | 1        |

## **Implications**

### **Implications**

Any Boolean function can be implemented with only NAND gates!

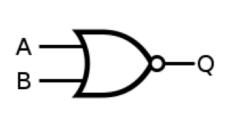

### **NOR** gate with NAND gates

#### **Desired NOR Gate**

#### **NAND Construction**

$\mathbf{Q} = \mathsf{NOT}(\mathbf{A} \ \mathsf{OR} \ \mathbf{B})$

= NOT( NOT[ NOT( A AND A ) AND NOT( B AND B )]}

| Input A | Input B | Output Q |

|---------|---------|----------|

| 0       | 0       | 1        |

| 0       | 1       | 0        |

| 1       | 0       | 0        |

| 1       | 1       | 0        |

### **XOR** gate with NAND gates

#### **Desired XOR Gate**

Q = A XOR B

#### **NAND Construction**

= NOT[ NOT(**A** AND NOT(**A** AND **B**)) AND NOT(**B** AND NOT(**A** AND **B**)) ]

**Truth Table**

| Input A | Input B | Output Q |

|---------|---------|----------|

| 0       | 0       | 0        |

| 0       | 1       | 1        |

| 1       | 0       | 1        |

| 1       | 1       | 0        |

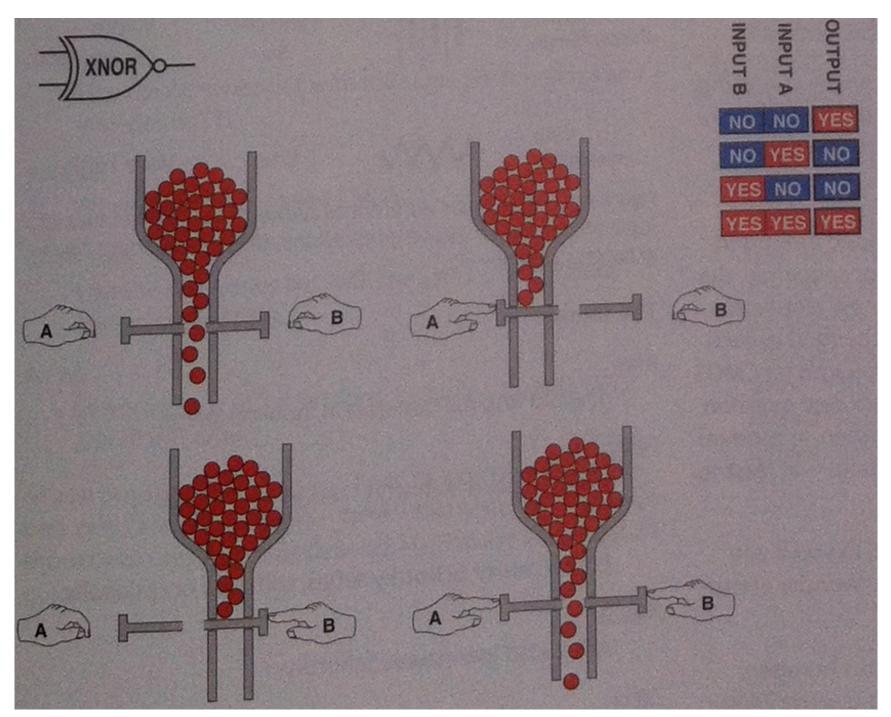

### **XNOR** gate with NAND gates

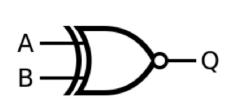

#### **Desired XNOR Gate**

## A \_\_\_\_\_Q

$\mathbf{Q} = \mathsf{NOT}(\mathbf{A} \mathsf{XOR} \mathbf{B})$

#### **NAND Construction**

= NOT[ NOT[ NOT(**A** AND NOT(**A** AND **B**)} AND NOT(**B** AND NOT(**A** AND **B**)} ] ]

| Input A | Input B | Output Q |

|---------|---------|----------|

| 0       | 0       | 1        |

| 0       | 1       | 0        |

| 1       | 0       | 0        |

| 1       | 1       | 1        |

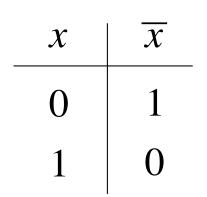

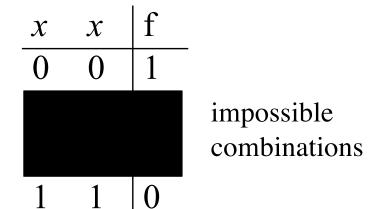

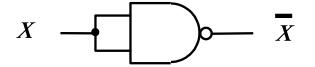

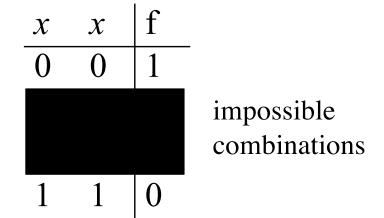

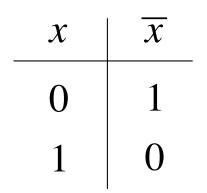

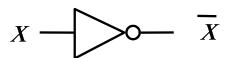

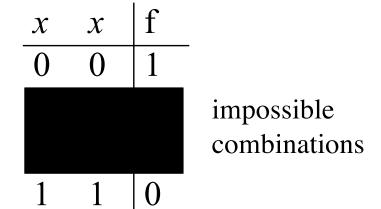

### **Building a NOT Gate with NOR**

| $\mathcal{X}$ | $\mathcal{X}$ | f |

|---------------|---------------|---|

| 0             | 0             | 1 |

| 0             | 1             | 0 |

| 1             | 0             | 0 |

| 1             | 1             | 0 |

### **Building a NOT Gate with NOR**

### **Building a NOT Gate with NOR**

Thus, the two truth tables are equal!

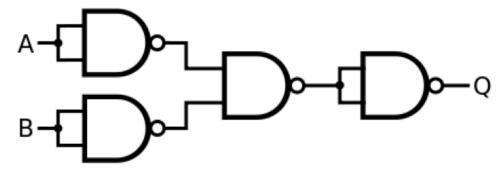

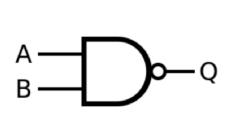

### Building an OR gate with NOR gates

#### **Desired Gate**

#### **NOR Construction**

| Input A | Input B | Output Q |

|---------|---------|----------|

| 0       | 0       | 0        |

| 0       | 1       | 1        |

| 1       | 0       | 1        |

| 1       | 1       | 1        |

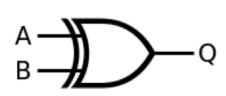

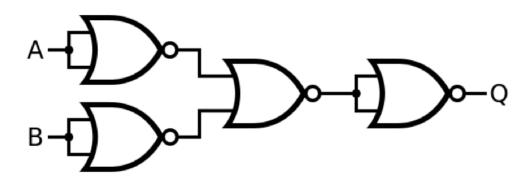

### Let's build an AND gate with NOR gates

### Let's build an AND gate with NOR gates

#### **Desired Gate**

#### **NOR Construction**

| Input A | Input B | Output Q |

|---------|---------|----------|

| 0       | 0       | 0        |

| 0       | 1       | 0        |

| 1       | 0       | 0        |

| 1       | 1       | 1        |

## **Implications**

### **Implications**

Any Boolean function can be implemented with only NOR gates!

### NAND gate with NOR gates

#### **Desired Gate**

#### NOR Construction

| Input A | Input B | Output Q |

|---------|---------|----------|

| 0       | 0       | 1        |

| 0       | 1       | 1        |

| 1       | 0       | 1        |

| 1       | 1       | 0        |

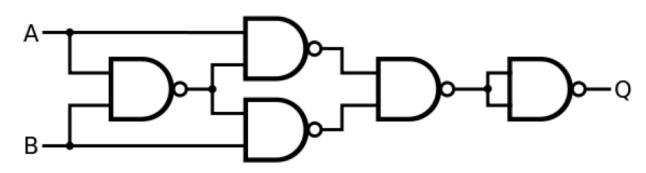

### XOR gate with NOR gates

**Truth Table**

| Input A | Input B | Output Q |

|---------|---------|----------|

| 0       | 0       | 0        |

| 0       | 1       | 1        |

| 1       | 0       | 1        |

| 1       | 1       | 0        |

### **XNOR** gate with NOR gates

#### **Desired XNOR Gate**

#### **NOR Construction**

**Truth Table**

| Input A | Input B | Output Q |

|---------|---------|----------|

| 0       | 0       | 1        |

| 0       | 1       | 0        |

| 1       | 0       | 0        |

| 1       | 1       | 1        |

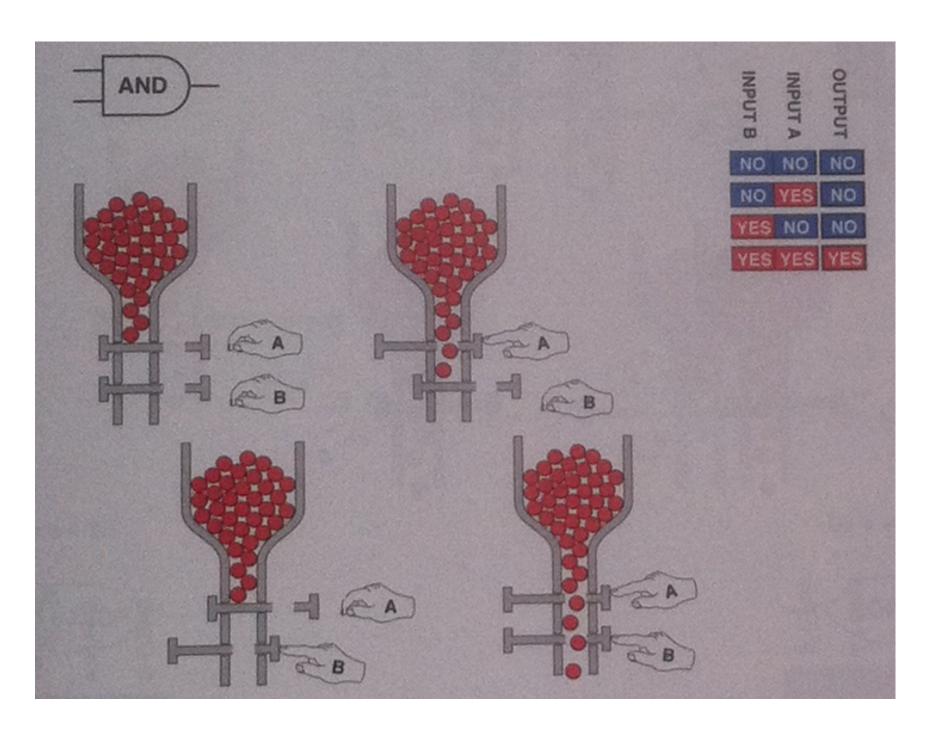

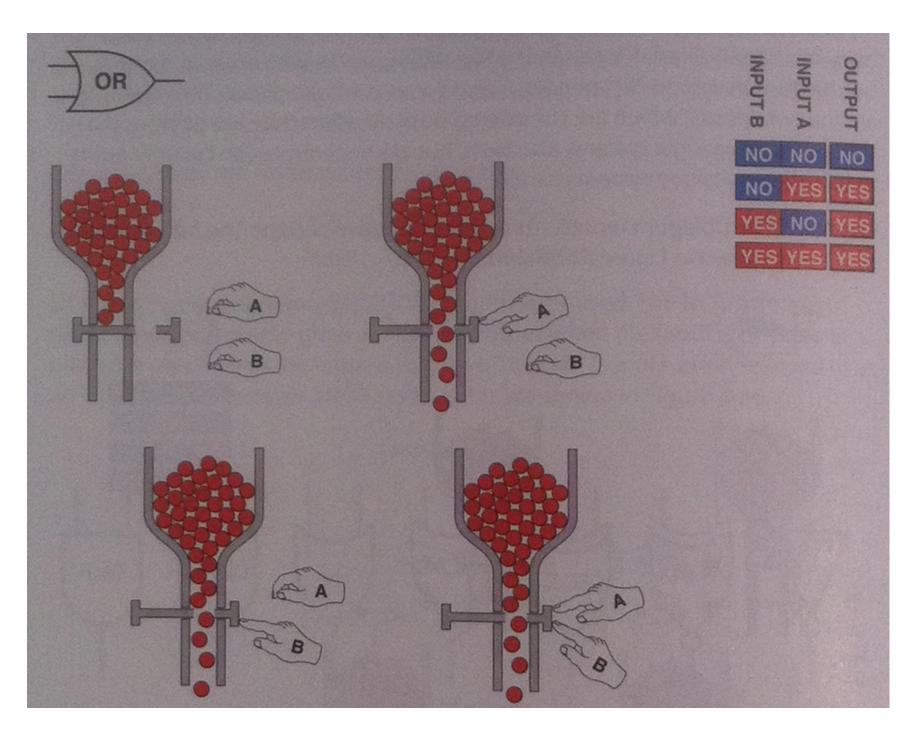

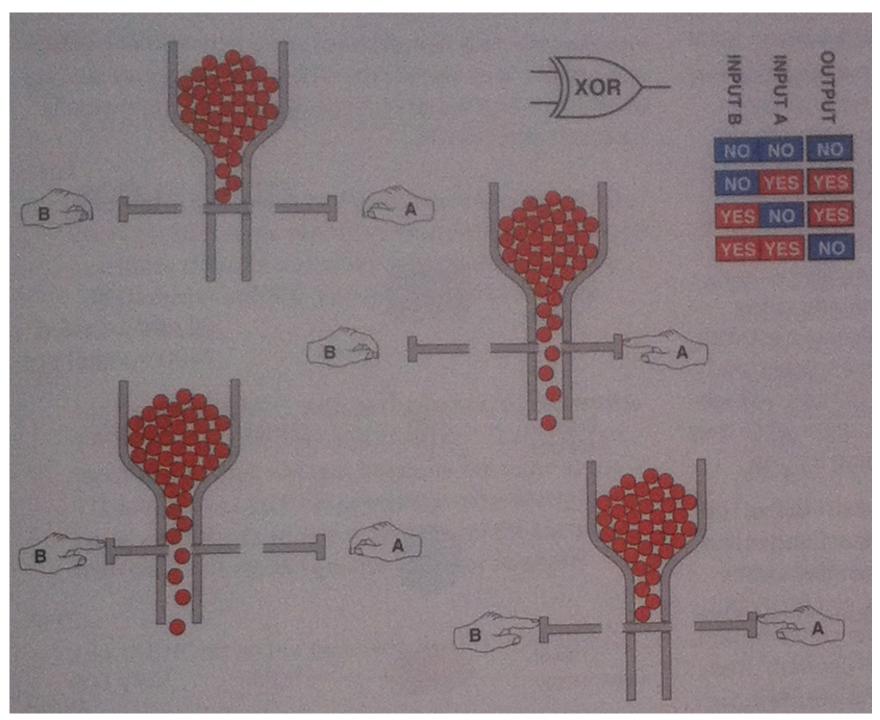

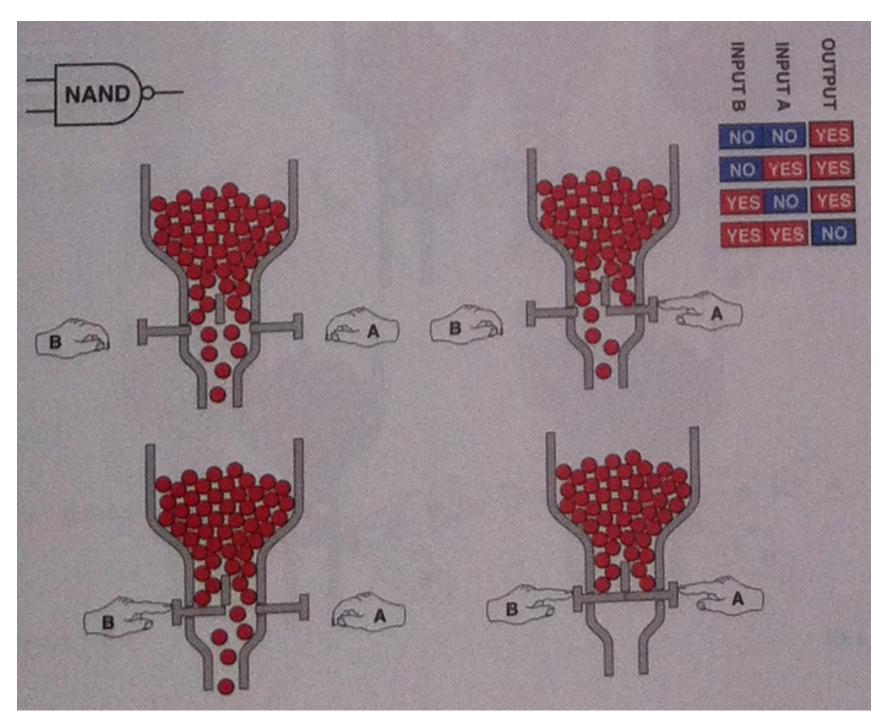

#### The following examples came from this book

[ Platt 2009 ]

[ Platt 2009 ]

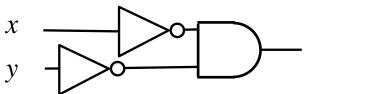

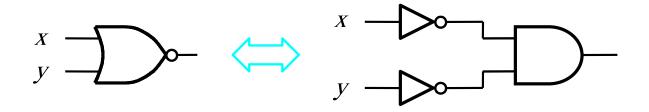

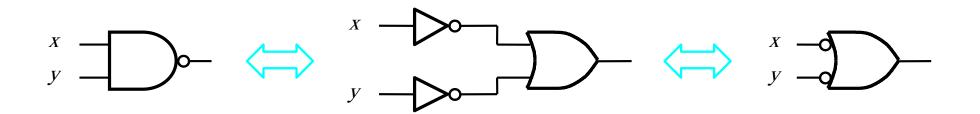

### DeMorgan's Theorem Revisited

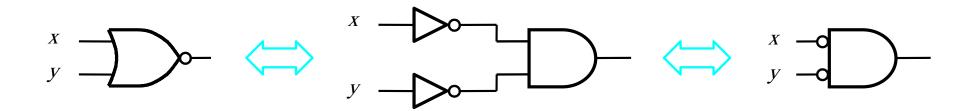

## DeMorgan's theorem (in terms of logic gates)

$$x \cdot y = x + y$$

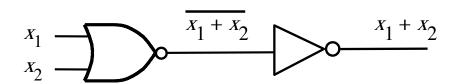

# The other DeMorgan's theorem (in terms of logic gates)

$$\frac{1}{x} + y = x \cdot y$$

#### **Shortcut Notation**

#### DeMorgan's theorem in terms of logic gates

(Theorem 15.a)

$$\overline{X \cdot y} = \overline{X + y}$$

#### DeMorgan's theorem in terms of logic gates

(Theorem 15.b)

$$\overline{X + y} = \overline{X} \overline{y}$$

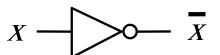

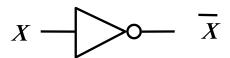

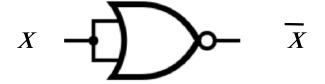

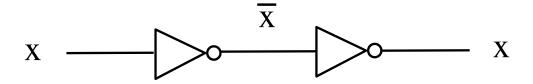

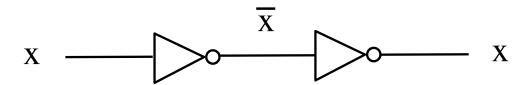

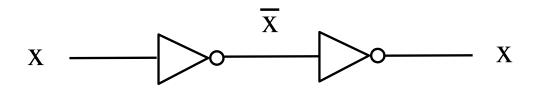

### Two NOTs in a row

#### Two NOTs in a row

X \_\_\_\_\_ X

## Two NOTs in a row

$$X \longrightarrow \bigcirc X$$

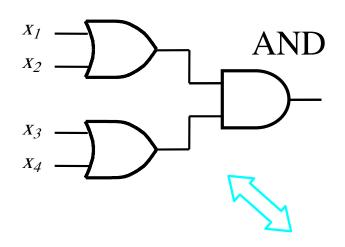

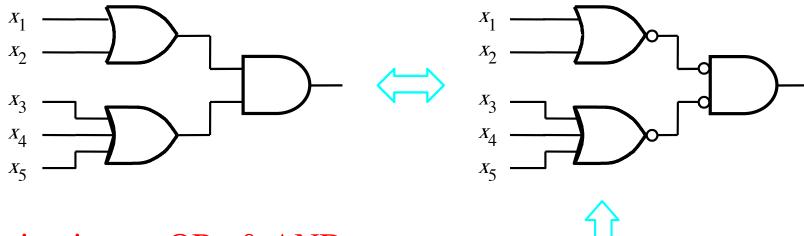

# NAND-NAND Implementation of Sum-of-Products Expressions

# NAND followed by NOT = AND

$$X_1$$

$X_2$

$X_1 \bullet X_2$

| $x_1$ | $x_2$ | <u>f</u> | <u>f</u> |

|-------|-------|----------|----------|

| 0     | 0     | 1        | 0        |

| 0     |       | 1        | 0        |

| 1     | 0     | 1        | 0        |

| 1     | 1     | 0        | 1        |

$$egin{array}{c|cccc} x_1 & x_2 & \mathbf{f} \\ \hline 0 & 0 & 0 \\ 0 & 1 & 0 \\ 1 & 0 & 0 \\ 1 & 1 & 1 \\ \hline \end{array}$$

## DeMorgan's Theorem

15a.

$$\overline{x \cdot y} = \overline{x} + \overline{y}$$

# DeMorgan's Theorem

15a.

$$\overline{x \cdot y} = \overline{x} + \overline{y}$$

$$= \frac{x}{y} = \frac{$$

This circuit uses only NANDs

This circuit uses only NANDs

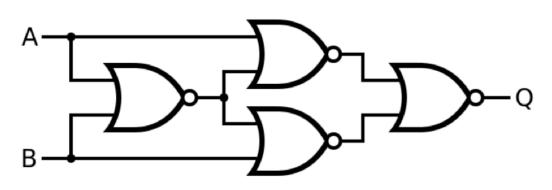

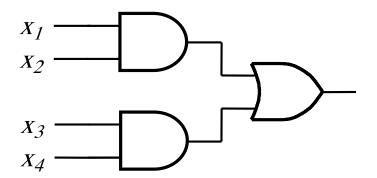

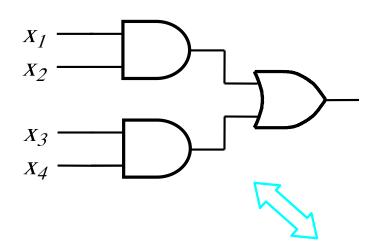

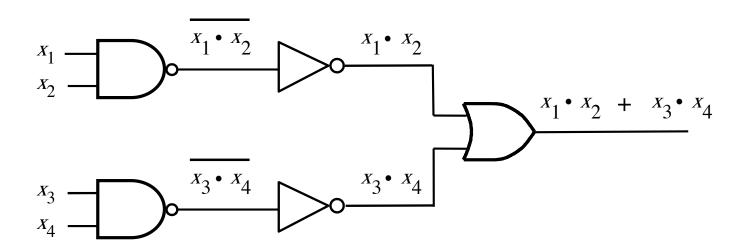

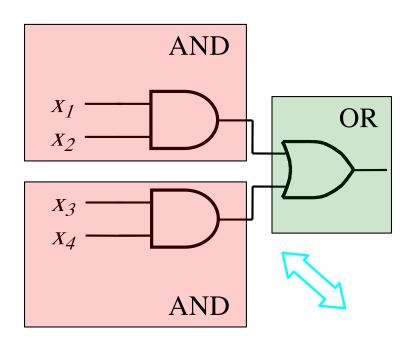

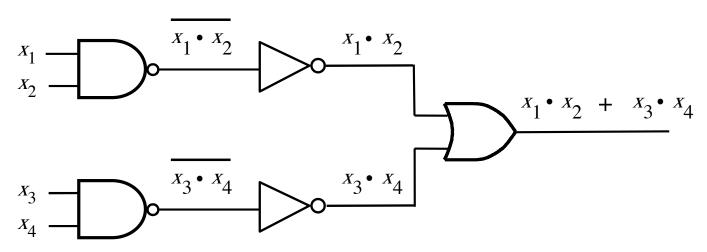

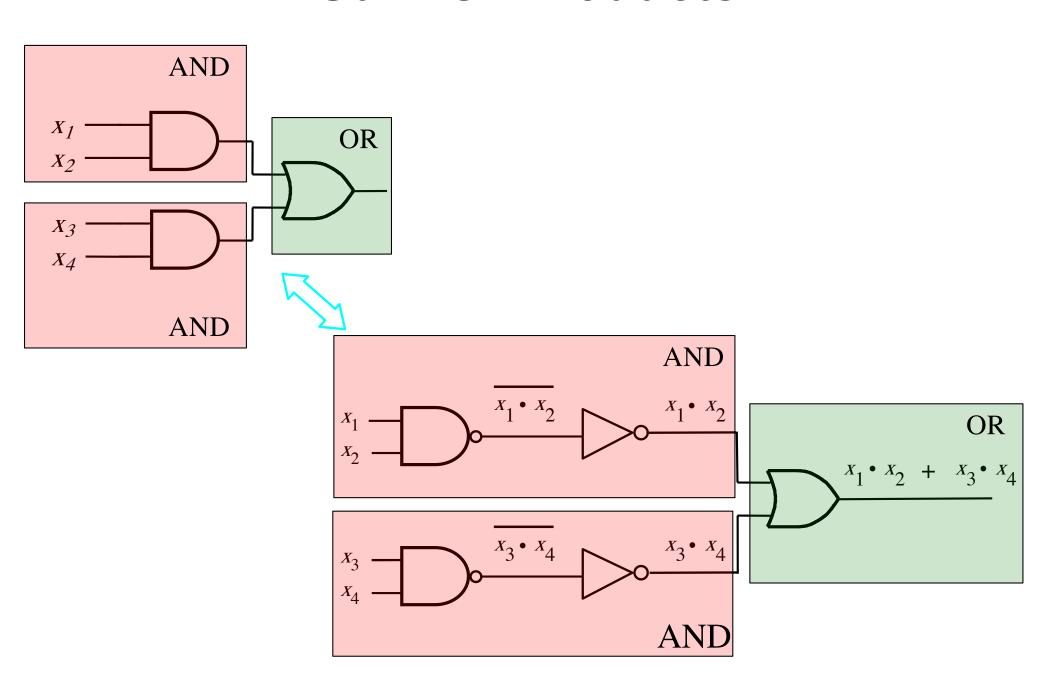

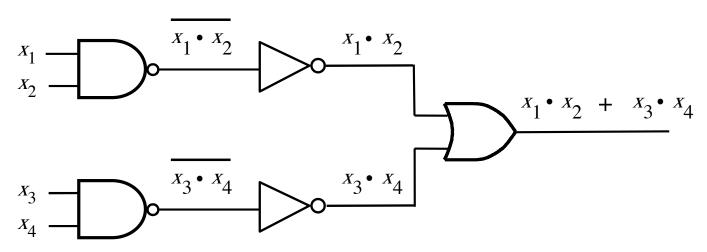

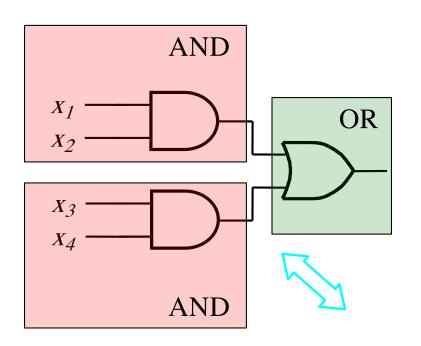

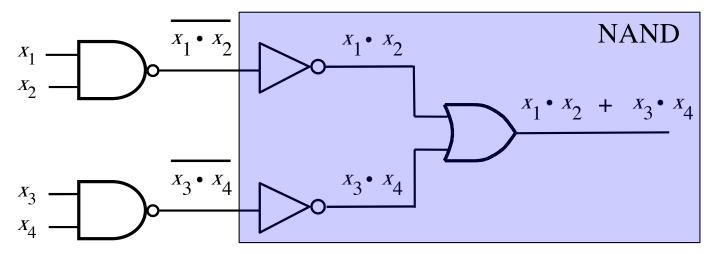

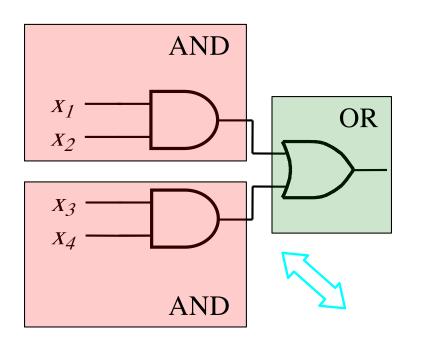

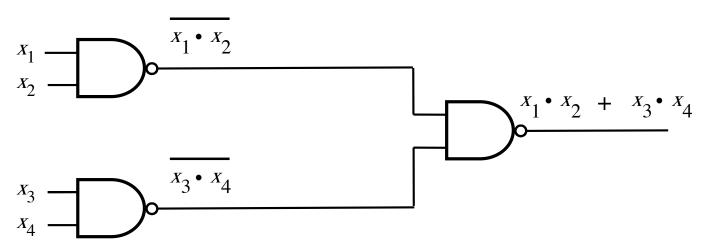

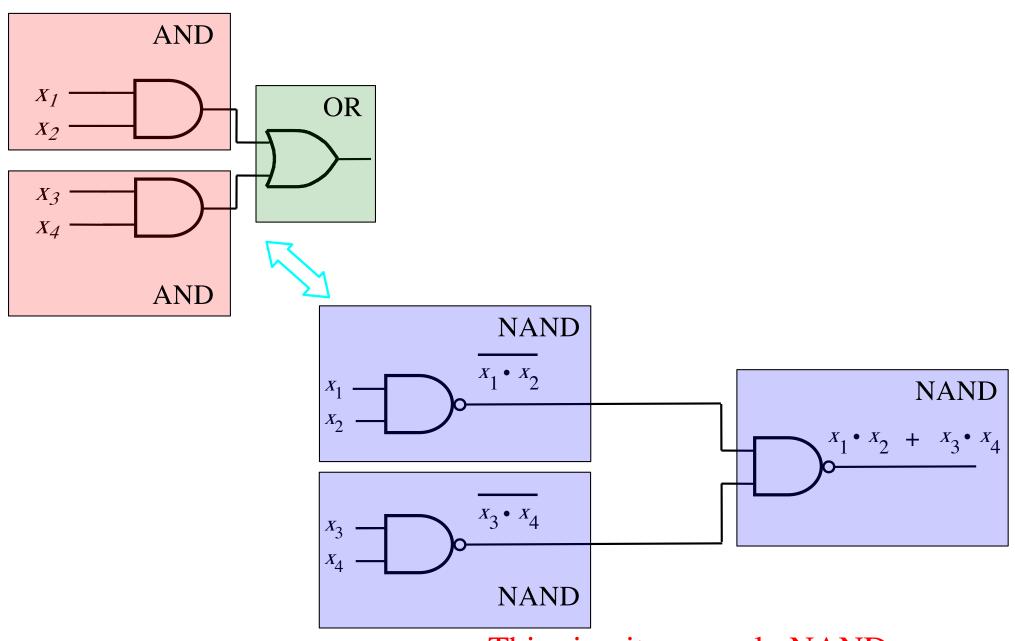

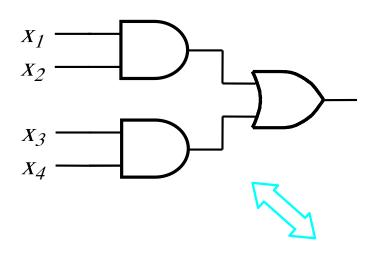

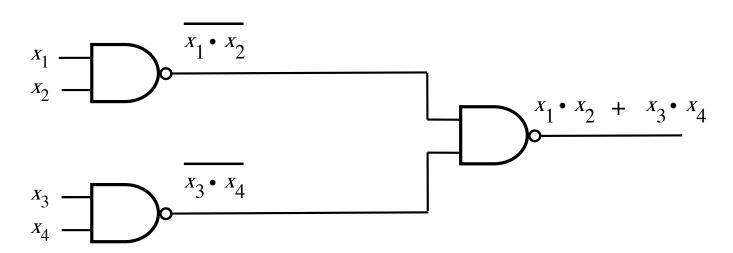

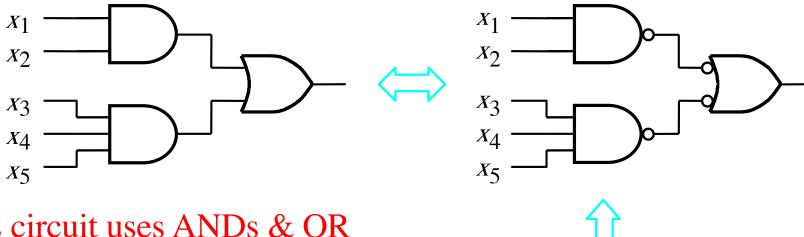

## **Another SOP Example**

This circuit uses ANDs & OR

This circuit uses only NANDs

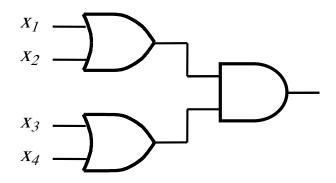

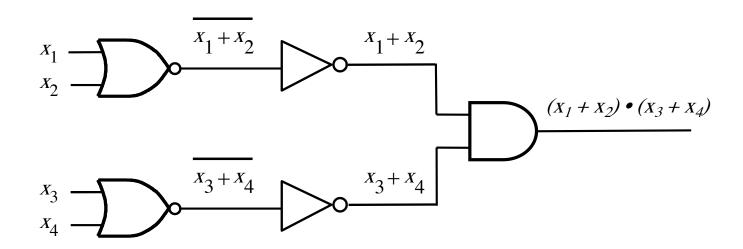

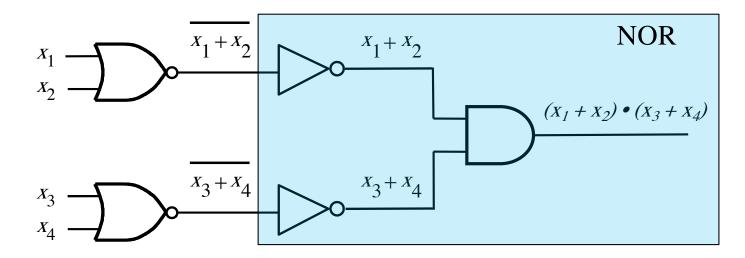

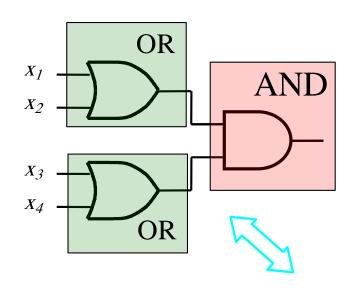

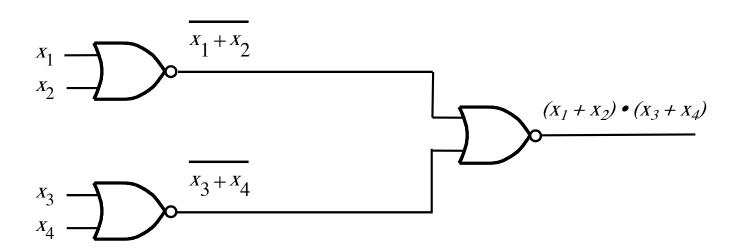

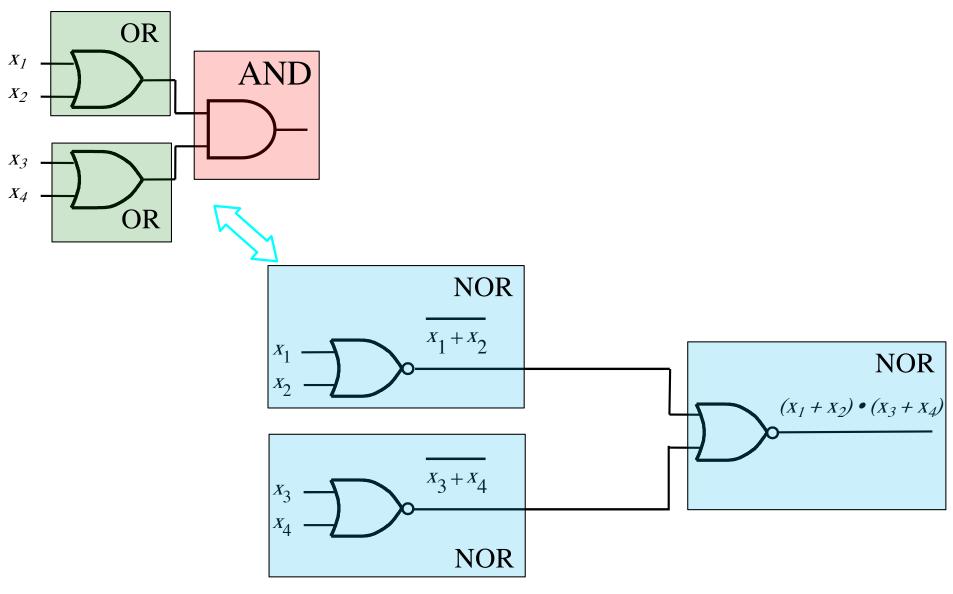

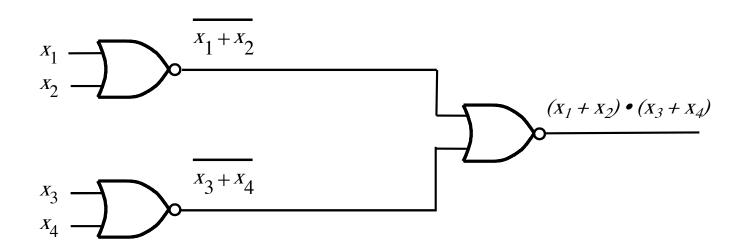

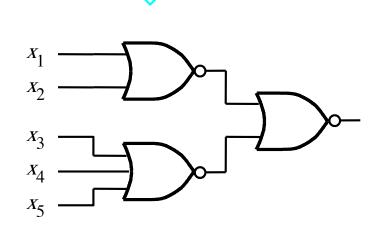

# NOR-NOR Implementation of Product-of-Sums Expressions

# NOR followed by NOT = OR

$$X_1$$

$X_2$

$X_1 + X_2$

| $x_1$ | $x_2$  | 1 | İ |

|-------|--------|---|---|

| 0     | 0      | 1 | 0 |

| 0     | 1<br>0 | 0 | 1 |

| 1     | 0      | 0 | 1 |

| 1     | 1      | 0 | 1 |

$$egin{array}{c|cccc} x_1 & x_2 & \mathbf{f} \\ \hline 0 & 0 & 0 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 1 \\ \hline \end{array}$$

## DeMorgan's Theorem

15b.

$$\overline{x + y} = \overline{x} \cdot \overline{y}$$

# DeMorgan's Theorem

15b.

$$\overline{x + y} = \overline{x} \cdot \overline{y}$$

$$= \bigvee_{X \to \overline{Y}} X + \overline{Y}$$

This circuit uses only NORs

This circuit uses only NORs

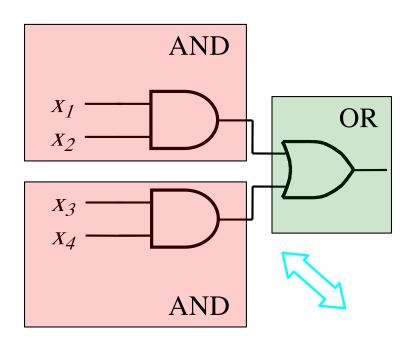

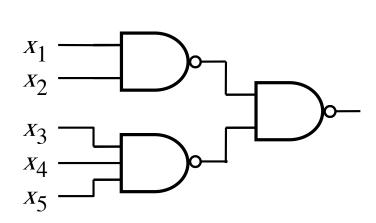

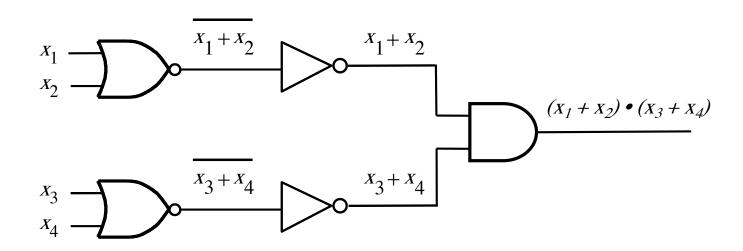

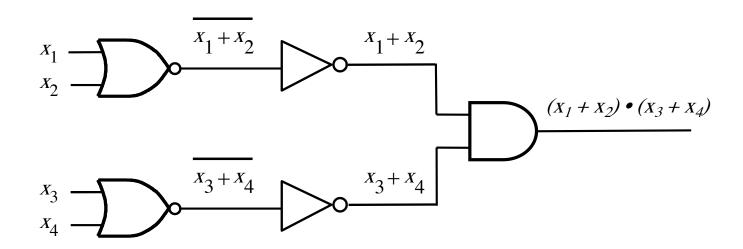

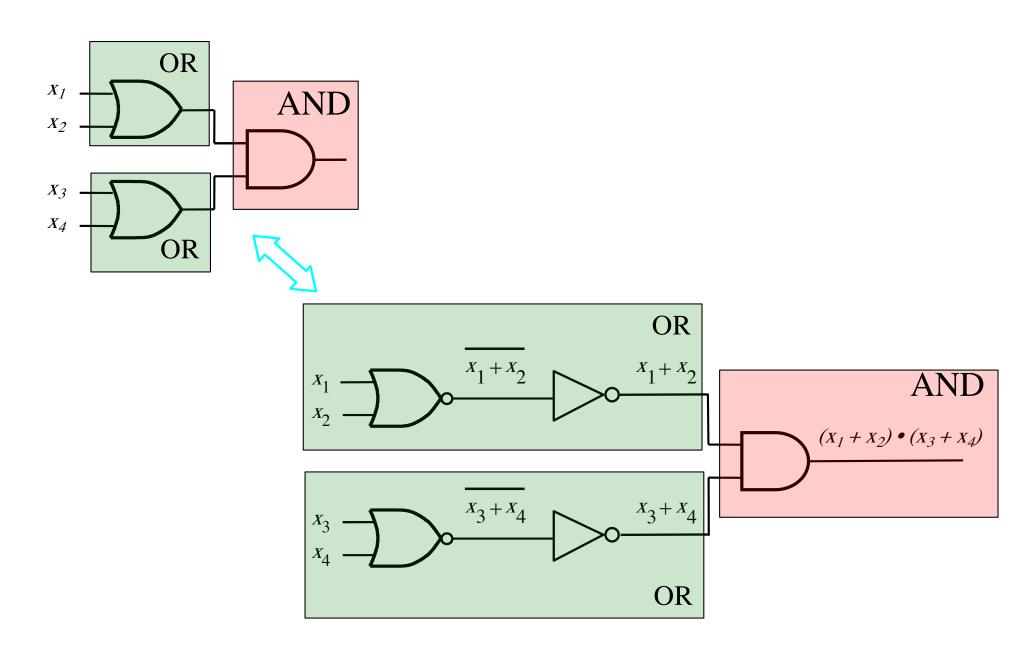

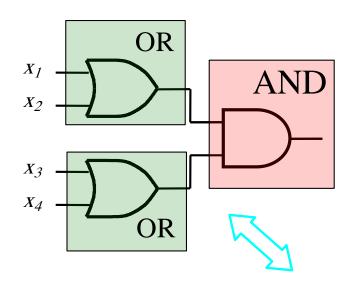

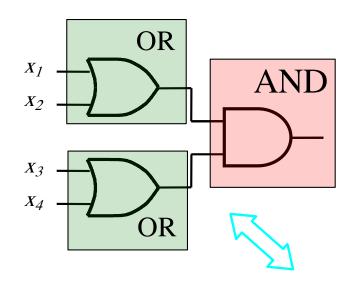

## **Another POS Example**

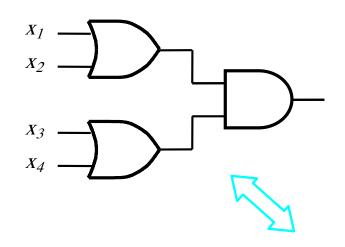

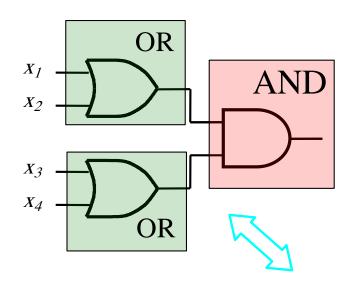

This circuit uses ORs & AND

This circuit uses only NORs

# **Questions?**

# THE END