# **CprE 281: Digital Logic**

Instructor: Alexander Stoytchev

http://www.ece.iastate.edu/~alexs/classes/

### **Logic Gates**

CprE 281: Digital Logic Iowa State University, Ames, IA Copyright © Alexander Stoytchev

#### **Administrative Stuff**

- HW1 is out. It is due on Monday Aug 30 @ 4pm.

- Submit it as a PDF upload on Canvas before the deadline.

- You can write the solutions on paper and then scan the pages to make \*\*one\*\* PDF file.

- No late homeworks will be accepted.

- Please write clearly on the first page:

- your name

- student ID

- lab section number

#### **Labs Next Week**

- Please download and read the lab assignment for next week before you go to your lab section.

- https://www.ece.iastate.edu/~alexs/classes/2021\_Fall\_281/labs/Lab\_01/

- You must print and complete the prelab before you go to the lab.

- The TAs will check your prelab answers at the beginning of the recitation. If you don't have it done you'll lose 20% of the lab grade for that lab.

Fall 2021, 4:25 - 5:15 p.m. (Mondays, Wednesdays, and Fridays)

LeBaron Hall, Room 1210

**Instructor:** Alexander Stoytchev

- Syllabus

- Class Schedule (Tentative)

- <u>Lecture Notes</u> (also in <u>PDF</u>)

- Labs

$\leftarrow$   $\rightarrow$  C

- Recitations

- Extra Readings

- Verilog Stuff

- Verilog Reference

- i281 CPU

### CprE 281: Digital Logic

Fall 2021, 4:25 - 5:15 p.m. (Mondays, Wednesdays, and Fridays)

LeBaron Hall, Room 1210

**Instructor:** Alexander Stoytchev

- Syllabus

- Class Schedule (Tentative)

- Lecture Notes (also in PDF)

- Labs

- Recitations

- Extra Readings

- Verilog Stuff

- <u>Verilog Reference</u>

- i281 CPU

#### Index of /~alexs/classes/2021\_Fall\_281/labs

| <u>Name</u>      | <b>Last modified</b> | Size Description |

|------------------|----------------------|------------------|

| Parent Directory | <u>/</u>             |                  |

| <u>Lab_01/</u>   | 27-Aug-2021 14:06    | -                |

| <u>Lab_02/</u>   | 27-Aug-2021 14:09    | -                |

Apache/2.2.15 (Red Hat) Server at www.ece.iastate.edu Port 80

#### Index of /~alexs/classes/2021\_Fall\_281/labs/Lab\_01

| <u>Name</u>            | <b>Last modified</b>          | Size Description |

|------------------------|-------------------------------|------------------|

| Parent Directory       |                               |                  |

| CPRE281_LAB01(Answer_S | Sheet).docx 27-Aug-2021 14:02 | 26K              |

| CPRE281_LAB01(Answer_S |                               |                  |

| CPRE281_LAB01.docx     | 27-Aug-2021 14:04             | 1.9M             |

| CPRE281_LAB01.pdf      | 27-Aug-2021 14:04             | 1.4M             |

| lab1.zip               | 27-Aug-2021 13:56             | 5.4M             |

|                        |                               |                  |

Apache/2.2.15 (Red Hat) Server at www.ece.iastate.edu Port 80

#### Index of /~alexs/classes/2021\_Fall\_281/labs/Lab\_01

| Name Last modified                                                                                                                                                                                                                                                                              | Size Description                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Parent Directory         CPRE281_LAB01(Answer_Sheet).docx       27-Aug-2021 14:02         CPRE281_LAB01(Answer_Sheet).pdf       27-Aug-2021 14:03         CPRE281_LAB01.docx       27-Aug-2021 14:04         CPRE281_LAB01.pdf       27-Aug-2021 14:04         Iab1.zip       27-Aug-2021 13:56 | and bring it with you to the lab. |

Apache/2.2.15 (Red Hat) Server at www.ece.iastate.edu Port 80

#### Index of /~alexs/classes/2021\_Fall\_281/labs/Lab\_01

| <u>Name</u>                 | Last modified | Size I               | <u>Description</u>                   |

|-----------------------------|---------------|----------------------|--------------------------------------|

| <u>CPRE281_LAB01.pdf</u> 27 | _             | 338K<br>1.9M<br>1.4M | This is the same, but in PDF format. |

Apache/2.2.15 (Red Hat) Server at www.ece.iastate.edu Port 80

## Cpr E 281 LAB1 ELECTRICAL AND COMPUTER ENGINEERING IOWA STATE UNIVERSITY

1

0

1

1

1

Logic Expression:

Date:\_\_

#### Lab 1 Answer Sheet

Lab Section:\_\_\_

| PRELAE                                                                                                   | 3:            |                        |                  |  |

|----------------------------------------------------------------------------------------------------------|---------------|------------------------|------------------|--|

| Q1. Fill i                                                                                               | in the Truth  | Table below            | for an AND gate: |  |

| Α                                                                                                        | В             | С                      |                  |  |

| 0                                                                                                        | 0             |                        |                  |  |

| 0                                                                                                        | 1             |                        |                  |  |

| 1                                                                                                        | 0             |                        |                  |  |

| 1                                                                                                        | 1             |                        |                  |  |

| Q2. What does the .bdf file extension stand for?  Q3. What is the name of the FPGA on the DE2-115 board? |               |                        |                  |  |

| TA Initia                                                                                                | ls:           | _                      |                  |  |

| LAB:<br>2.0 Fill in                                                                                      | n the Truth 1 | Γable for <i>lαb</i> . | 1step1:          |  |

| Α                                                                                                        | В             | С                      |                  |  |

| 0                                                                                                        | 0             |                        |                  |  |

Name and Student ID:

This is the prelab for lab #1.

## Cpr E 281 LAB1 ELECTRICAL AND COMPUTER ENGINEERING IOWA STATE UNIVERSITY

#### Lab 1 Answer Sheet

| V                        | X                         | Y                    | Z             |   |

|--------------------------|---------------------------|----------------------|---------------|---|

| )                        | 0                         | 0                    |               |   |

| :                        |                           | 1                    |               | : |

|                          |                           | 0                    |               | i |

|                          |                           | 1                    |               |   |

|                          |                           | 0                    |               |   |

|                          |                           | 1                    |               | ; |

|                          |                           | 0                    |               |   |

|                          |                           |                      |               |   |

| xpr                      | ession:<br>:              |                      |               |   |

| xpr<br>ials<br>in        | ession:<br>:<br>the Truth | Table for <i>lal</i> | b1step3:      |   |

| xpr<br>ials              | ession:<br>:<br>the Truth | Table for <i>lal</i> | 51step3:<br>F |   |

| Expr<br>tials            | ession:<br>:<br>the Truth | Table for <i>lal</i> | 51step3:<br>F |   |

| Expr<br>itials<br>ill in | ession:<br>:<br>the Truth | Table for <i>lal</i> | o1step3:<br>F |   |

| Expr<br>nitials          | ession:<br>:<br>the Truth | Table for <i>lal</i> | o1step3:<br>F |   |

| Expr<br>nitials          | the Truth                 | Table for <i>lal</i> | o1step3:      |   |

| Expr<br>itials           | the Truth                 | Table for <i>lal</i> | o1step3:      |   |

| Expr<br>nitials          | the Truth                 | Table for <i>lal</i> | o1step3:      |   |

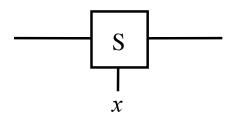

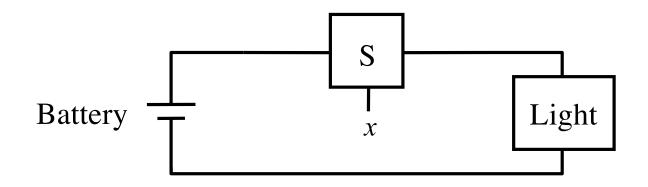

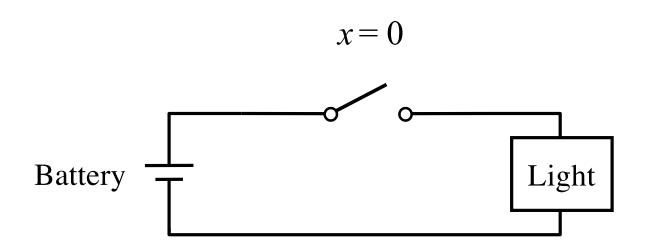

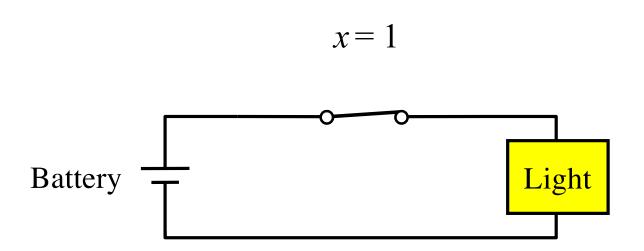

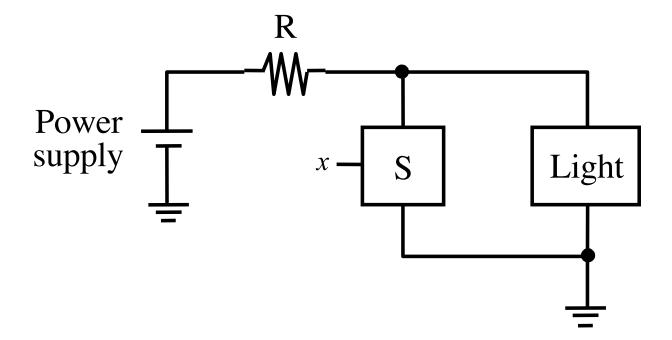

### **A Binary Switch**

(a) Two states of a switch

(b) Symbol for a switch

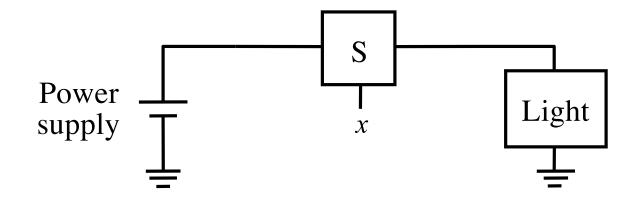

(a) Simple connection to a battery

(b) Using a ground connection as the return path

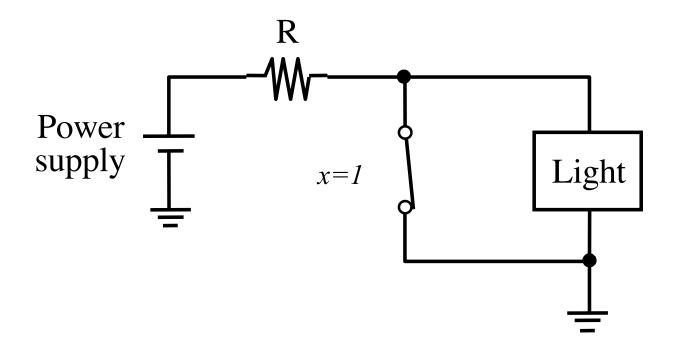

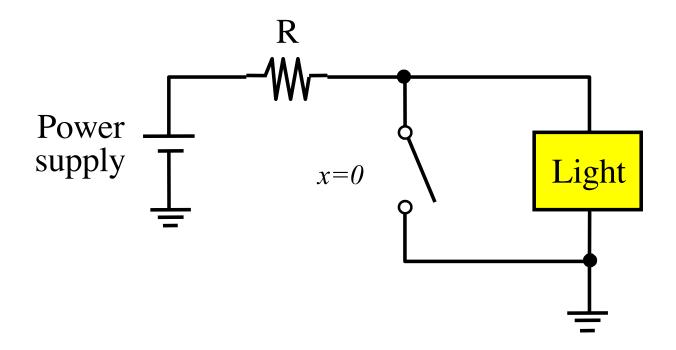

### **An Inverting Circuit**

### **An Inverting Circuit**

### **An Inverting Circuit**

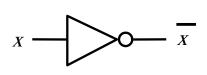

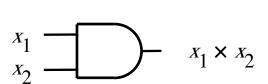

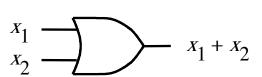

### The Three Basic Logic Gates

$$X_1$$

$X_2$

$X_1 \times X_2$

$$X_1$$

$X_2$

$X_1 + X_2$

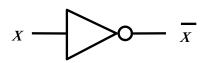

NOT gate

AND gate

**OR** gate

#### **Truth Table for NOT**

| $\mathcal{X}$ | $\overline{\mathcal{X}}$ |

|---------------|--------------------------|

| 0             | 1                        |

| 1             | 0                        |

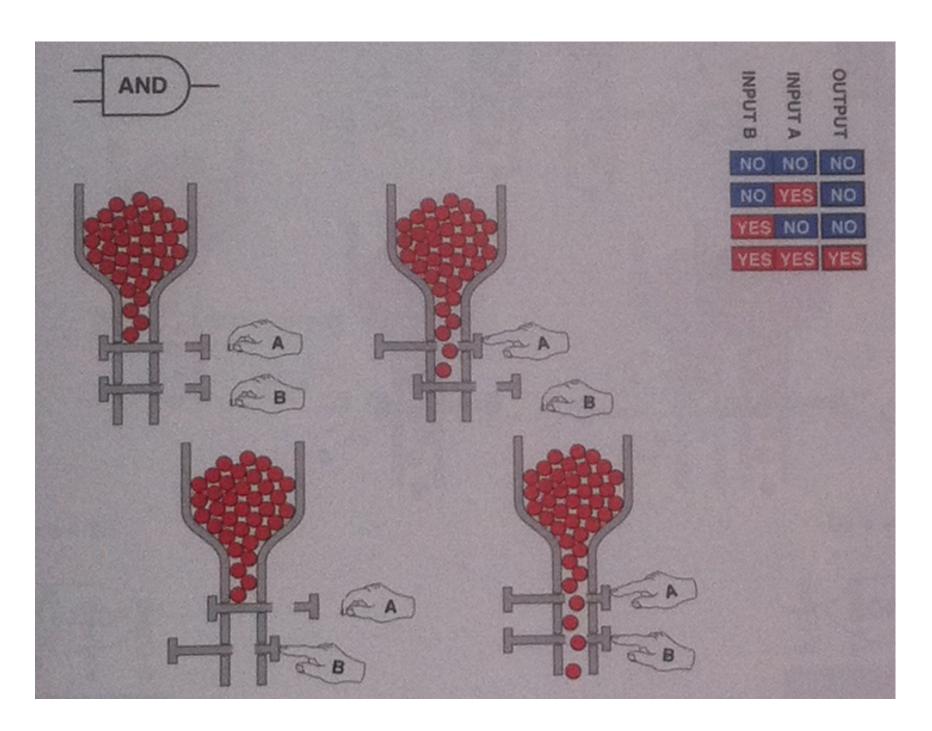

### **Truth Table for AND**

| $x_1$ | $x_2$ | $x_1 \cdot x_2$ |

|-------|-------|-----------------|

| 0     | 0     | 0               |

| 0     | 1     | 0               |

| 1     | 0     | 0               |

| 1     | 1     | 1               |

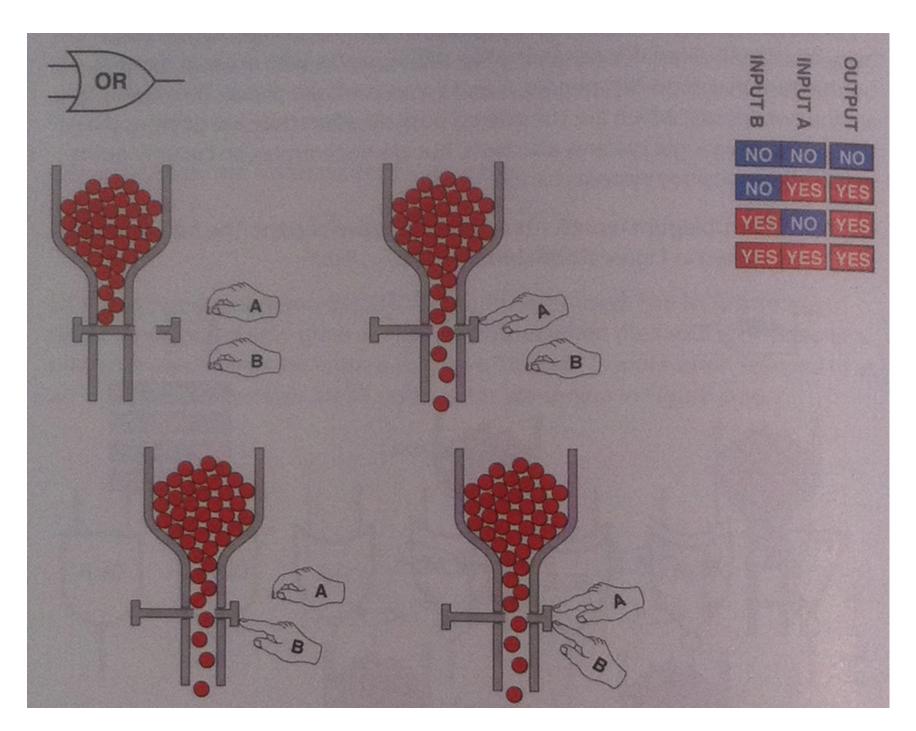

### **Truth Table for OR**

| $x_1 + x_2$ |

|-------------|

| 0           |

| 1           |

| 1           |

| 1           |

|             |

#### Truth Tables for AND and OR

| $x_1$ | $x_2$ | $oxed{x_1  x_2}$ | $x_1 + x_2$ |

|-------|-------|------------------|-------------|

| 0     | 0     | 0                | 0           |

| 0     | 1     | 0                | 1           |

| 1     | 0     | 0                | 1           |

| 1     | 1     | 1                | 1           |

AND OR

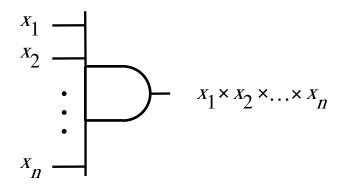

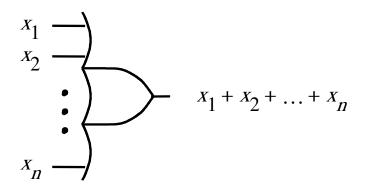

#### **Logic Gates with n Inputs**

AND gate

OR gate

## Truth Table for 3-input AND and OR

| $x_1$ | $x_2$ | $x_3$    | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ | $x_1 + x_2 + x_3$ |

|-------|-------|----------|--------------------------------------------------------|-------------------|

| 0     | 0     | 0        | 0                                                      | 0                 |

| 0     | 0     | 1        | 0                                                      | 1                 |

| 0     | 1     | 0        | 0                                                      | 1                 |

| 0     | 1     | 1        | 0                                                      | 1                 |

| 1     | 0     | 0        | 0                                                      | 1                 |

| 1     | 0     | 1        | 0                                                      | 1                 |

| 1     | 1     | 0        | 0                                                      | 1                 |

| 1     | 1     | $1 \mid$ | 1                                                      | 1                 |

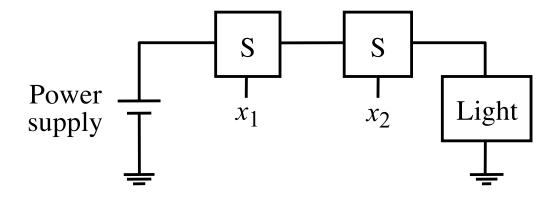

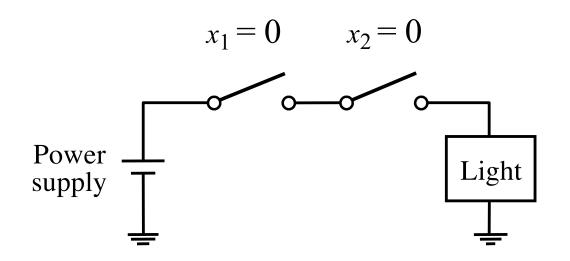

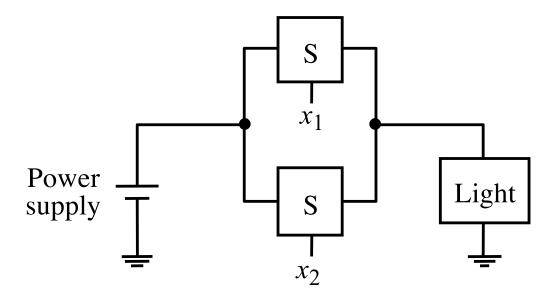

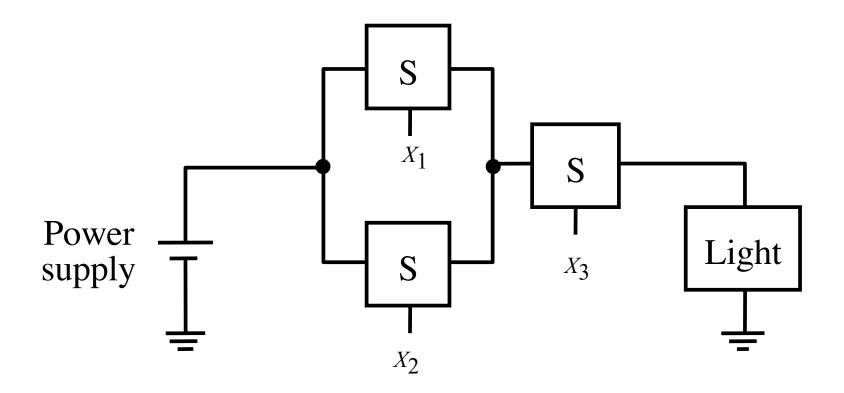

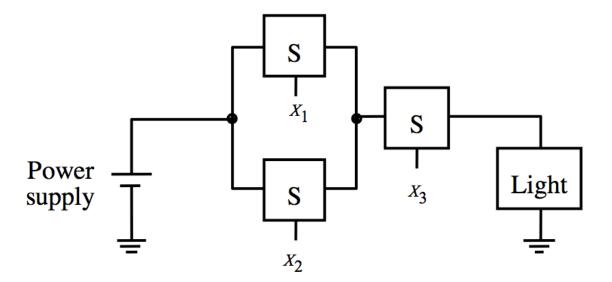

## A series-parallel connection of the switches

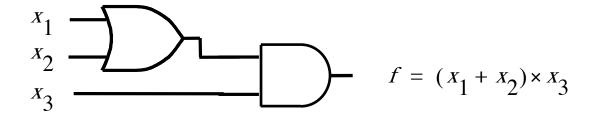

# **Example of a Logic Circuit Implemented with Logic Gates**

$$x_{1}$$

$x_{2}$

$x_{3}$

$f = (x_{1} + x_{2}) \times x_{3}$

# **Example of a Logic Circuit**Implemented with Logic Gates

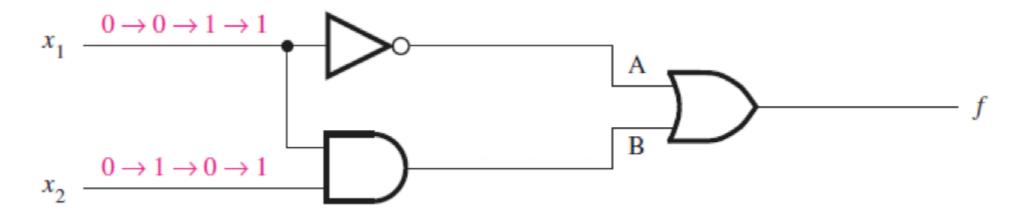

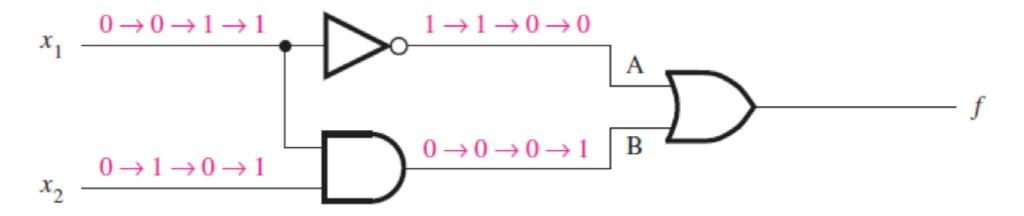

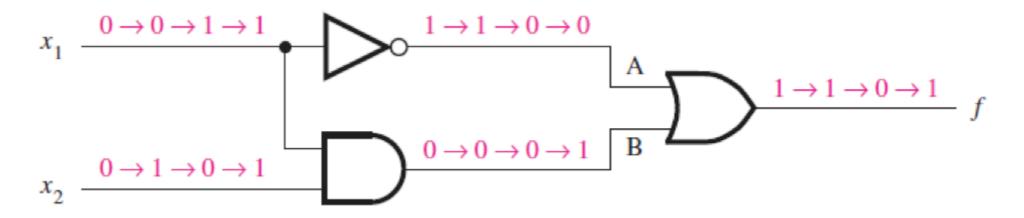

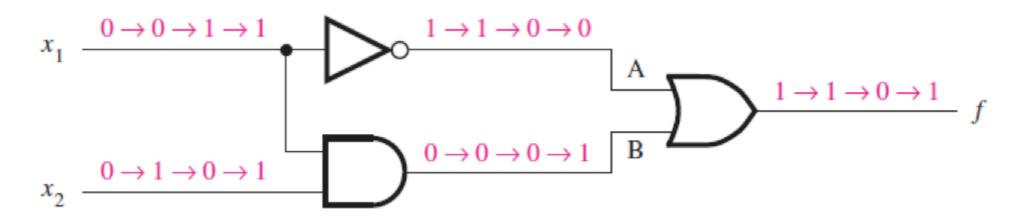

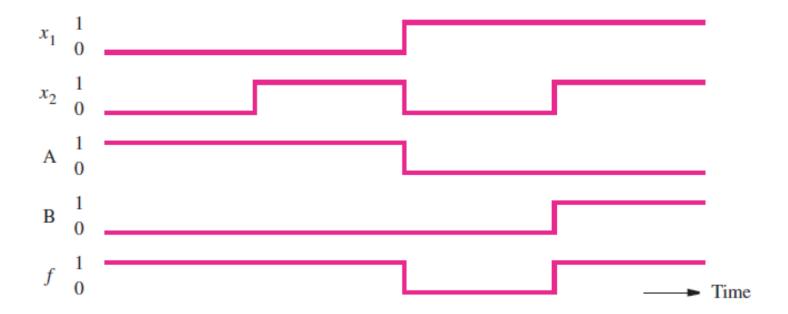

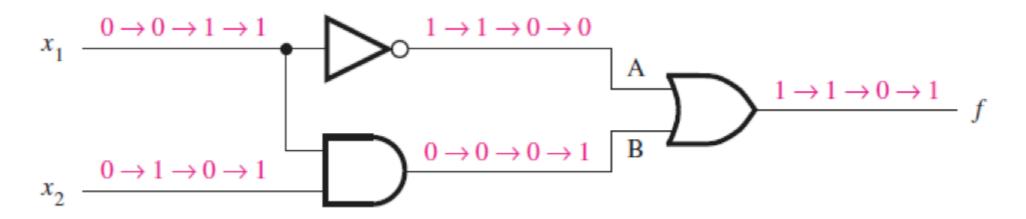

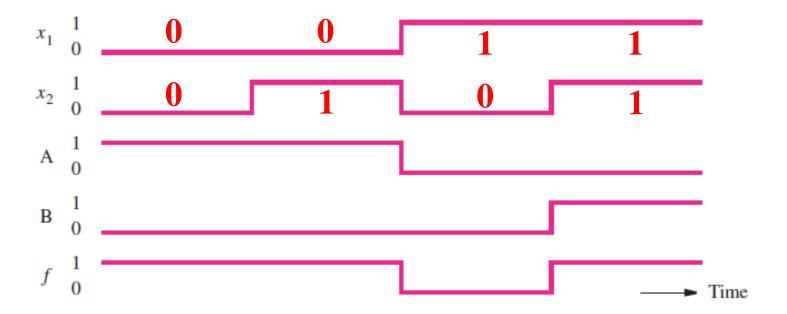

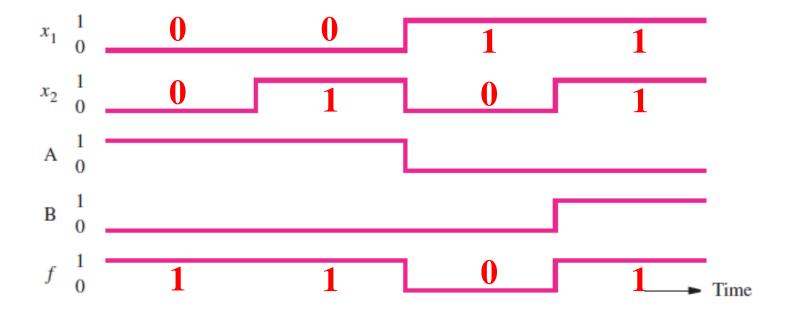

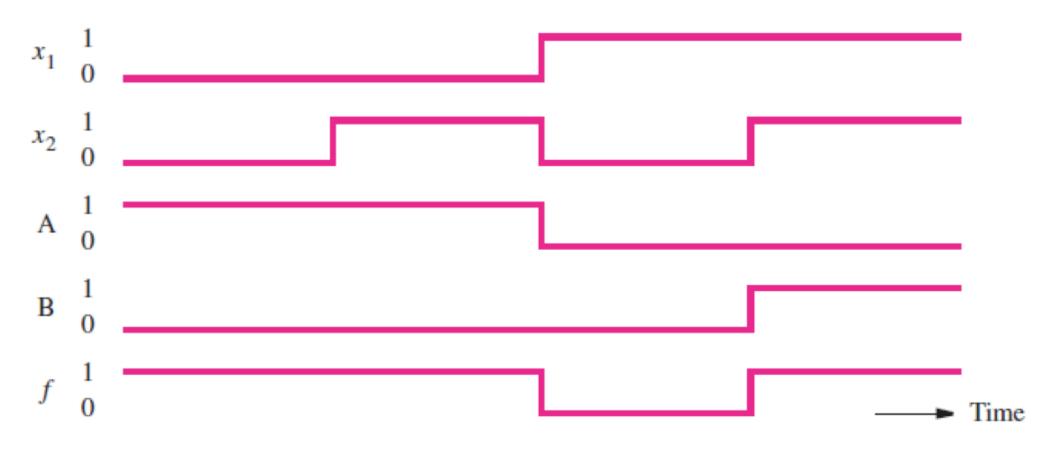

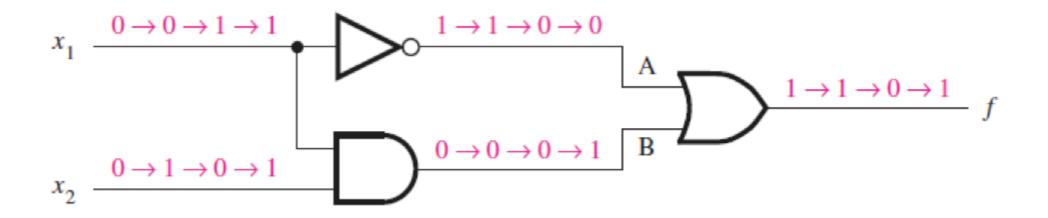

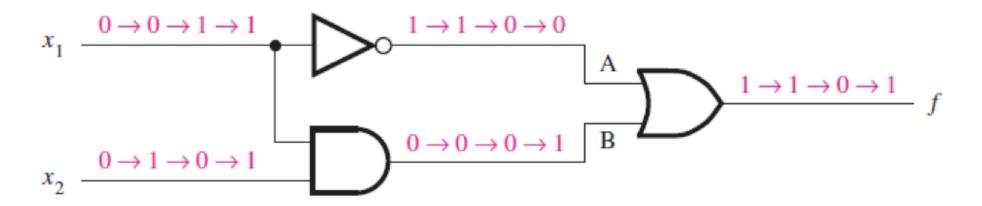

## **Timing Diagram**

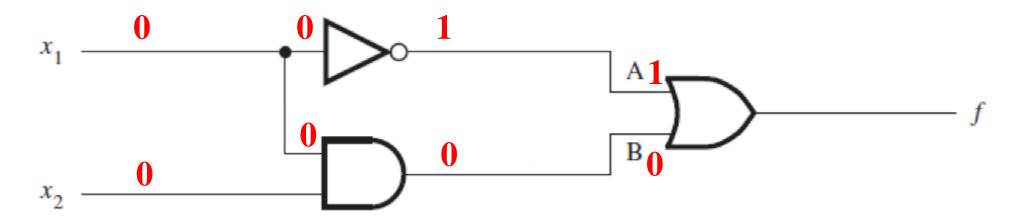

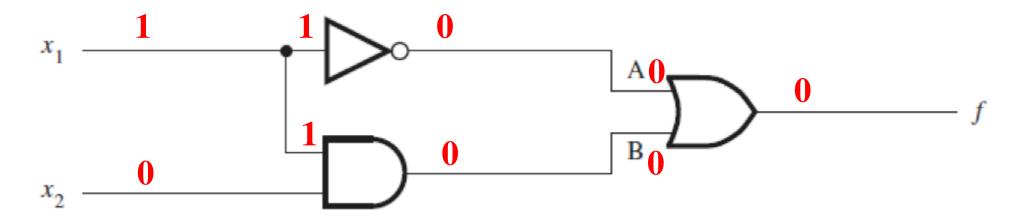

#### **Truth Table for this Logic Circuit**

| $x_1$ $x_2$ $f(x_1)$ | $(x_{2})$ |

|----------------------|-----------|

| 0 0                  | 1         |

| 0 1                  | 1         |

| 1 0 (                | 0         |

| 1 1                  | 1         |

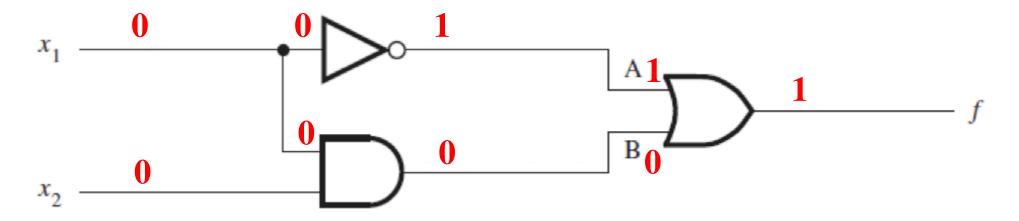

#### **Truth Table for this Logic Circuit**

| $x_1$ | $x_2$ | $f(x_1, x_2)$ |

|-------|-------|---------------|

| 0     | 0     | 1             |

| 0     | 1     | 1             |

| 1     | 0     | 0             |

| 1     | 1     | 1             |

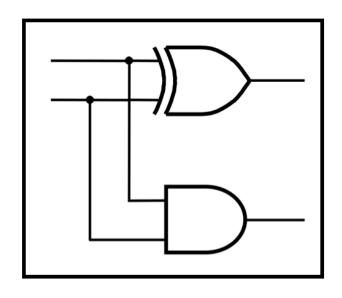

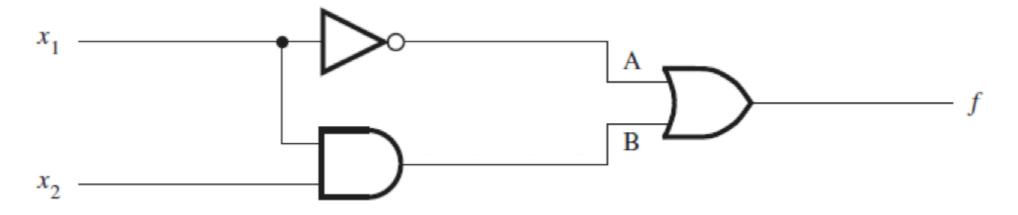

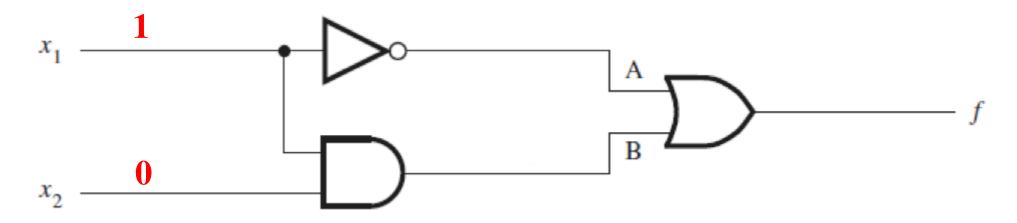

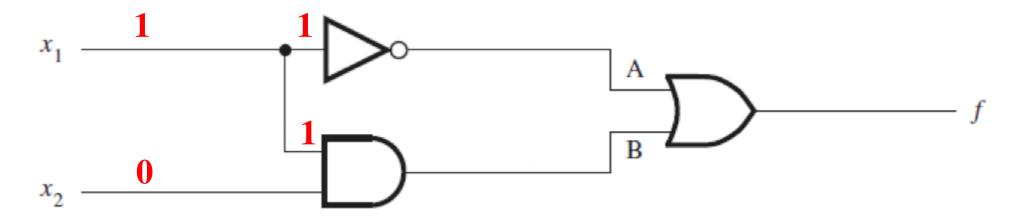

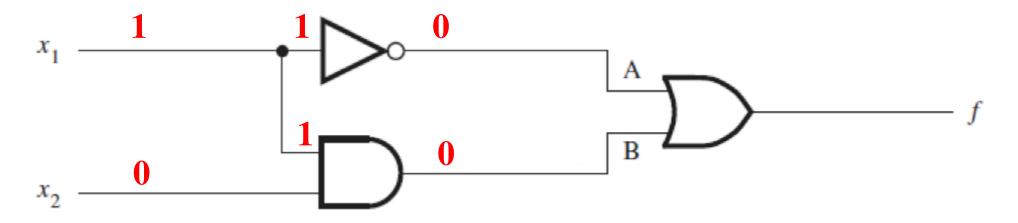

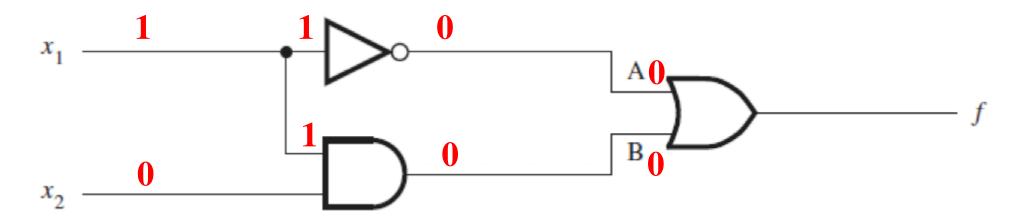

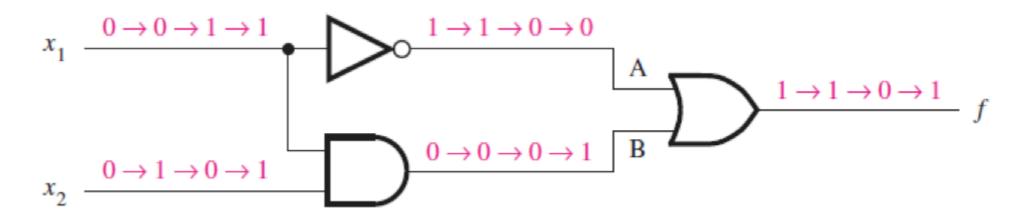

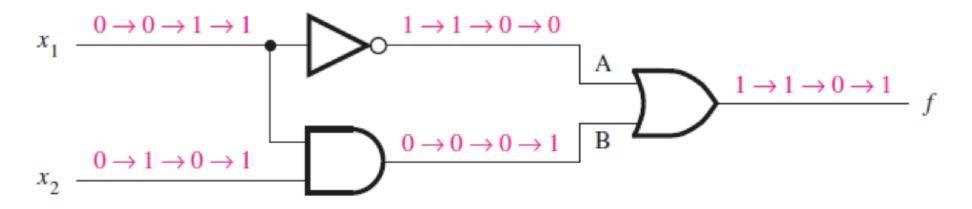

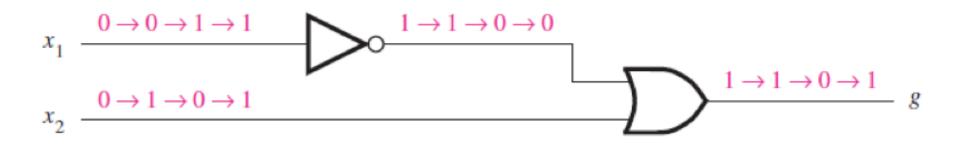

#### **Functionally Equivalent Circuits**

#### **Functionally Equivalent Circuits**

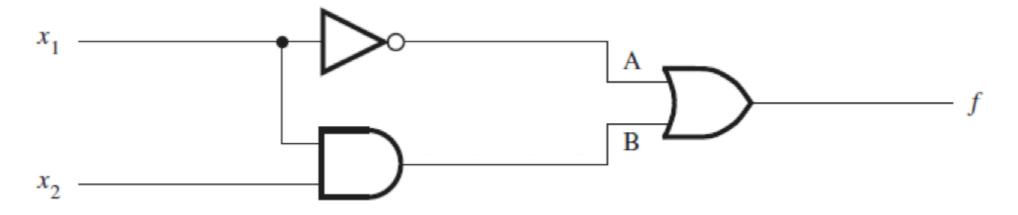

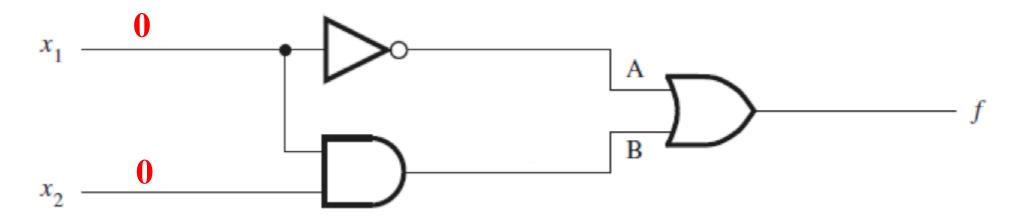

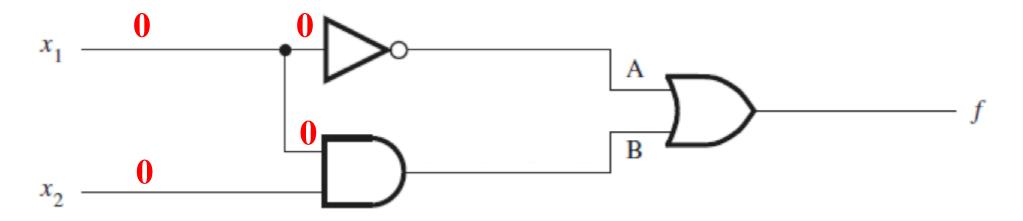

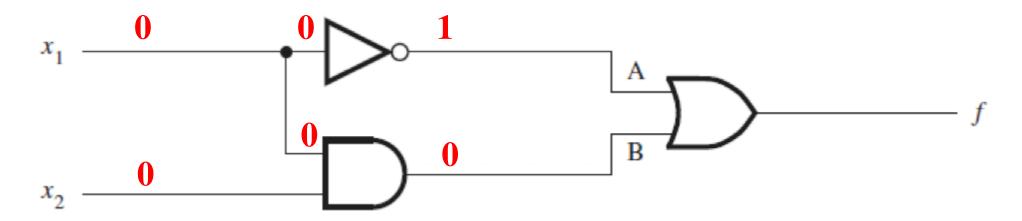

(a) Network that implements  $f = \bar{x}_1 + x_1 \cdot x_2$

(d) Network that implements  $g = \bar{x}_1 + x_2$

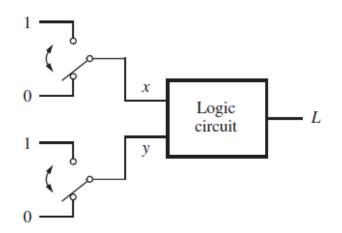

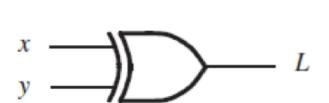

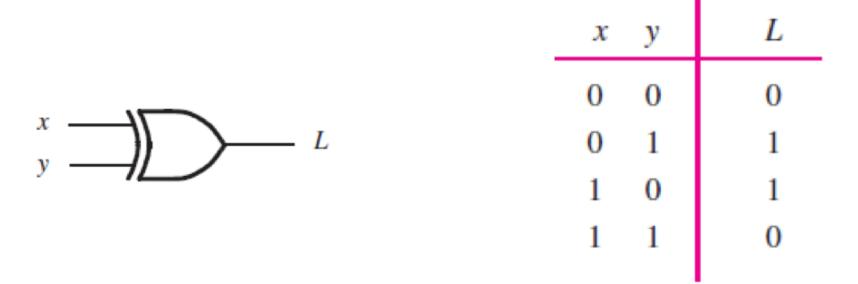

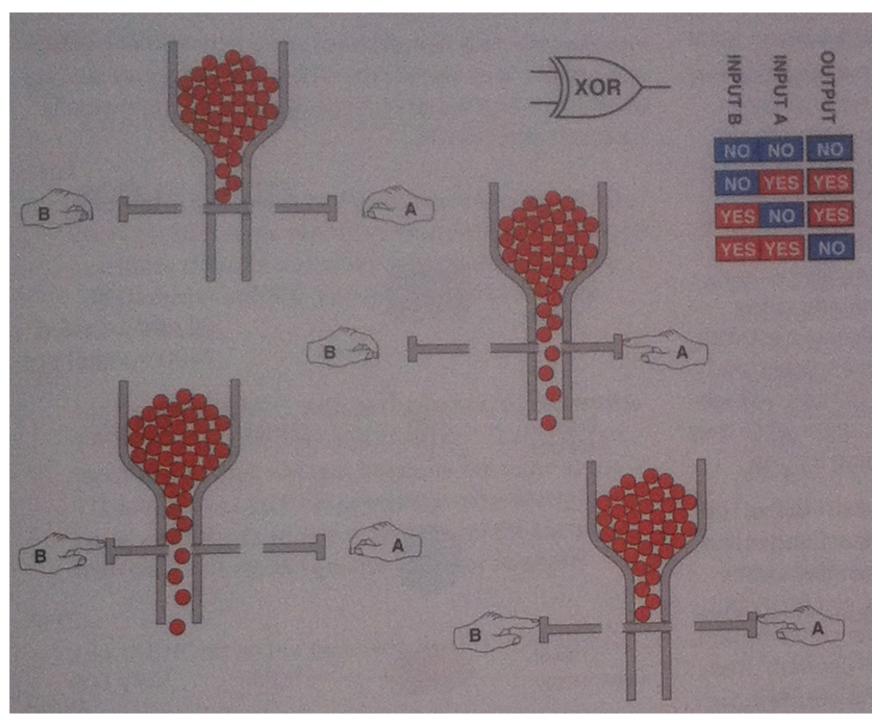

#### The XOR Logic Gate

| х | y | L |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

|   |   |   |

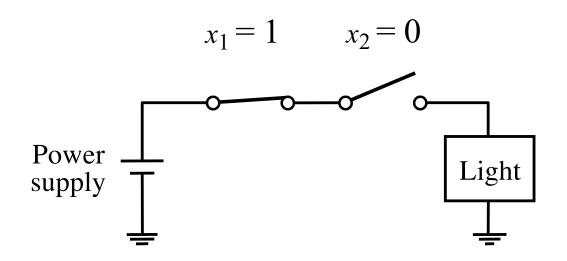

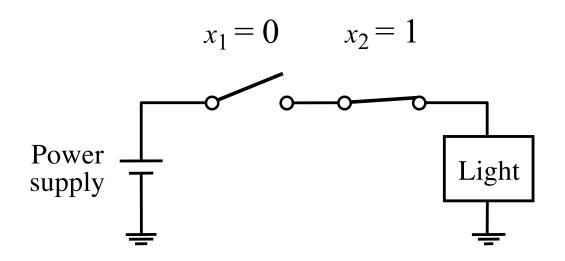

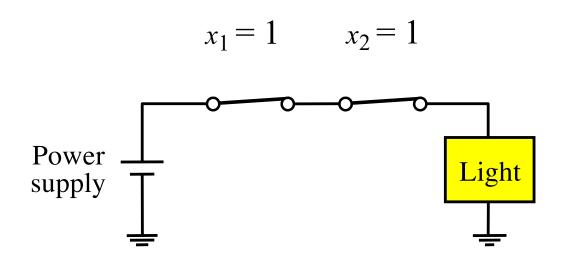

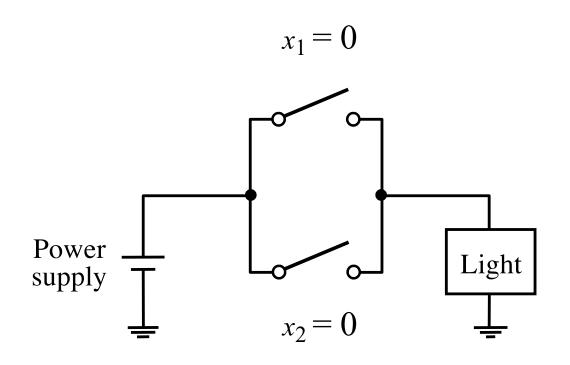

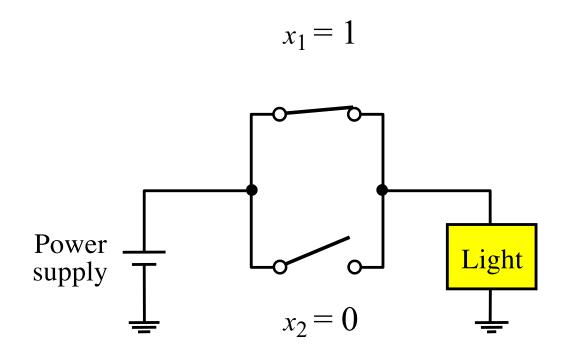

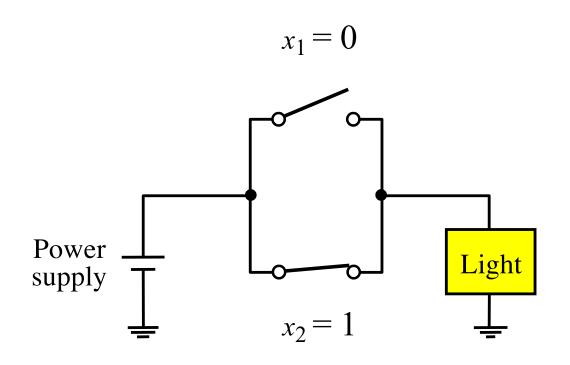

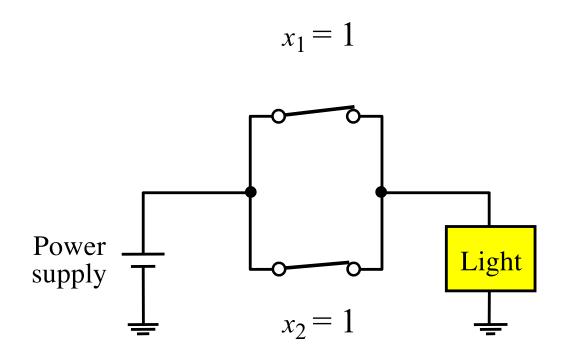

(a) Two switches that control a light

(b) Truth table

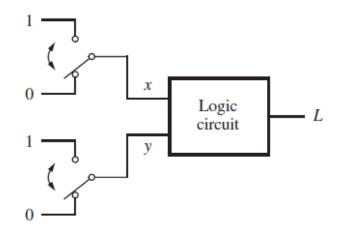

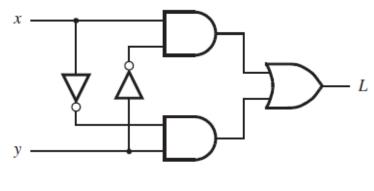

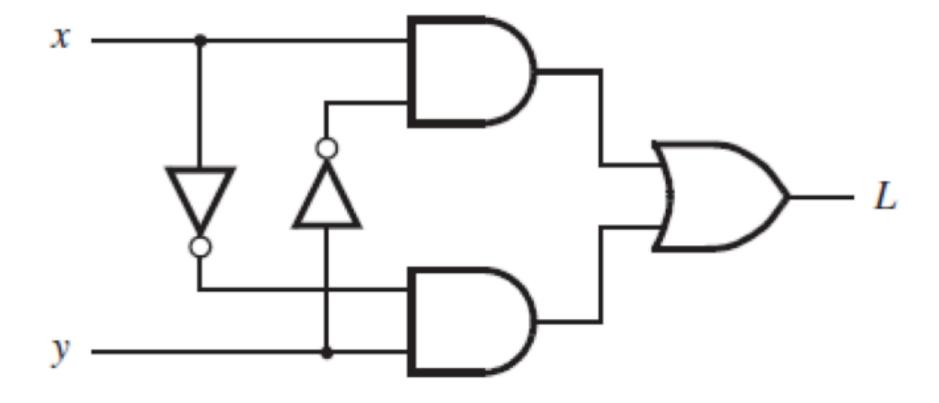

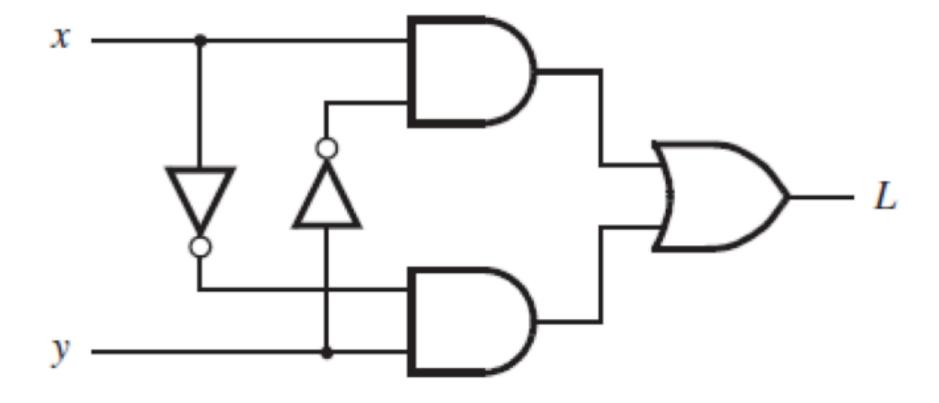

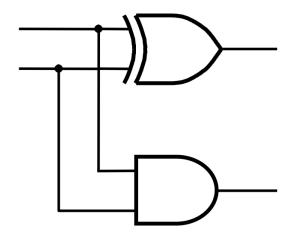

#### The XOR Logic Gate

| х | у | L |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

|   |   |   |

(a) Two switches that control a light

(b) Truth table

(c) Logic network

(d) XOR gate symbol

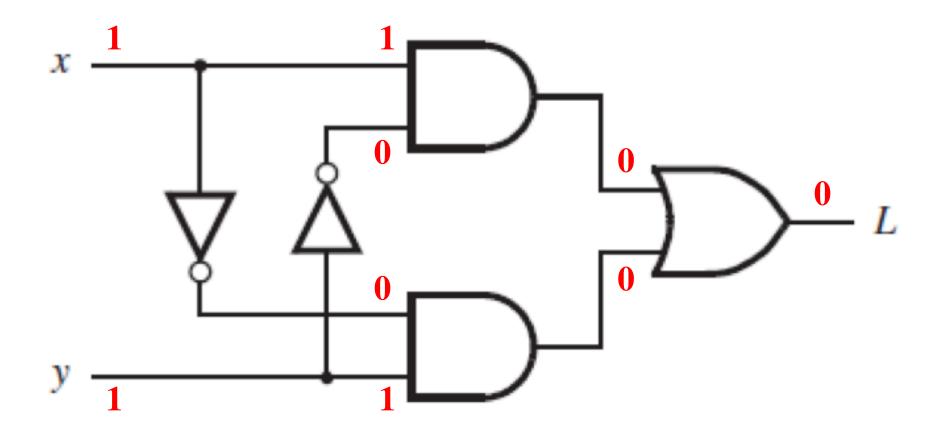

### **XOR Analysis**

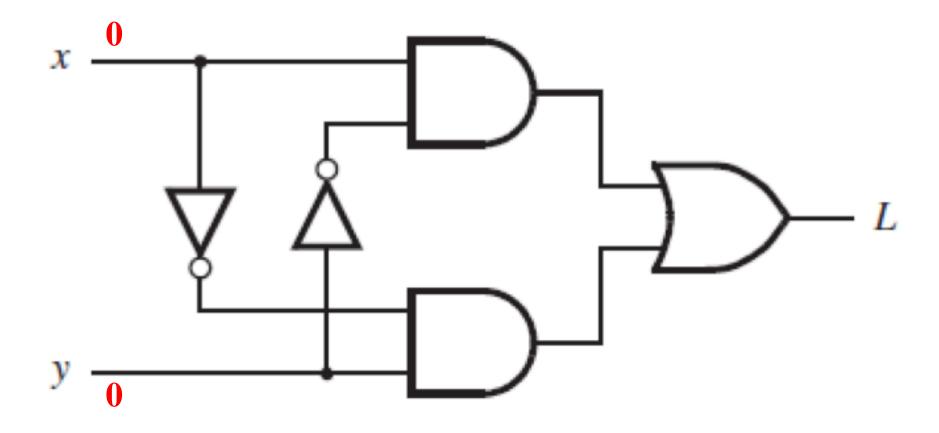

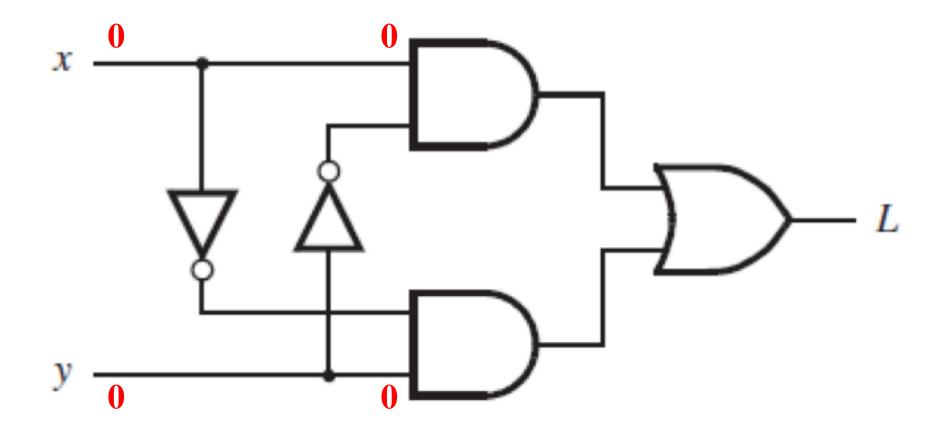

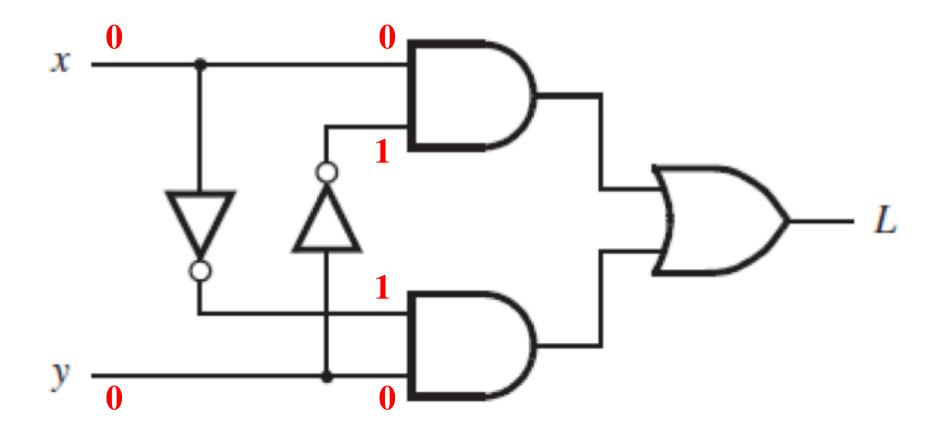

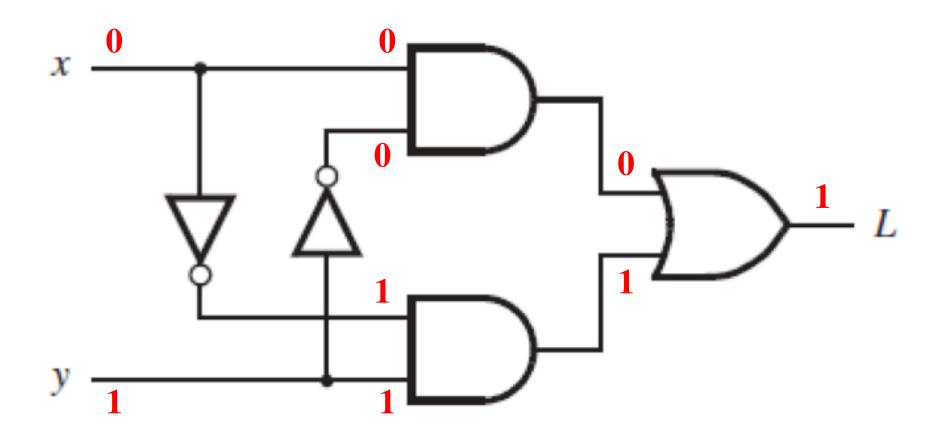

# XOR Analysis (x=0, y=0)

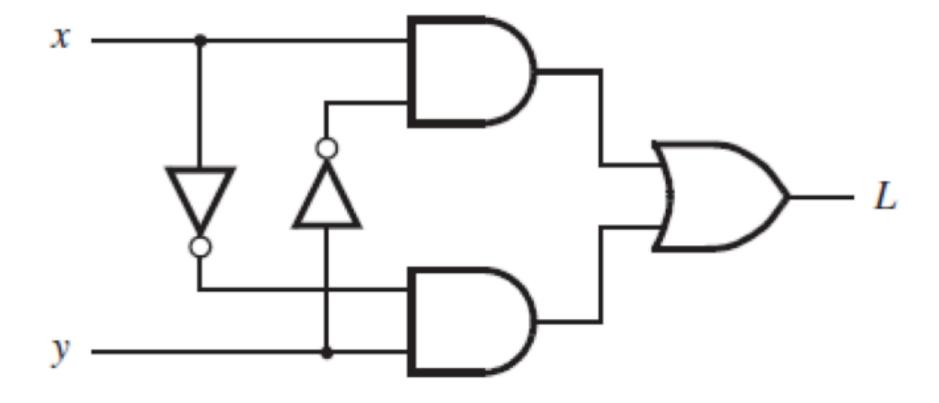

### **XOR Analysis**

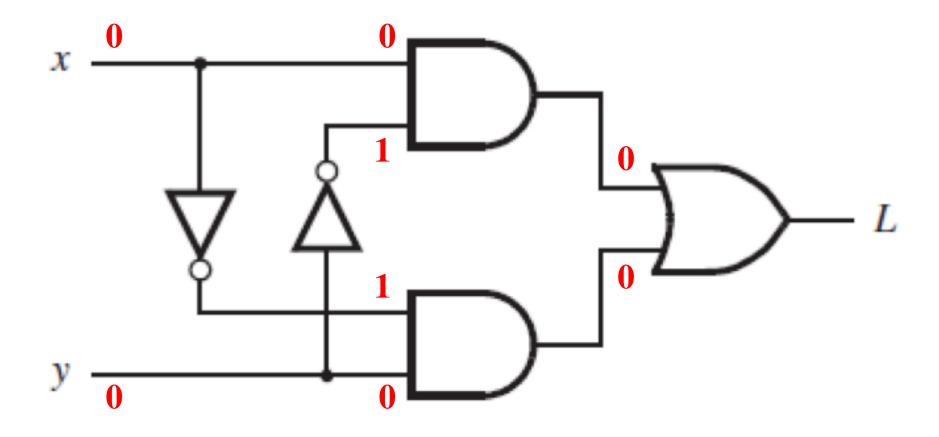

# XOR Analysis (x=0, y=1)

### **XOR Analysis**

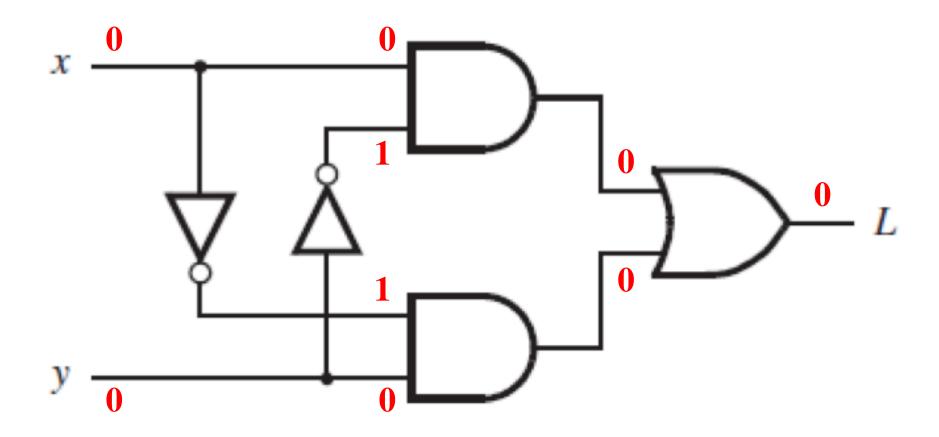

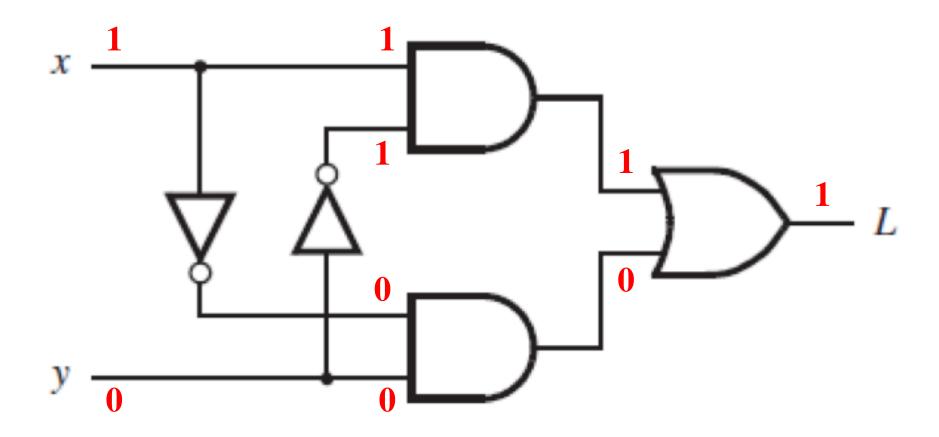

# XOR Analysis (x=1, y=0)

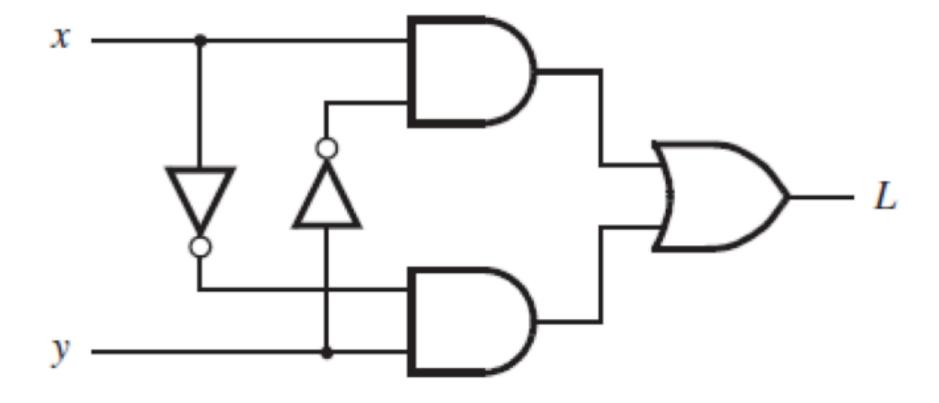

### **XOR Analysis**

# XOR Analysis (x=1, y=1)

#### **Truth Table for XOR**

| х | y | L |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

|   |   |   |

#### **Truth Table for XOR**

The output is 1 only if both inputs are different.

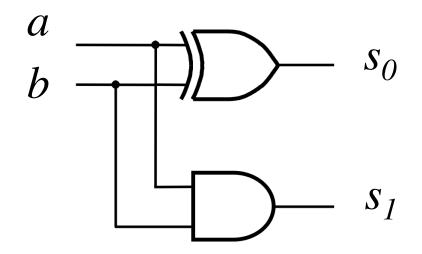

| a | b | <i>s</i> <sub>1</sub> | $s_0$ |

|---|---|-----------------------|-------|

| 0 | 0 | 0                     | 0     |

| 0 | 1 | 0                     | 1     |

| 1 | 0 | 0                     | 1     |

| 1 | 1 | 1                     | 0     |

| a          | 0   | 0   | 1   | 1   |

|------------|-----|-----|-----|-----|

| + <i>b</i> | + 0 | + 1 | + 0 | + 1 |

| $s_1 s_0$  | 0 0 | 0 1 | 0 1 | 1 0 |

| a | b | <i>s</i> <sub>1</sub> | <i>s</i> <sub>0</sub> |

|---|---|-----------------------|-----------------------|

| 0 | 0 | 0                     | 0                     |

| 0 | 1 | 0                     | 1                     |

| 1 | 0 | 0                     | 1                     |

| 1 | 1 | 1                     | 0                     |

| a          | 0   | 0   | 1   | 1   |

|------------|-----|-----|-----|-----|

| + <i>b</i> | + 0 | + 1 | + 0 | + 1 |

| $s_1 s_0$  | 0 0 | 0 1 | 0 1 | 1 0 |

| a | b | <i>s</i> <sub>1</sub> | <i>s</i> <sub>0</sub> |  |

|---|---|-----------------------|-----------------------|--|

| 0 | 0 | 0                     | 0                     |  |

| 0 | 1 | 0                     | 1                     |  |

| 1 | 0 | 0                     | 1                     |  |

| 1 | 1 | 1                     | 0                     |  |

$$a$$

$+b$

$s_1 s_0$

| a b | s <sub>1</sub> s <sub>0</sub> |

|-----|-------------------------------|

| 0 0 | 0 0                           |

| 0 1 | 0 1                           |

| 1 0 | 0 1                           |

| 1 1 | 1 0                           |

|     | 1                             |

| a          | 0  | 0   | 1   | 1   |

|------------|----|-----|-----|-----|

| + <i>b</i> | +0 | + 1 | + 0 | + 1 |

| $s_1 s_0$  |    |     | 0 1 |     |

| a | b | <i>s</i> <sub>1</sub> | $s_0$ |

|---|---|-----------------------|-------|

| 0 | 0 | 0                     | 0     |

| 0 | 1 | 0                     | 1     |

| 1 | 0 | 0                     | 1     |

| 1 | 1 | 1                     | 0     |

| a          | 0   | 0   | 1   | 1   |

|------------|-----|-----|-----|-----|

| + <i>b</i> | + 0 | + 1 | + 0 | + 1 |

| $s_1 s_0$  |     |     | 0 1 |     |

| a | b |  | <i>s</i> <sub>1</sub> | $s_0$ |

|---|---|--|-----------------------|-------|

| 0 | 0 |  | 0                     | 0     |

| 0 | 1 |  | 0                     | 1     |

| 1 | 0 |  | 0                     | 1     |

| 1 | 1 |  | 1                     | 0     |

$$a$$

$+b$

$s_1 s_0$

| a b | s <sub>1</sub> s <sub>0</sub> |

|-----|-------------------------------|

| 0 0 | 0 0                           |

| 0 1 | 0 1                           |

| 1 0 | 0 1                           |

| 1 1 | 1 0                           |

|     | 1                             |

$$a + b$$

$s_1 s_0$

| a | b | S | 1 | $s_0$ |

|---|---|---|---|-------|

| 0 | 0 | 0 | ) | 0     |

| 0 | 1 | 0 | ) | 1     |

| 1 | 0 | 0 | ) | 1     |

| 1 | 1 | 1 |   | 0     |

$$a$$

$+b$

$s_1s_0$

$0$

| a | b | <i>s</i> <sub>1</sub> | $s_0$ |

|---|---|-----------------------|-------|

| 0 | 0 | 0                     | 0     |

| 0 | 1 | 0                     | 1     |

| 1 | 0 | 0                     | 1     |

| 1 | 1 | 1                     | 0     |

$$a$$

$+b$

$s_1 s_0$

| a b | s <sub>1</sub> s <sub>0</sub> |

|-----|-------------------------------|

| 0 0 | 0 0                           |

| 0 1 | 0 1                           |

| 1 0 | 0 1                           |

| 1 1 | 1 0                           |

|     | 1                             |

$$a + b$$

$s_1 s_0$

| а | b | S | 1 | $s_0$ |

|---|---|---|---|-------|

| 0 | 0 | ( | ) | 0     |

| 0 | 1 | ( | ) | 1     |

| 1 | 0 | ( | ) | 1     |

| 1 | 1 | 1 | l | 0     |

$$a + b$$

$s_1 s_0$

| + | 0 | 4 | + 1 |

|---|---|---|-----|

| 0 | 1 | 1 | 0   |

|   |   |   |     |

| $s_1$ | $s_0$ |                   |

|-------|-------|-------------------|

| 0     | 0     |                   |

| 0     | 1     |                   |

| 0     | 1     |                   |

| 1     | 0     |                   |

|       | 0     | 0 0<br>0 1<br>0 1 |

$$a$$

$+b$

$s_1 s_0$

| a b | s <sub>1</sub> s <sub>0</sub> |

|-----|-------------------------------|

| 0 0 | 0 0                           |

| 0 1 | 0 1                           |

| 1 0 | 0 1                           |

| 1 1 | 1 0                           |

|     | 1                             |

| a | b | $s_1$ | $s_0$ |

|---|---|-------|-------|

| 0 | 0 | 0     | 0     |

| 0 | 1 | 0     | 1     |

| 1 | 0 | 0     | 1     |

| 1 | 1 | 1     | 0     |

|   |   | ?     |       |

|---|---|-------|-------|

| a | b | $s_1$ | $s_0$ |

| 0 | 0 | 0     | 0     |

| 0 | 1 | 0     | 1     |

| 1 | 0 | 0     | 1     |

| 1 | 1 | 1     | 0     |

|   |   |       |       |

|   | AND |  |       |       |

|---|-----|--|-------|-------|

| a | b   |  | $s_1$ | $s_0$ |

| 0 | 0   |  | 0     | 0     |

| 0 | 1   |  | 0     | 1     |

| 1 | 0   |  | 0     | 1     |

| 1 | 1   |  | 1     | 0     |

|   |     |  |       |       |

| a | b | $s_1$ | $s_0$ |

|---|---|-------|-------|

| 0 | 0 | 0     | 0     |

| 0 | 1 | 0     | 1     |

| 1 | 0 | 0     | 1     |

| 1 | 1 | 1     | 0     |

|   |   |                       | ?     |  |

|---|---|-----------------------|-------|--|

| a | b | <i>s</i> <sub>1</sub> | $s_0$ |  |

| 0 | 0 | 0                     | 0     |  |

| 0 | 1 | 0                     | 1     |  |

| 1 | 0 | 0                     | 1     |  |

| 1 | 1 | 1                     | 0     |  |

|   |   |                       |       |  |

|   |   | XOR                   |       |  |

|---|---|-----------------------|-------|--|

| a | b | <i>s</i> <sub>1</sub> | $s_0$ |  |

| 0 | 0 | 0                     | 0     |  |

| 0 | 1 | 0                     | 1     |  |

| 1 | 0 | 0                     | 1     |  |

| 1 | 1 | 1                     | 0     |  |

|   |   |                       |       |  |

| a | b | $s_1$ | $s_0$ |

|---|---|-------|-------|

| 0 | 0 | 0     | 0     |

| 0 | 1 | 0     | 1     |

| 1 | 0 | 0     | 1     |

| 1 | 1 | 1     | 0     |

| a | b      | <i>s</i> <sub>1</sub> | $s_0$ |

|---|--------|-----------------------|-------|

| 0 | 0      | 0                     | 0     |

| 0 | 1      | 0                     | 1     |

| 1 | 0      | 0                     | 1     |

| 1 | 1      | 1                     | 0     |

|   | 0<br>1 |                       | •     |

| a | b | <i>s</i> <sub>1</sub> | $s_0$ |

|---|---|-----------------------|-------|

| 0 | 0 | 0                     | 0     |

| 0 | 1 | 0                     | 1     |

| 1 | 0 | 0                     | 1     |

| 1 | 1 | 1                     | 0     |

|   |   |                       |       |

#### The following examples came from this book

[ Platt 2009 ]

### **Questions?**

### THE END