# CprE 281: Digital Logic

### **Instructor: Alexander Stoytchev**

http://www.ece.iastate.edu/~alexs/classes/

# Latches

CprE 281: Digital Logic Iowa State University, Ames, IA Copyright © Alexander Stoytchev

# **Administrative Stuff**

• HW 7 is due on Monday (Oct 18) @ 4pm

• Midterm grades submitted to the registrar's office

# **Administrative Stuff**

- Midterm 2 is in two weeks

- Sample exams are posted on the class web page

# **Administrative Stuff**

- Midterm Exam #2

- When: Friday October 29 @ 4:20pm.

- Where: This room

- What: Chapters 1, 2, 3, 4 and 5

- The exam will be closed book but open notes (you can bring up to 3 pages of handwritten notes).

# **Chapter 5**

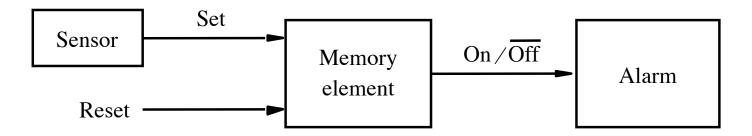

# **Control of an alarm system**

## **Motivation**

So far, our circuits have been converting inputs to outputs without storing any data.

To do more advanced things (e.g., to build computers) we need components that can store data.

Can we make a component that "remembers"

using the components that we know already?

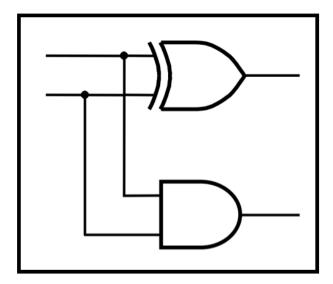

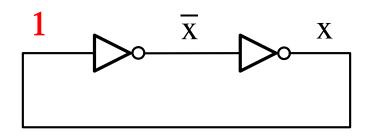

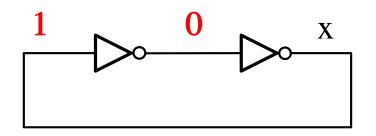

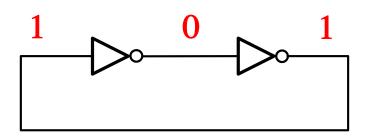

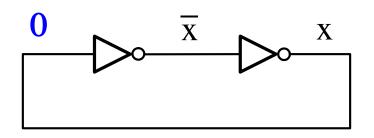

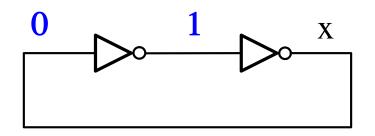

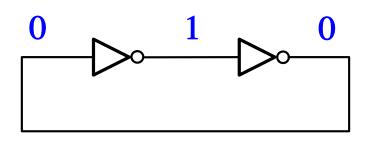

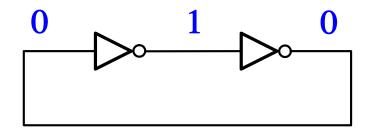

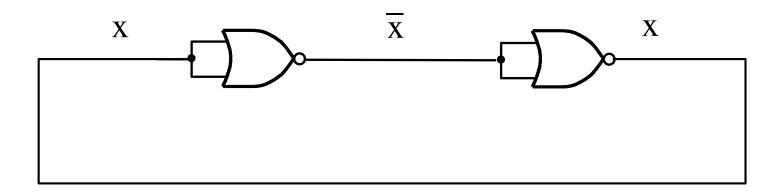

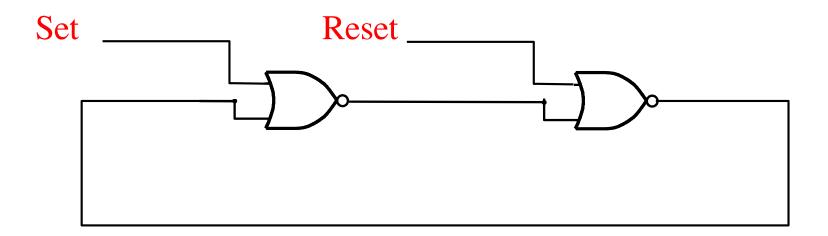

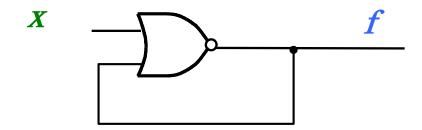

## A simple memory element

[Figure 5.2 from the textbook]

The circuit will stay in this state indefinitely.

The circuit will stay in this state indefinitely.

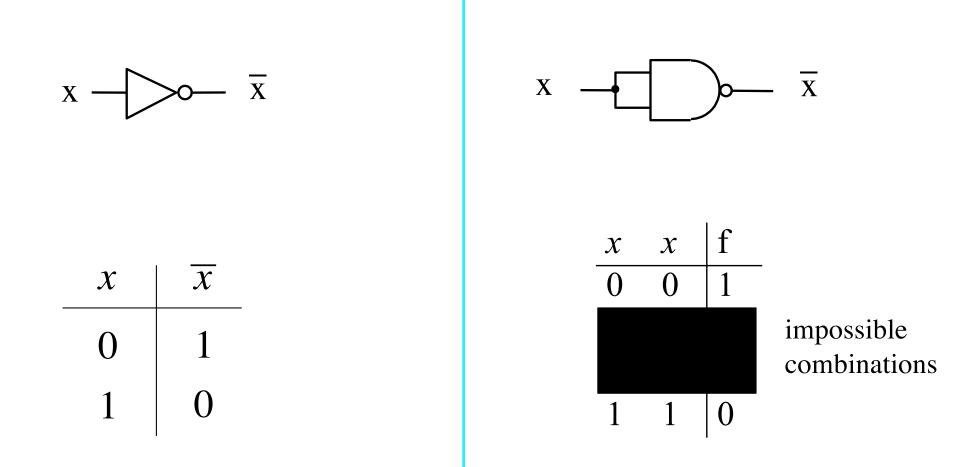

## A Strange Loop

### This circuit can be in two possible states

## This circuit can be in two possible states

#### used to store a 1

used to store a 0

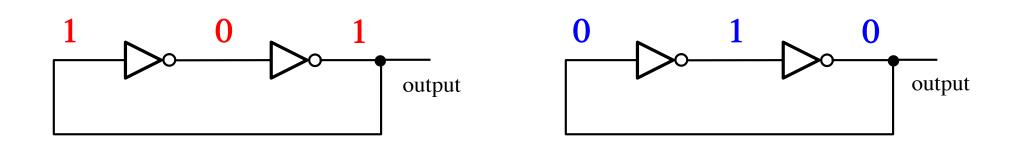

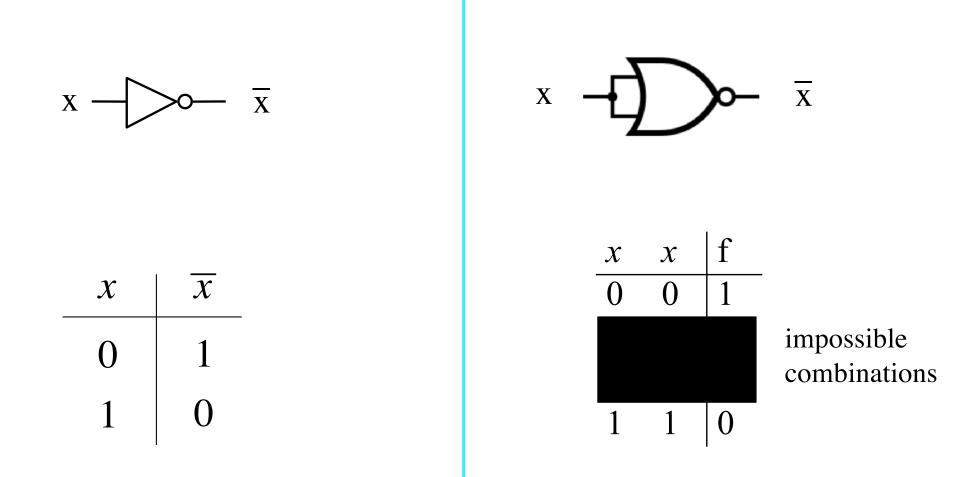

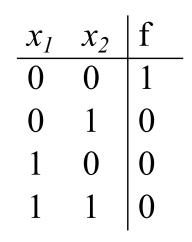

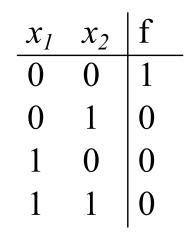

# Building a NOT gate with a NAND gate

Thus, the two truth tables are equal!

# Building a NOT gate with a NOR gate

Thus, the two truth tables are equal!

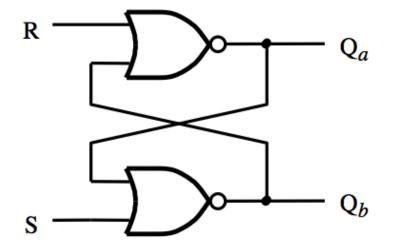

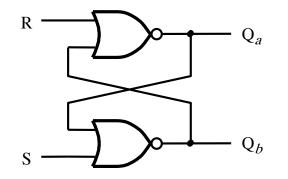

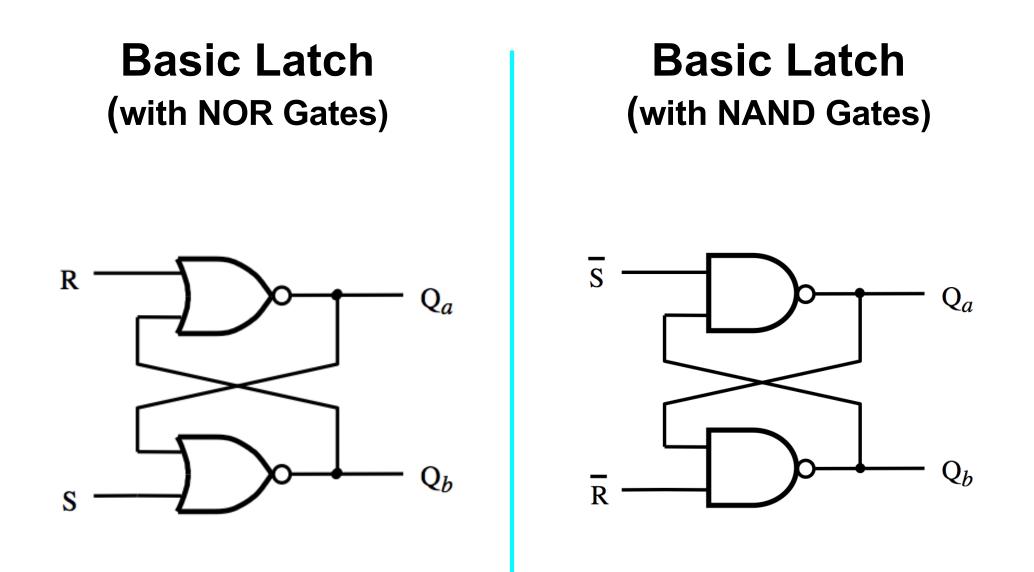

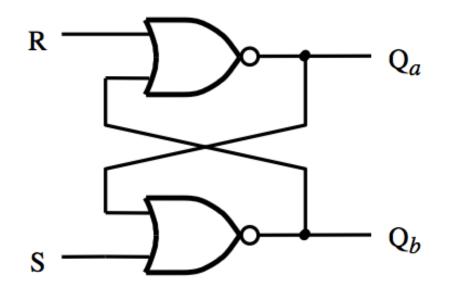

# **Basic Latch**

## What is a latch?

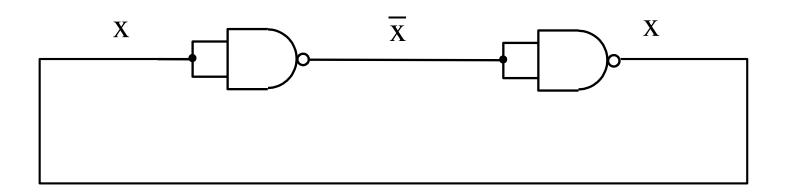

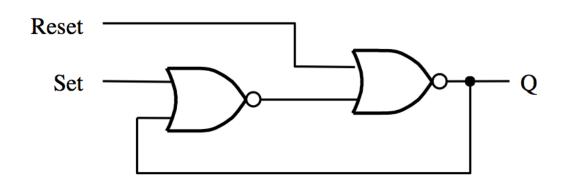

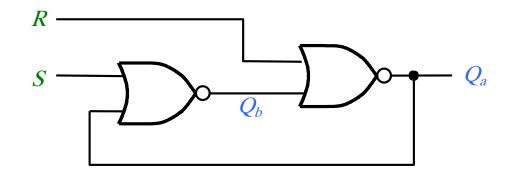

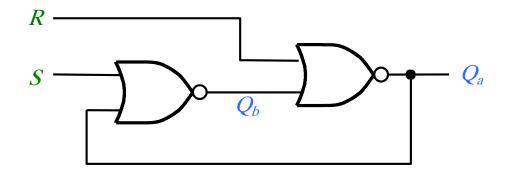

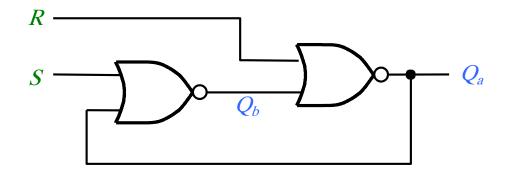

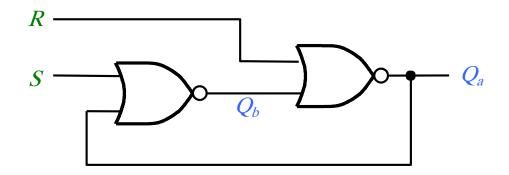

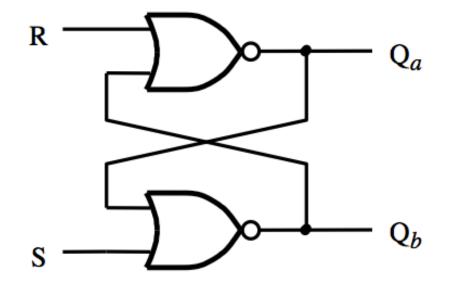

# A memory element with NOR gates

[Figure 5.3 from the textbook]

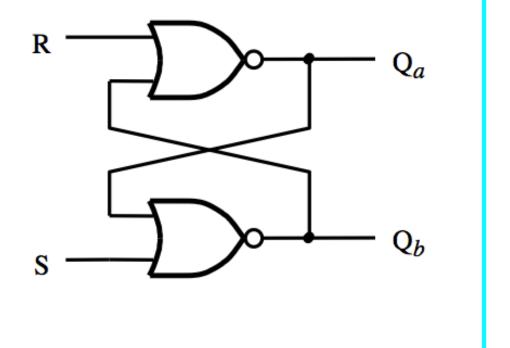

## **Two Different Ways to Draw the Same Circuit**

[Figure 5.3 & 5.4 from the textbook]

## **Two Different Ways to Draw the Same Circuit**

[Figure 5.3 & 5.4 from the textbook]

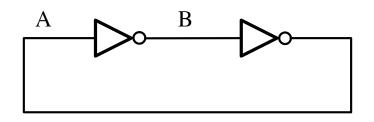

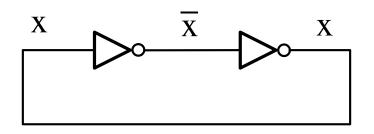

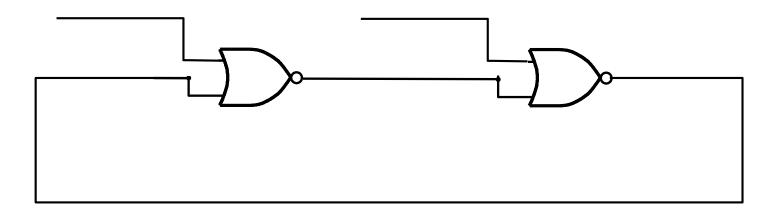

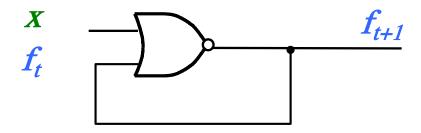

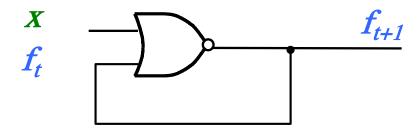

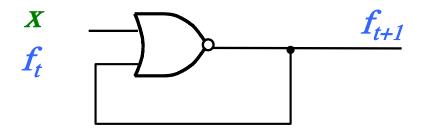

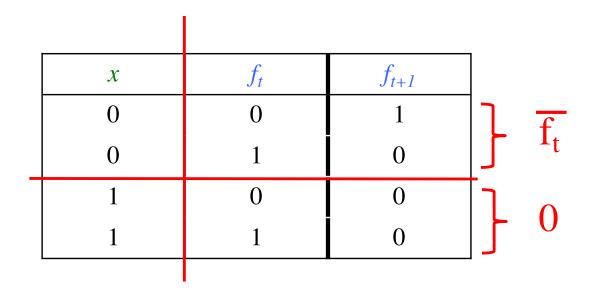

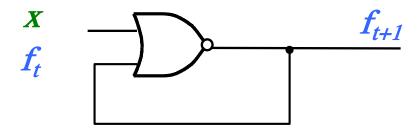

# Before We Analyze the Basic Latch Let's Look at a Two Simpler Examples with Feedback

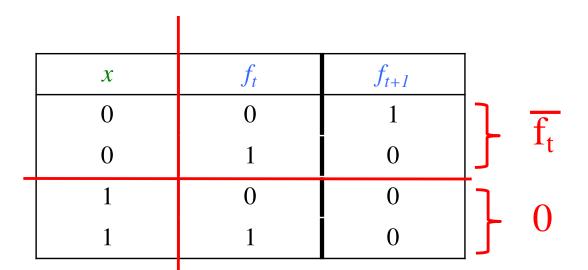

| x | $f_t$ | $f_{t+1}$ |

|---|-------|-----------|

| 0 | 0     |           |

| 0 | 1     |           |

| 1 | 0     |           |

| 1 | 1     |           |

| x | $f_t$ | $f_{t+1}$ |

|---|-------|-----------|

| 0 | 0     | 1         |

| 0 | 1     | 0         |

| 1 | 0     | 0         |

| 1 | 1     | 0         |

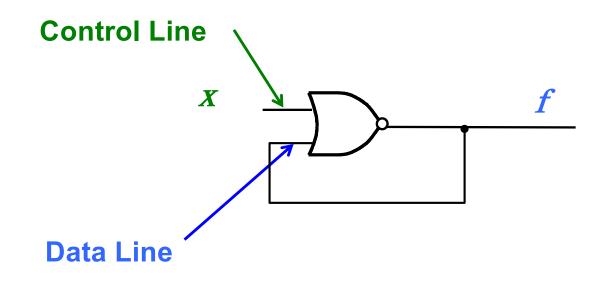

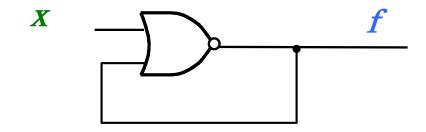

If x = 0, then *f* is negated. If x = 1, then *f* is driven to 0.

### **Key Observation**

If a NOR's control line is 0, then that NOR just *negates* its data line. If the control line is 1, then the NOR's output is *driven* to 0, ignoring its data line.

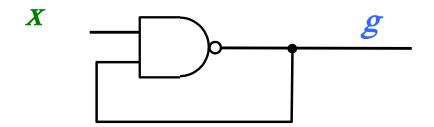

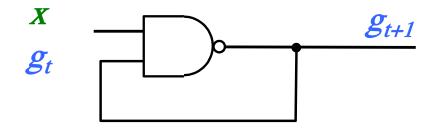

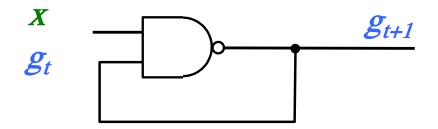

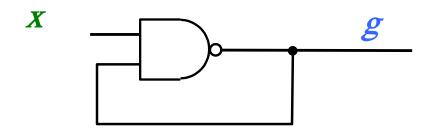

| x | $g_t$ | $g_{t+1}$ |

|---|-------|-----------|

| 0 | 0     |           |

| 0 | 1     |           |

| 1 | 0     |           |

| 1 | 1     |           |

| x | $g_t$ | $g_{t+1}$ |

|---|-------|-----------|

| 0 | 0     | 1         |

| 0 | 1     | 1         |

| 1 | 0     | 1         |

| 1 | 1     | 0         |

If x = 0, then g is driven to one. If x = 1, then g is negated.

### **Key Observation**

If a NAND's control line is 1, then that NAND just *negates* its data line. If the control line is 0, then the NAND's output is *driven* to 1, ignoring its data line.

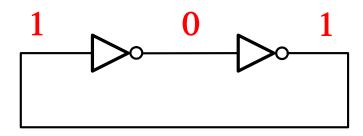

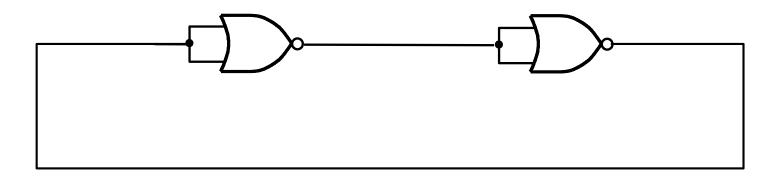

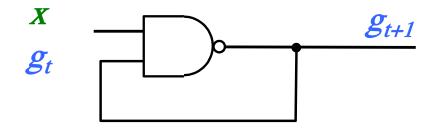

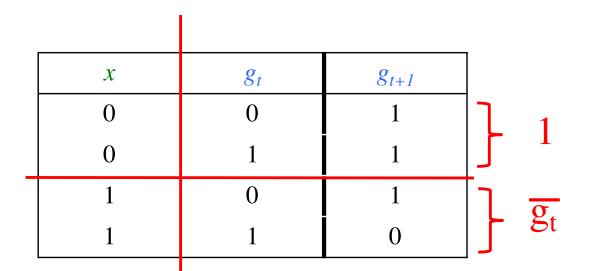

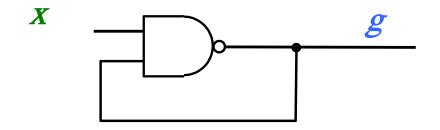

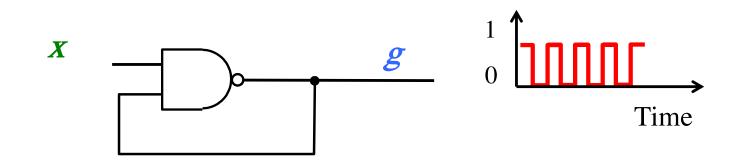

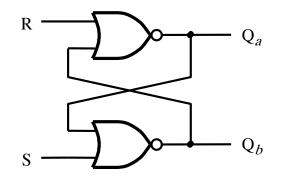

### **Output Oscillations**

What would happen to **g** if we keep **x**=1 for a long time?

### **Output Oscillations**

What would happen to **g** if we keep **x=1** for a long time?

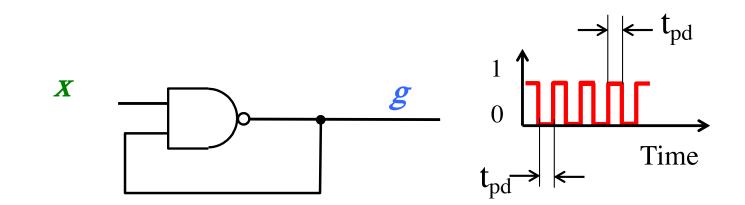

### **Output Oscillations**

What would happen to g if we keep x=1 for a long time?

$t_{pd}$  is the propagation delay through the NAND gate, which is small, but not zero.

# **Back to the Basic Latch**

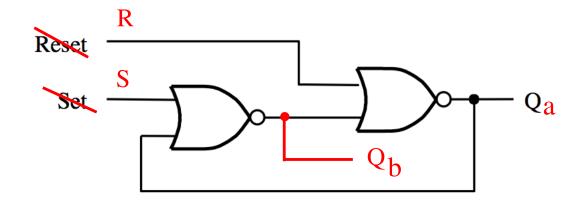

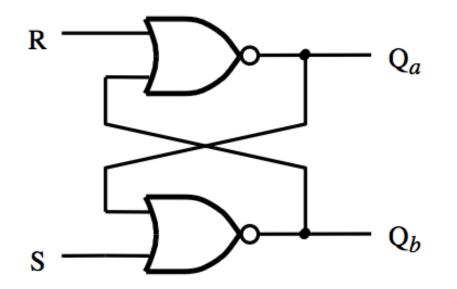

# **The Basic Latch**

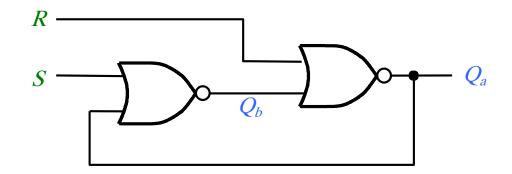

[Figure 5.3 from the textbook]

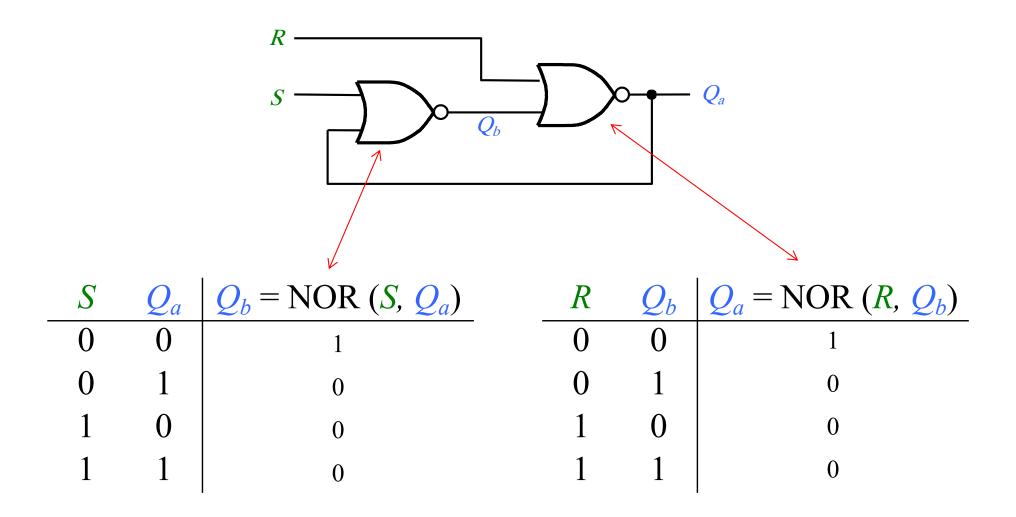

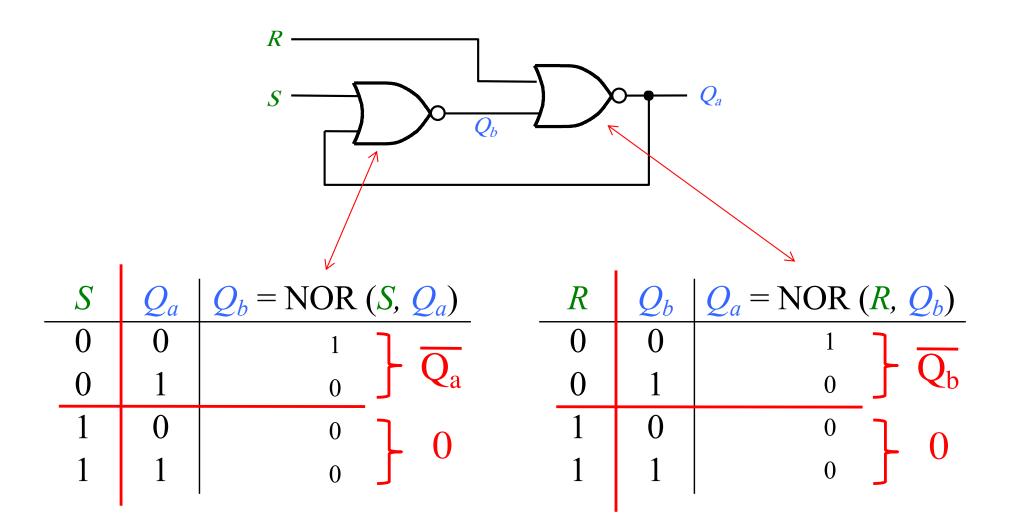

# **The Basic Latch**

[Figure 5.3 from the textbook]

| S | $Q_a$ | $Q_b = \text{NOR}(S, Q_a)$ | R | $Q_b$ | $Q_a = \text{NOR}(R, Q_b)$ |

|---|-------|----------------------------|---|-------|----------------------------|

| 0 | 0     |                            | 0 | 0     |                            |

| 0 | 1     |                            | 0 | 1     |                            |

| 1 | 0     |                            | 1 | 0     |                            |

| 1 | 1     |                            | 1 | 1     |                            |

| S | R | $Q_{t+1}$ |

|---|---|-----------|

| 0 | 0 |           |

| 0 | 1 |           |

| 1 | 0 |           |

| 1 | 1 |           |

| S | R | $Q_{t+1}$ |

|---|---|-----------|

| 0 | 0 | $Q_t$     |

| 0 | 1 | 0         |

| 1 | 0 | 1         |

| 1 | 1 | 0         |

| S | R | $Q_a(t+1)$ | $Q_b(t+1)$ |

|---|---|------------|------------|

| 0 | 0 |            |            |

| 0 | 1 |            |            |

| 1 | 0 |            |            |

| 1 | 1 |            |            |

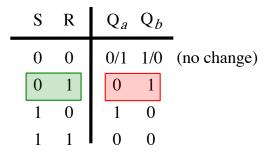

| S | R | $Q_a(t+1)$ | $Q_b(t+1)$ |

|---|---|------------|------------|

| 0 | 0 | $Q_a(t)$   | $Q_b(t)$   |

| 0 | 1 | 0          | 1          |

| 1 | 0 | 1          | 0          |

| 1 | 1 | 0          | 0          |

| S | R | $Q_a(t+1)$ | $Q_b(t+1)$ |  |

|---|---|------------|------------|--|

| 0 | 0 | $Q_a(t)$   | $Q_b(t)$   |  |

| 0 | 1 | 0          | 1          |  |

| 1 | 0 | 1          | 0          |  |

| 1 | 1 | 0          | 0          |  |

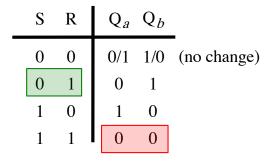

Latch Reset Set Undesirable

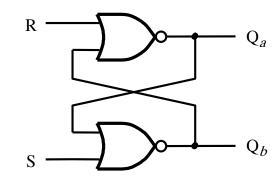

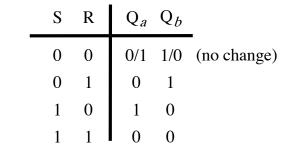

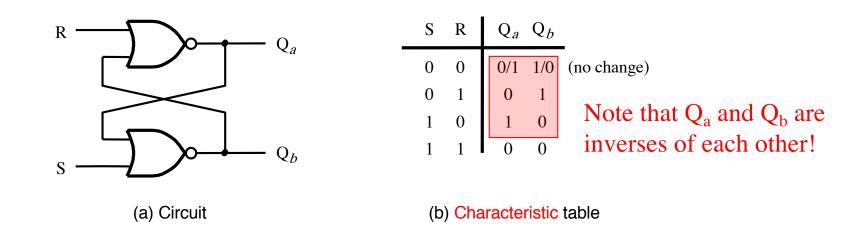

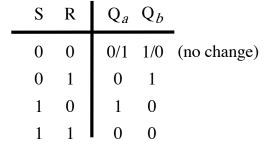

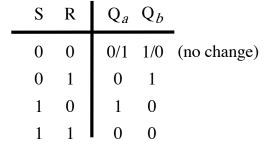

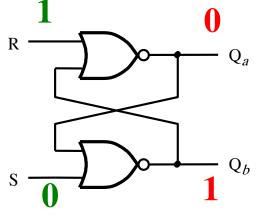

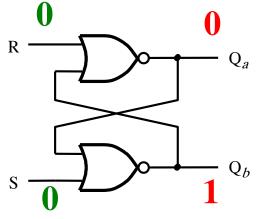

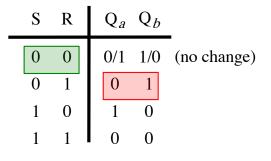

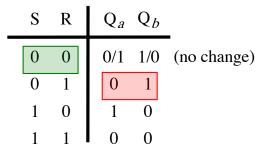

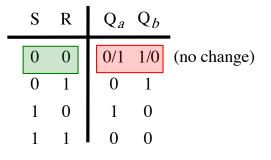

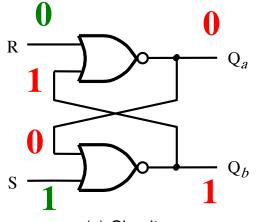

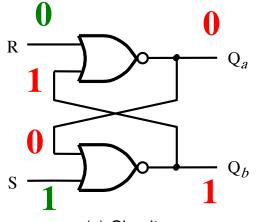

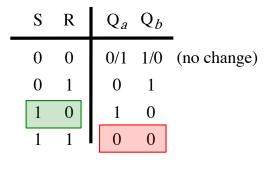

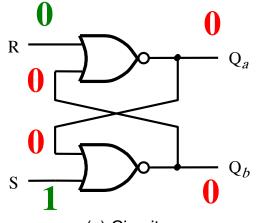

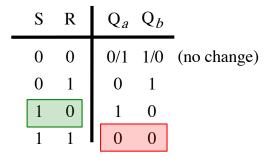

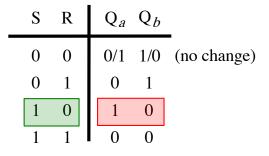

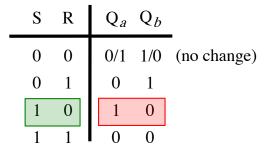

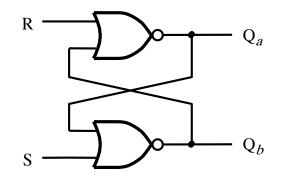

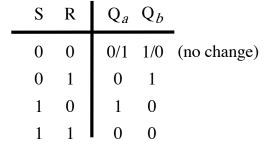

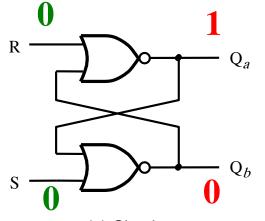

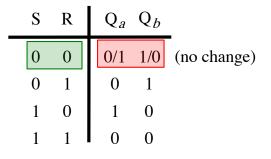

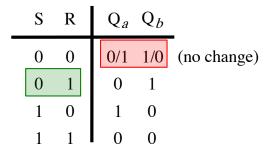

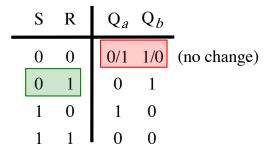

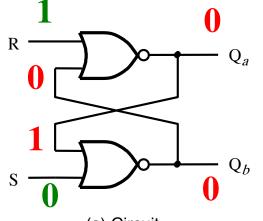

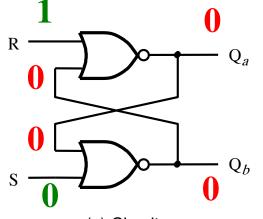

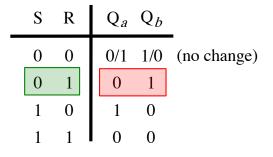

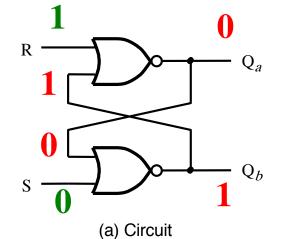

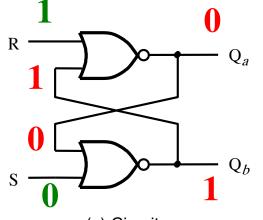

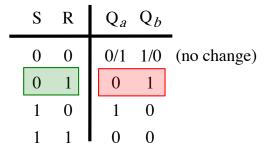

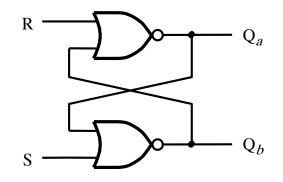

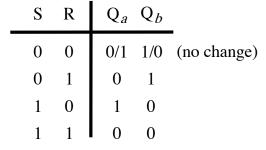

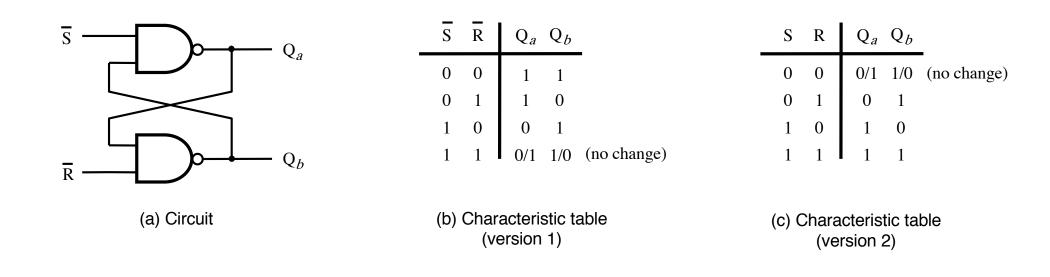

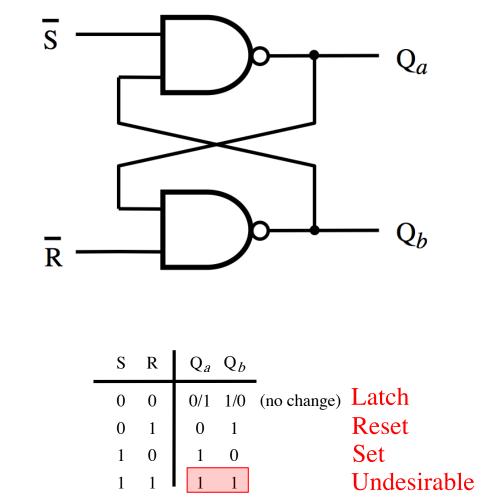

#### **Circuit and Characteristic Table**

(a) Circuit

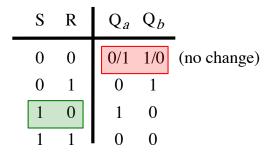

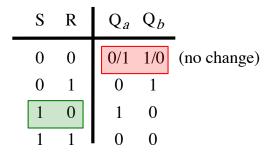

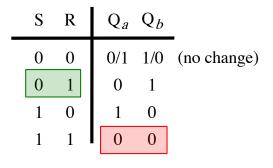

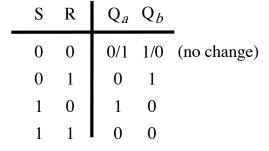

| S | R | Qa  | $Q_b$ | _           |

|---|---|-----|-------|-------------|

| 0 | 0 | 0/1 | 1/0   | (no change) |

| 0 | 1 | 0   | 1     |             |

| 1 | 0 | 1   | 0     |             |

| 1 | 1 | 0   | 0     |             |

|   |   |     |       |             |

(b) Characteristic table

[Figure 5.4a,b from the textbook]

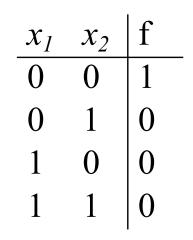

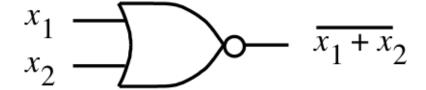

NOR Gate Truth table

NOR Gate

#### **Circuit and Characteristic Table**

(a) Circuit

$x_1 + x_2$

(b) Characteristic table

A truth table should take the state into account. A characteristic table takes only the inputs into account.

NOR Gate

$x_1$

$x_2$

[Figure 5.4a,b from the textbook]

NOR Gate Truth table

#### **Circuit and Characteristic Table**

$\overline{x_1 + x_2}$

NOR Gate

$x_1$

$x_2$

[Figure 5.4a,b from the textbook]

NOR Gate Truth table

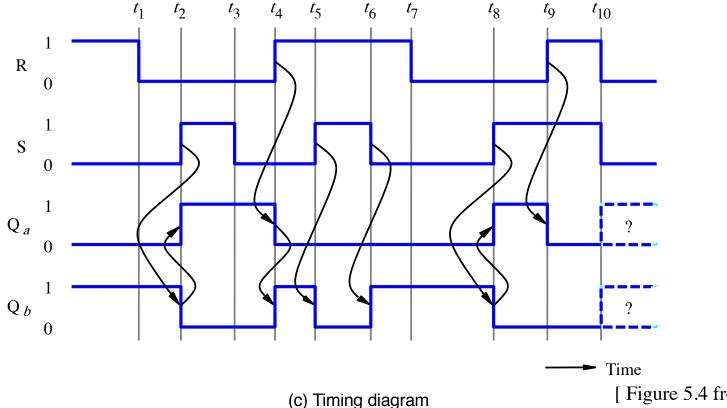

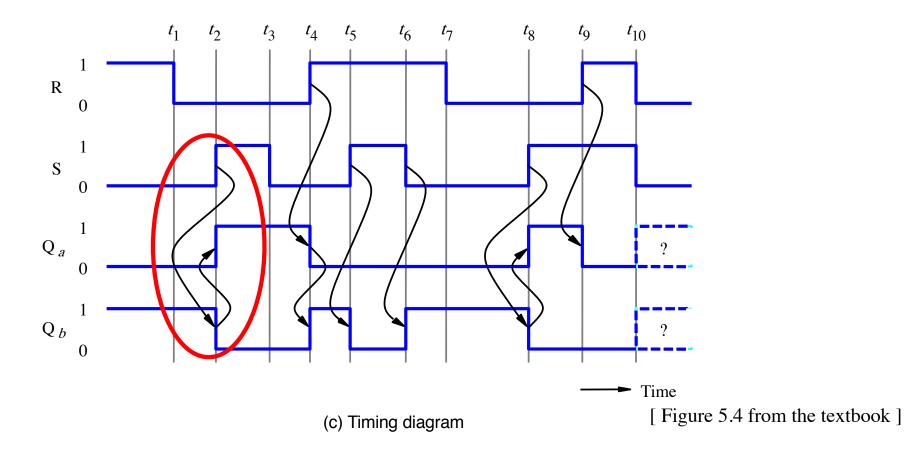

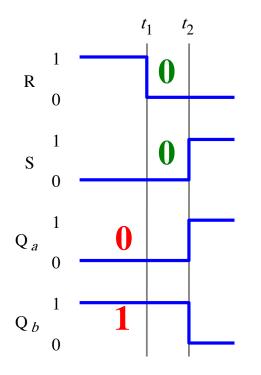

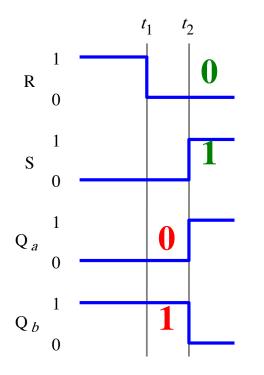

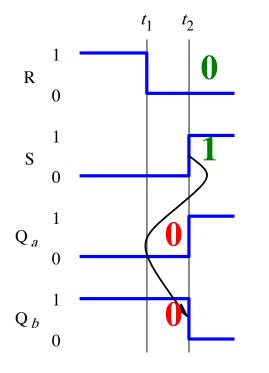

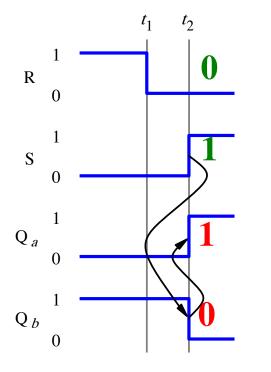

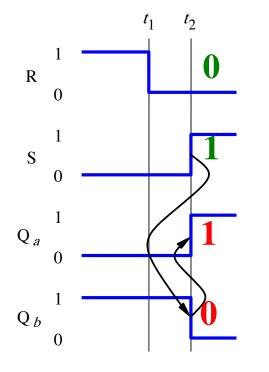

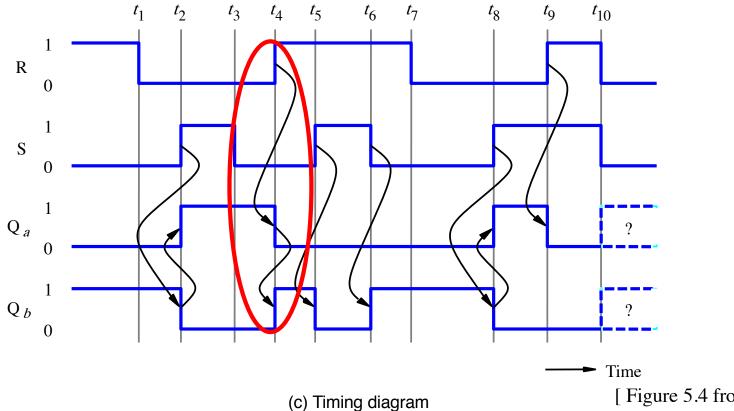

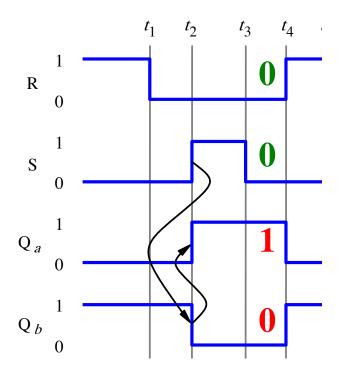

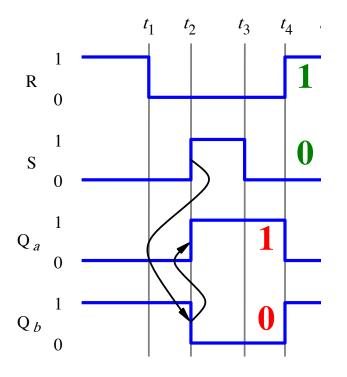

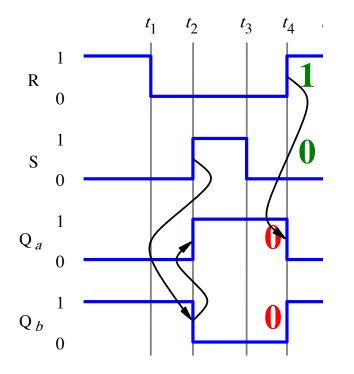

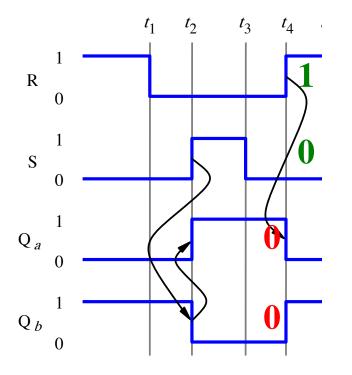

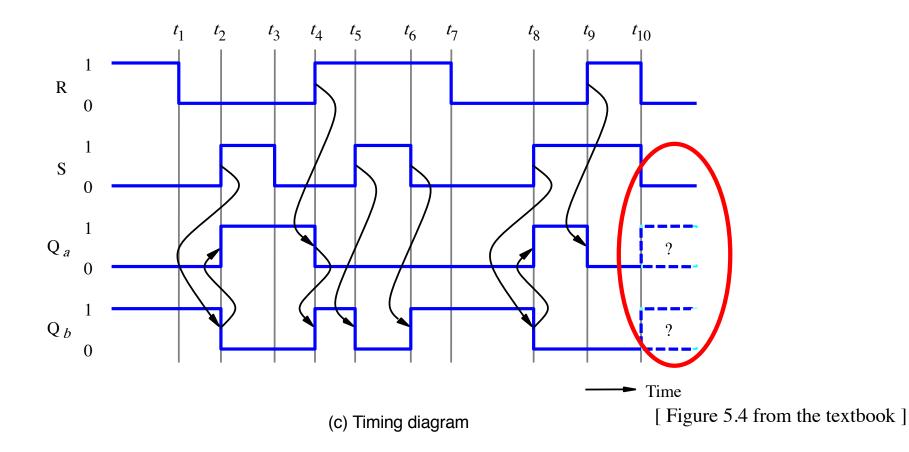

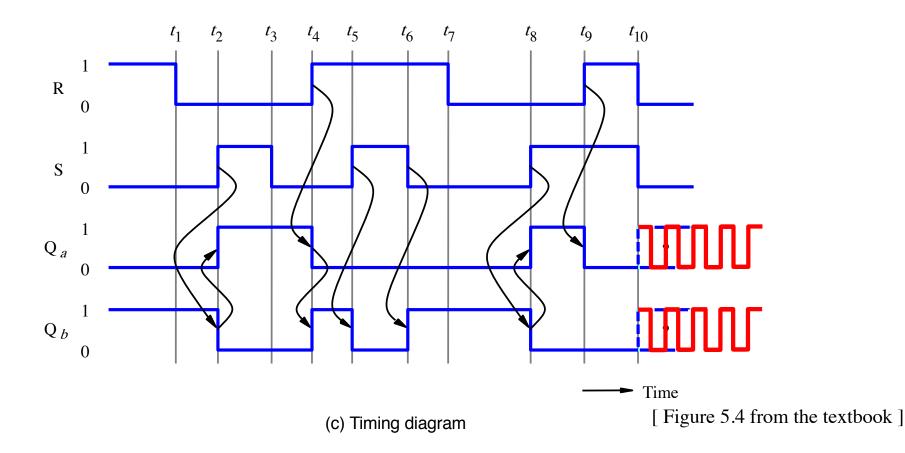

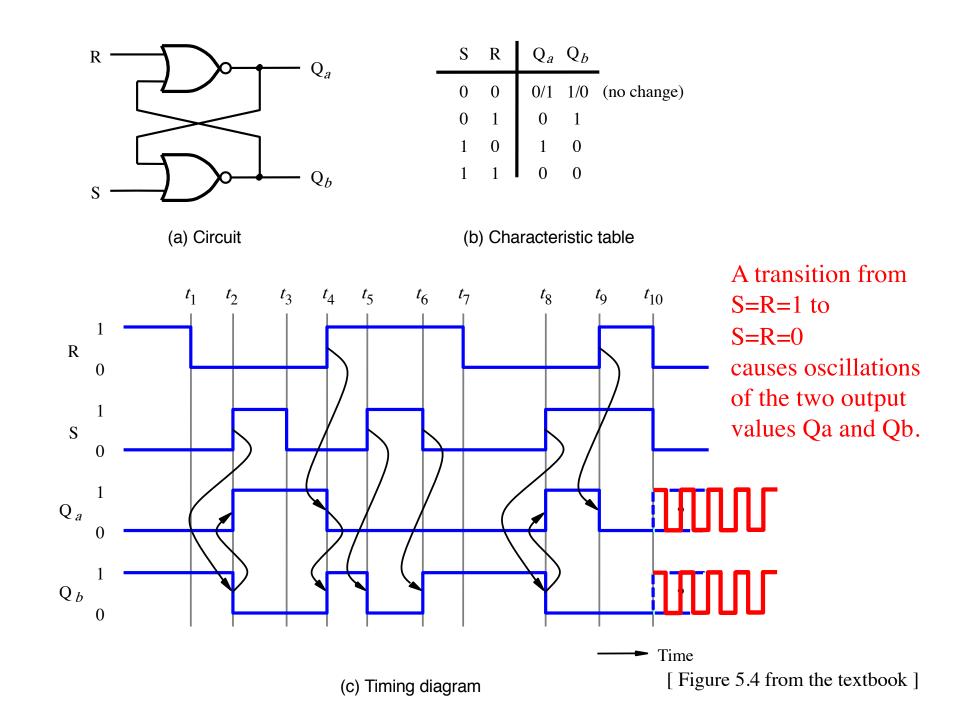

# **Oscillations and Undesirable States**

- When S=1 and R=1 both outputs of the latch are equal to 0, i.e., Q<sub>a</sub>=0 and Q<sub>b</sub>=0.

- Thus, the two outputs are no longer complements of each other.

- This is undesirable as many of the circuits that we will build later with these latches rely on the assumption that the two outputs are always complements of each other.

- (This is obviously not the case for the basic latch, but we will patch it later to eliminate this problem).

# **Oscillations and Undesirable States**

- An even bigger problem occurs when we transition from S=R=1 to S=R=0.

- When S=R=1 we have Q<sub>a</sub>=Q<sub>b</sub>=0. After the transition to S=R=0, however, we get Q<sub>a</sub>=Q<sub>b</sub>=1, which would immediately cause Q<sub>a</sub>=Q<sub>b</sub>=0, and so on.

- If the gate delays and the wire lengths are identical, then this oscillation will continue forever.

- In practice, the oscillation dies down and the output settles into either Q<sub>a</sub>=1 and Q<sub>b</sub>=0 or Q<sub>a</sub>=0 and Q<sub>b</sub>=1.

- The problem is that we can't predict which one of these two it will settle into.

(b) Characteristic table

[Figure 5.4 from the textbook]

| S | R | Qa  | $Q_b$ | _           |

|---|---|-----|-------|-------------|

| 0 | 0 | 0/1 | 1/0   | (no change) |

| 0 | 1 | 0   | 1     |             |

| 1 | 0 | 1   | 0     |             |

| 1 | 1 | 0   | 0     |             |

| S | R | Qa  | $Q_b$ | _           |

|---|---|-----|-------|-------------|

| 0 | 0 | 0/1 | 1/0   | (no change) |

| 0 | 1 | 0   | 1     |             |

| 1 | 0 | 1   | 0     |             |

| 1 | 1 | 0   | 0     |             |

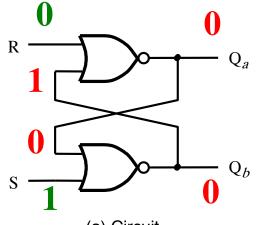

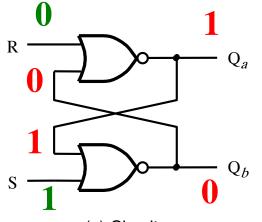

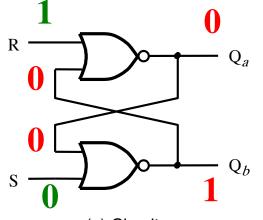

(a) Circuit

(a) Circuit

(a) Circuit

(a) Circuit

(b) Characteristic table

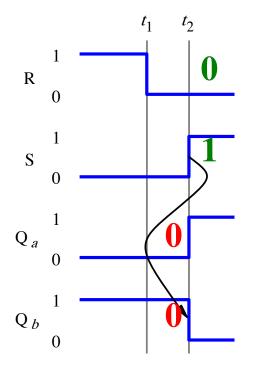

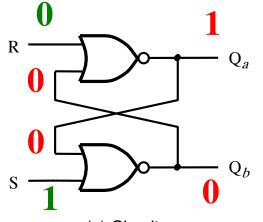

For a brief moment the latch goes through the undesirable state  $Q_a=0$  and  $Q_b=0$ .

(a) Circuit

(b) Characteristic table

But these zeros loop around ...

| S | R | Qa  | $Q_b$ | _           |

|---|---|-----|-------|-------------|

| 0 | 0 | 0/1 | 1/0   | (no change) |

| 0 | 1 | 0   | 1     |             |

| 1 | 0 | 1   | 0     |             |

| 1 | 1 | 0   | 0     |             |

(b) Characteristic table

... and set it to  $Q_a=1$  and  $Q_b=0$ .

(b) Characteristic table

The new values also loop around ...

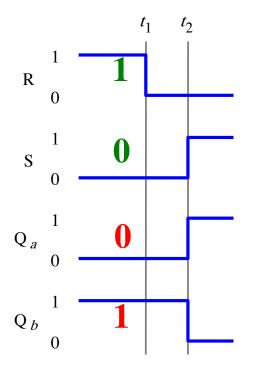

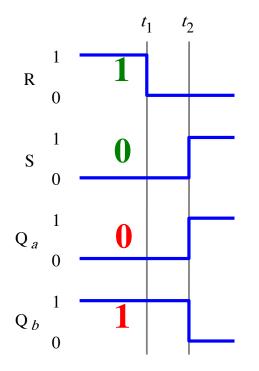

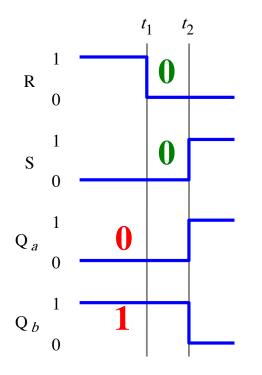

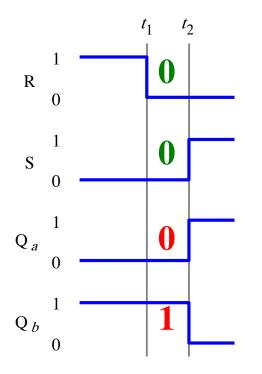

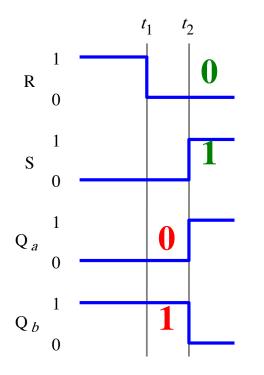

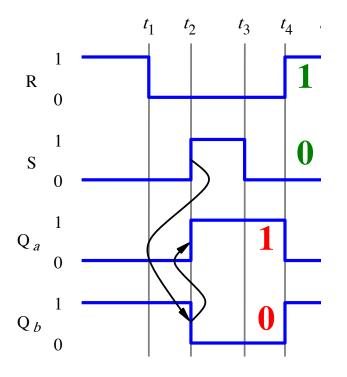

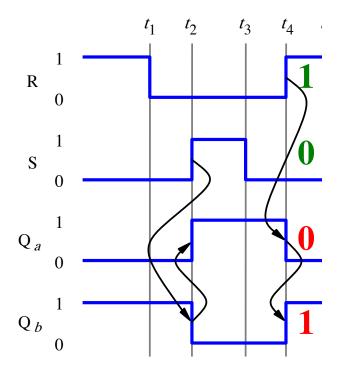

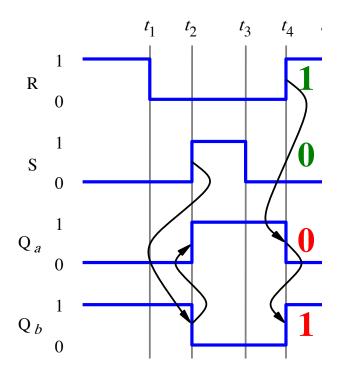

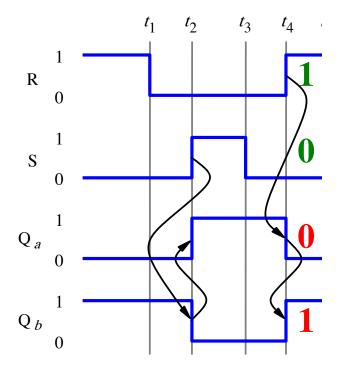

(c) Timing diagram

(a) Circuit

(b) Characteristic table

... but they leave the outputs the same.

(b) Characteristic table

[Figure 5.4 from the textbook]

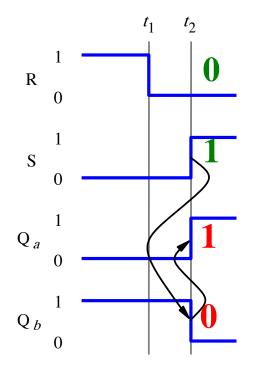

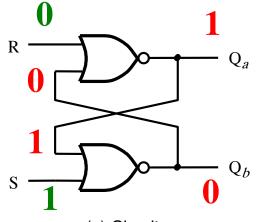

(a) Circuit

(a) Circuit

(a) Circuit

(b) Characteristic table

For a brief moment the latch goes through the undesirable state  $Q_a=0$  and  $Q_b=0$ .

(a) Circuit

(b) Characteristic table

But these zeros loop around ...

(b) Characteristic table

... and set it to  $Q_a=0$  and  $Q_b=1$ .

S

R

(b) Characteristic table

$Q_a Q_b$

The new values also loop around ...

(b) Characteristic table

... but they leave the outputs the same.

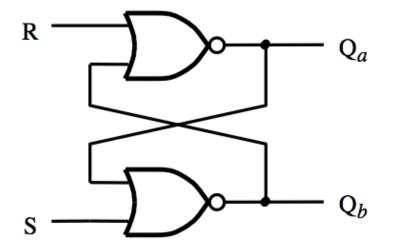

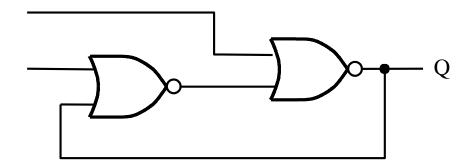

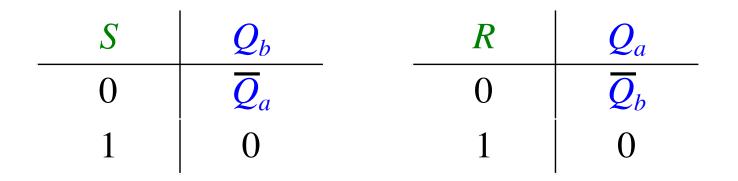

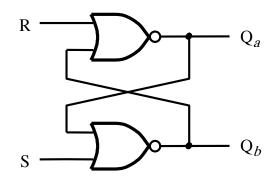

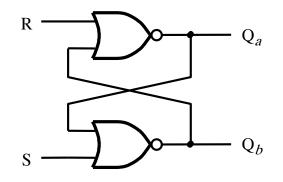

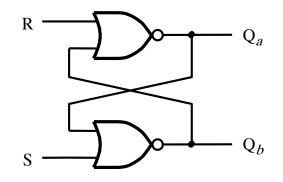

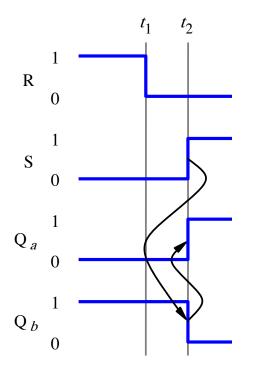

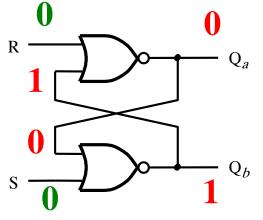

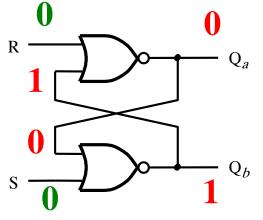

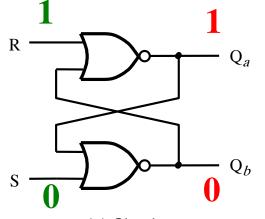

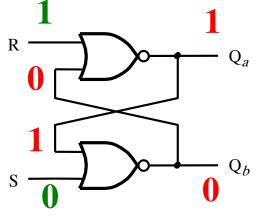

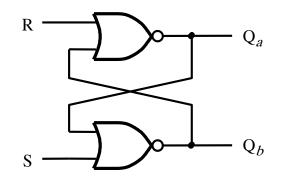

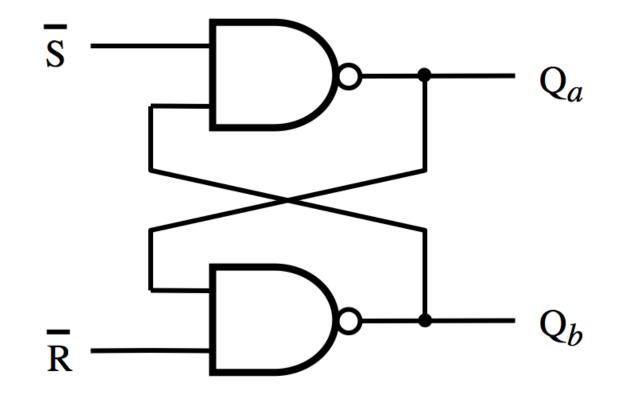

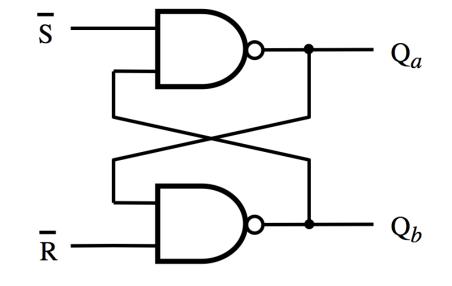

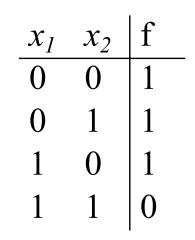

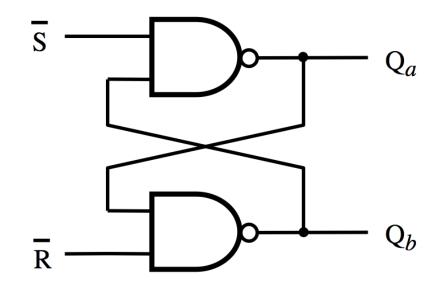

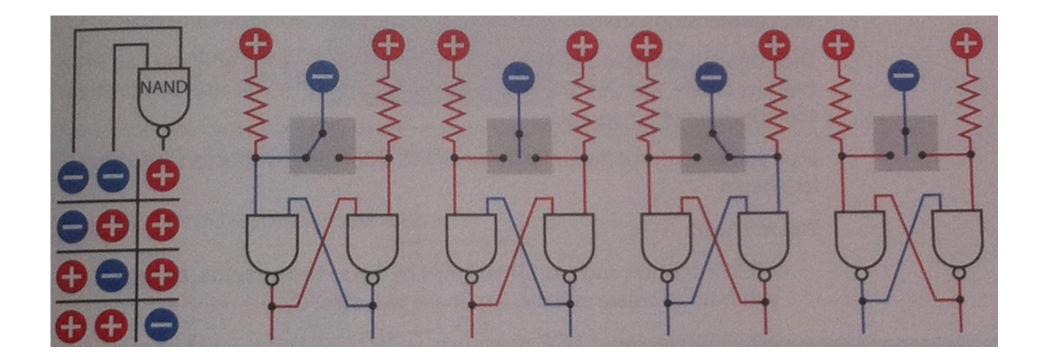

## **Basic Latch with NAND Gates**

### **Circuit for the Basic Latch with NAND Gates**

Notice that in the NAND case the two inputs are swapped and negated.

The labels of the outputs are the same in both cases.

**Basic Latch** (with NAND Gates)

SR Latch

**SR** Latch

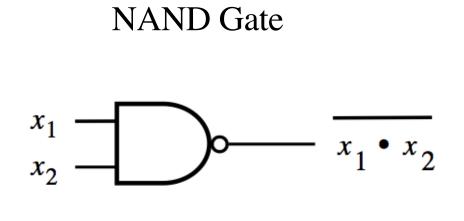

#### **Circuit and Characteristic Table**

NAND Gate Truth table

## Basic Latch (with NOR Gates)

| S | R | Q <sub>a</sub> | $Q_b$ | _           |

|---|---|----------------|-------|-------------|

| 0 | 0 | 0/1            | 1/0   | (no change) |

| 0 | 1 | 0              | 1     |             |

| 1 | 0 | 1              | 0     |             |

| 1 | 1 | 0              | 0     |             |

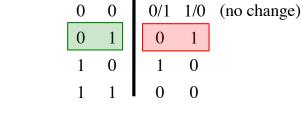

## Basic Latch (with NAND Gates)

| R | Qa                    | $Q_b$ | _           |

|---|-----------------------|-------|-------------|

| 0 | 0/1                   | 1/0   | (no change) |

| 1 | 0                     | 1     |             |

| 0 | 1                     | 0     |             |

| 1 | 1                     | 1     |             |

|   | R<br>0<br>1<br>0<br>1 | Cu    | cu co       |

## Basic Latch (with NOR Gates)

| S | R | Q <sub>a</sub> | $Q_b$ | _           |             |

|---|---|----------------|-------|-------------|-------------|

| 0 | 0 | 0/1            | 1/0   | (no change) | Latch       |

| 0 | 1 | 0              | 1     |             | Reset       |

| 1 | 0 | 1              | 0     |             | Set         |

| 1 | 1 | 0              | 0     |             | Undesirable |

|   |   |                |       |             |             |

## **Basic Latch** (with NAND Gates)

| S | R | Q <sub>a</sub> | $Q_b$ | _           |             |

|---|---|----------------|-------|-------------|-------------|

| 0 | 0 | 0/1            | 1/0   | (no change) | Latch       |

| 0 | 1 | 0              | 1     |             | Reset       |

| 1 | 0 | 1              | 0     |             | Set         |

| 1 | 1 | 1              | 1     |             | Undesirable |

## Basic Latch (with NOR Gates)

0/1 1/0 (no change)

$Q_a Q_b$

0

0

0

0

S R

0

0

1

1

0

1

0

1

## **Basic Latch** (with NAND Gates)

The two characteristic tables are the same (except for the last row, which is the undesirable configuration).

Latch

Reset

Undesirable

Set

## **Oscillations and Undesirable States**

The basic latch with NAND gates also suffers form oscillation problems, similar to the basic latch implemented with NOR gates.

• Try to do this analysis on your own.

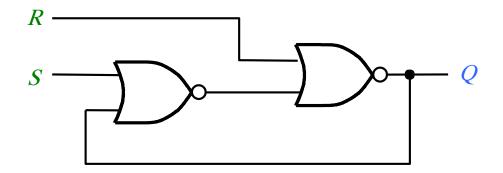

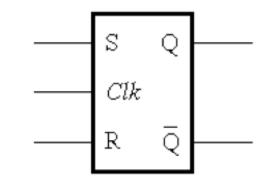

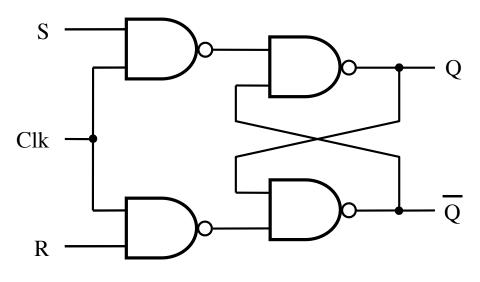

# **Gated SR Latch**

## Motivation

- The basic latch changes its state when the input signals change.

- It is hard to control when these input signals will change and thus it is hard to know when the latch may change its state.

- We want to have something like an Enable input.

- In this case it is called the "Clock" input because it is desirable for the state changes to be synchronized

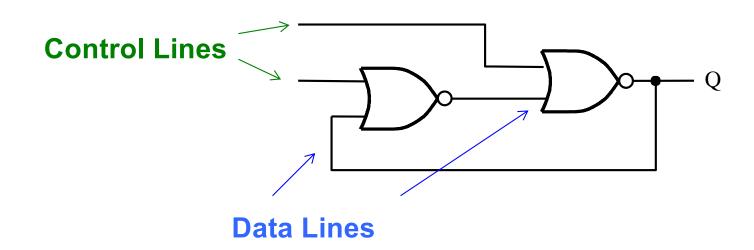

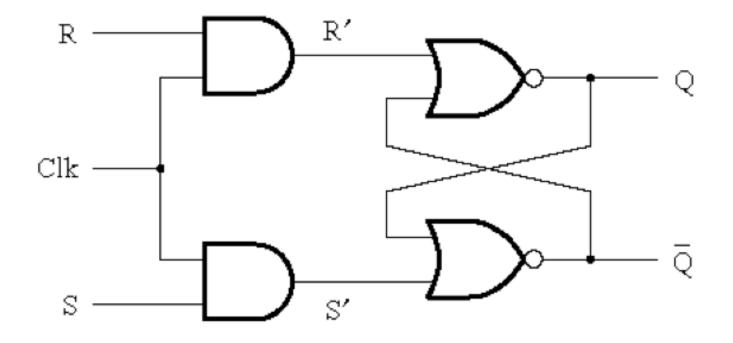

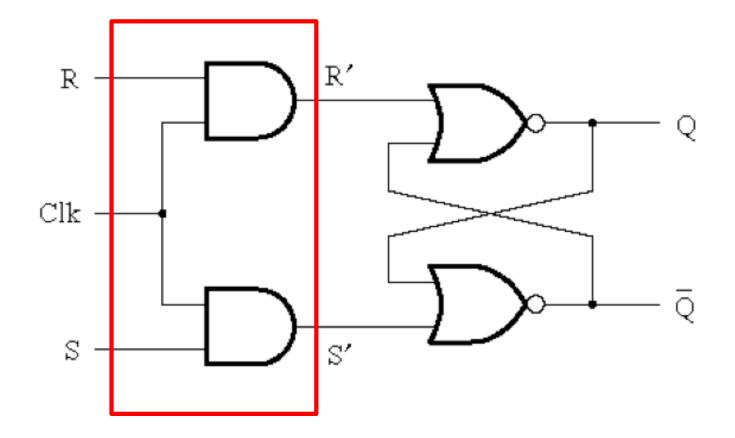

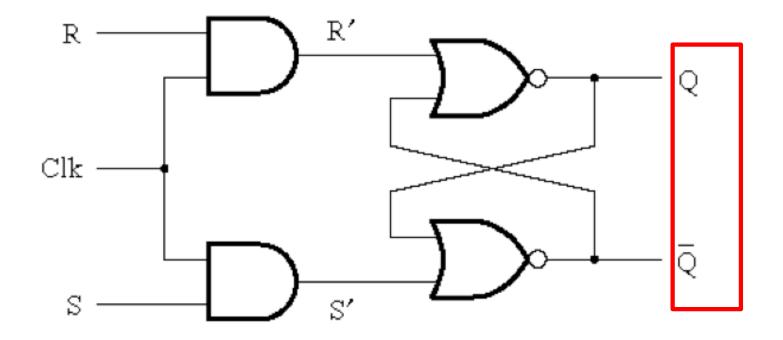

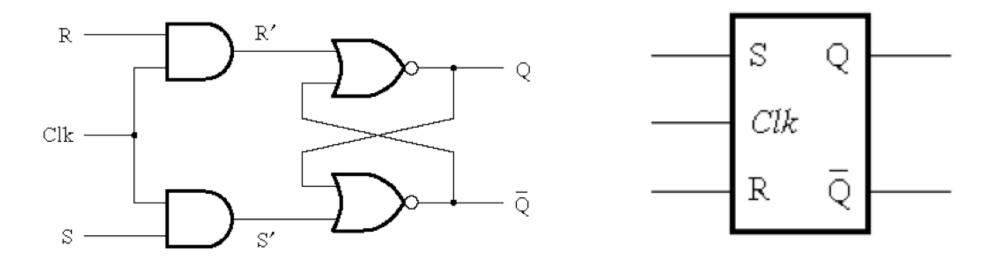

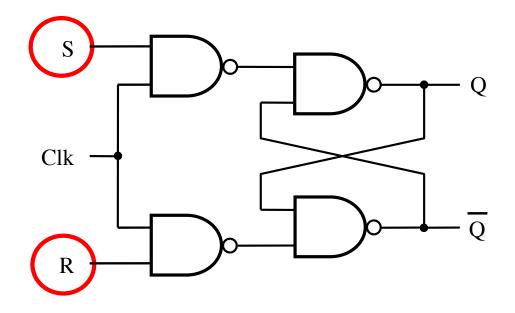

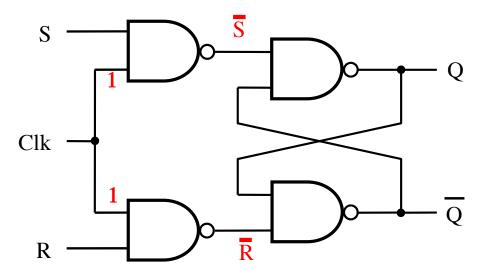

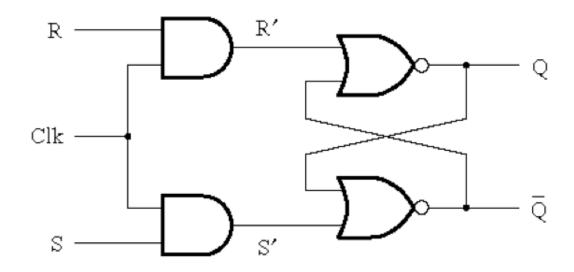

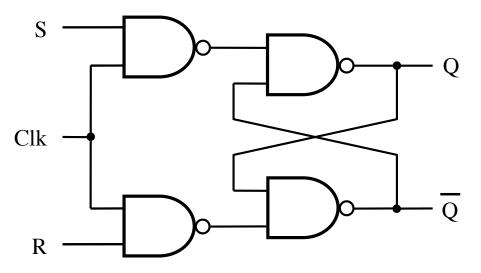

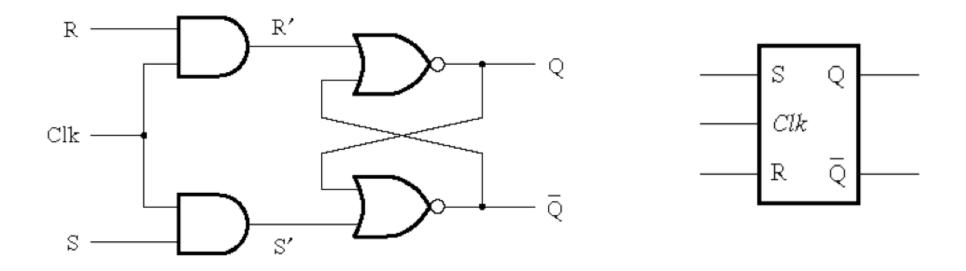

### **Circuit Diagram for the Gated SR Latch**

[Figure 5.5a from the textbook]

### **Circuit Diagram for the Gated SR Latch**

This is the "gate" of the gated latch

### **Circuit Diagram for the Gated SR Latch**

Notice that these are complements of each other

## Circuit Diagram and Characteristic Table for the Gated SR Latch

# Circuit Diagram and Graphical Symbol for the Gated SR Latch

[Figure 5.5a,c from the textbook]

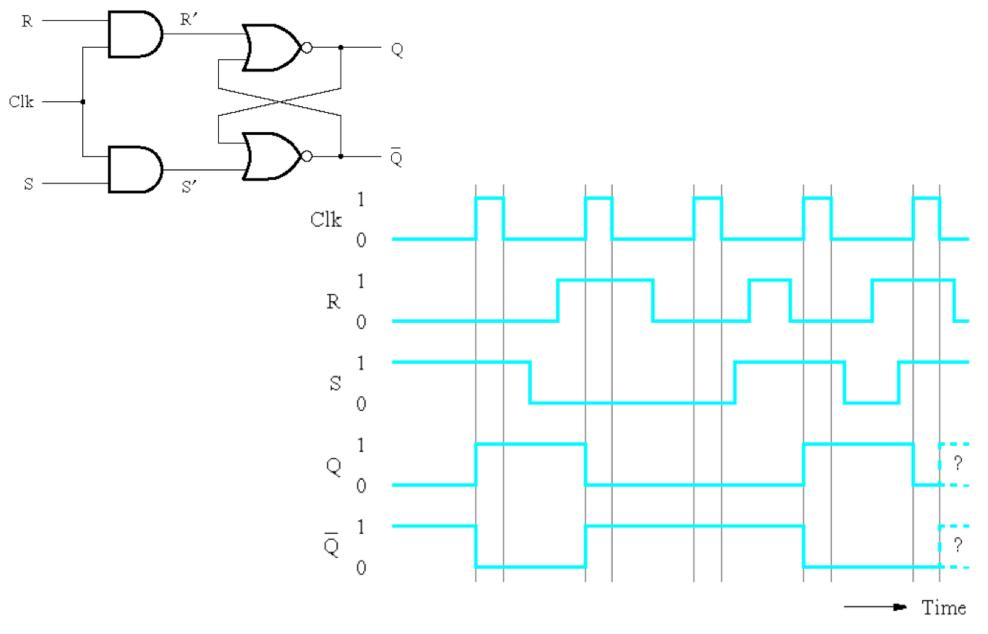

# **Timing Diagram for the Gated SR Latch**

[Figure 5.5c from the textbook]

[Figure 5.6 from the textbook]

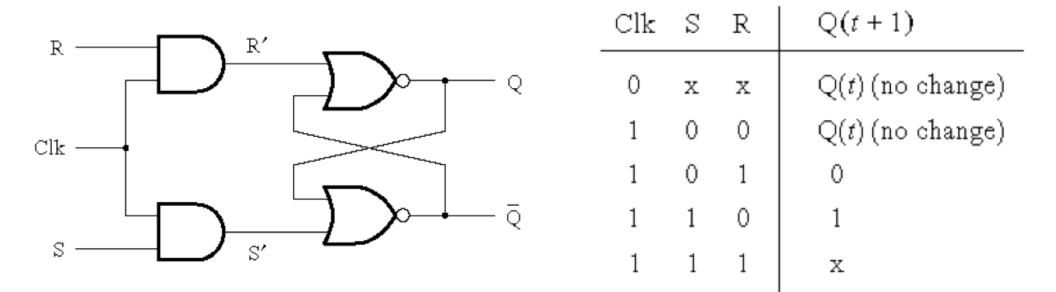

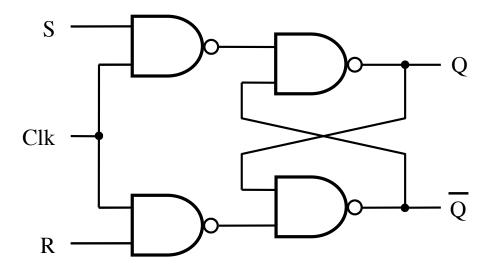

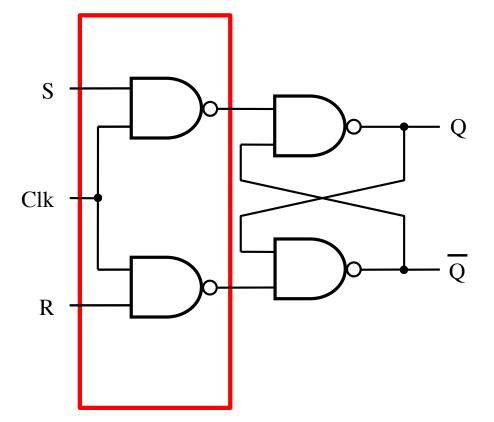

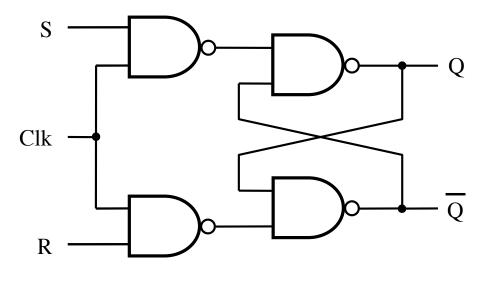

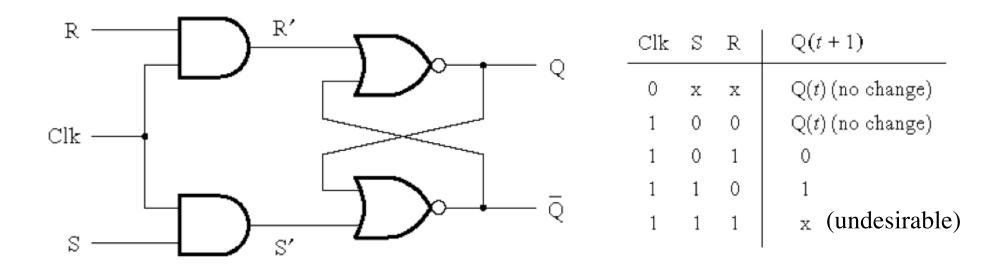

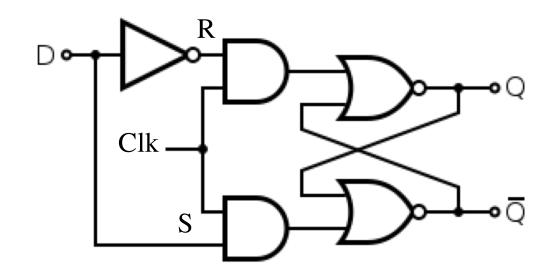

In this case the "gate" is constructed using NAND gates! Not AND gates.

Also, notice that the positions of S and R are now swapped.

Finally, notice that when Clk=1 this turns into the basic latch with NAND gates, i.e., the  $\overline{SR}$  Latch.

# Gated SR latch with NAND gates

### Gated SR latch with NAND gates

Graphical symbols are the same

# Gated SR latch with NAND gates

| Clk | S | R | Q( <i>t</i> + 1) |

|-----|---|---|------------------|

| 0   | x | x | Q(t) (no change) |

| 1   | 0 | 0 | Q(t) (no change) |

| 1   | 0 | 1 | 0                |

| 1   | 1 | 0 | 1                |

| 1   | 1 | 1 | x (undesirable)  |

Characteristic tables are the same

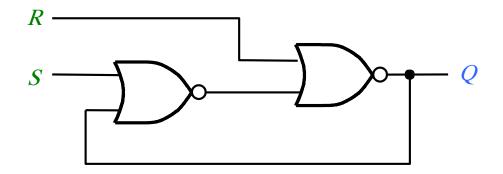

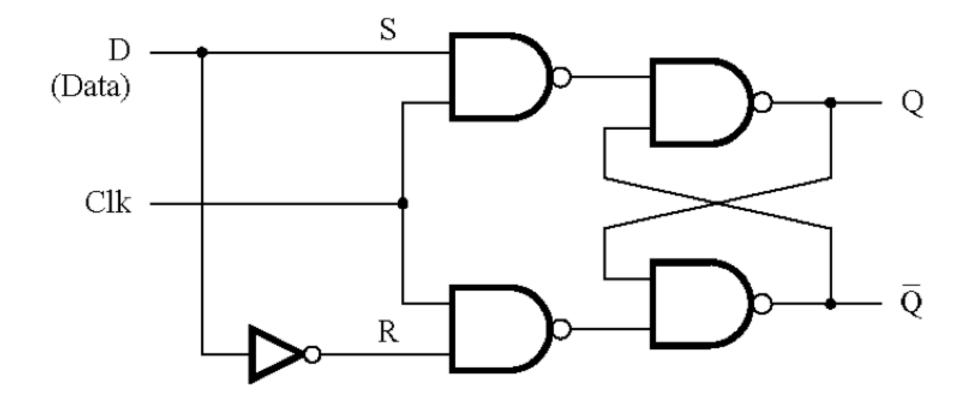

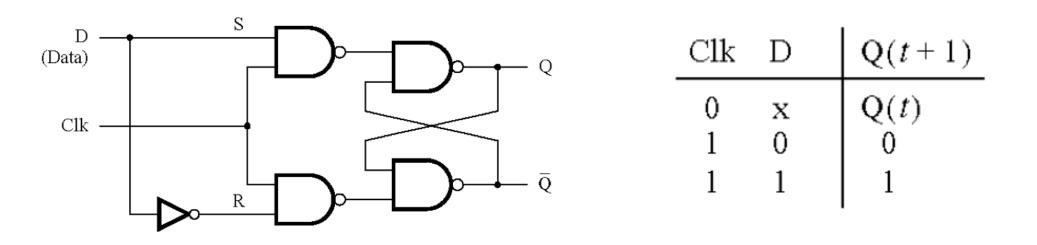

# **Gated D Latch**

# Motivation

- Dealing with two inputs (S and R) could be messy.

For example, we may have to reset the latch before some operations in order to store a specific value but the reset may not be necessary depending on the current state of the latch.

- Why not have just one input and call it D.

- The D latch can be constructed using a simple modification of the SR latch.

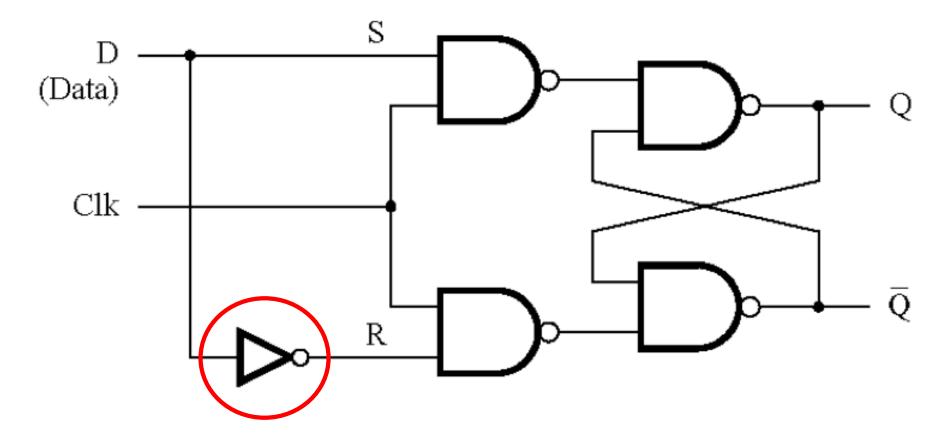

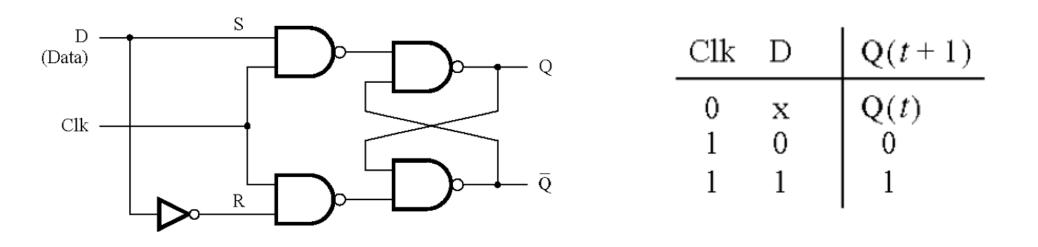

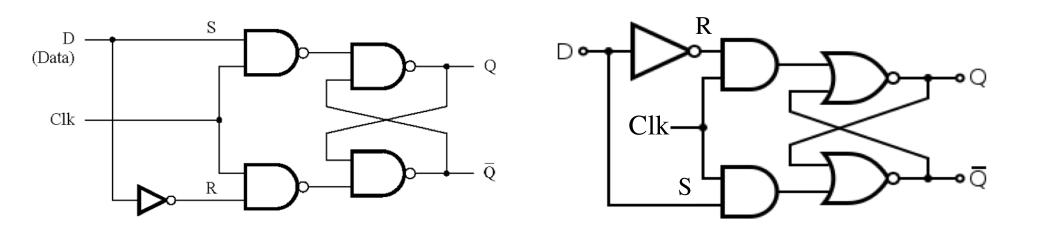

# **Circuit Diagram for the Gated D Latch**

[Figure 5.7a from the textbook]

# **Circuit Diagram for the Gated D Latch**

This is the only new thing here.

[Figure 5.7a from the textbook]

# Circuit Diagram and Characteristic Table for the Gated D Latch

#### Note that it is now impossible to have S=R=1.

[Figure 5.7a,b from the textbook]

# Circuit Diagram and Characteristic Table for the Gated D Latch

#### When Clk=1 the output follows the D input. When Clk=0 the output cannot be changed.

[Figure 5.7a,b from the textbook]

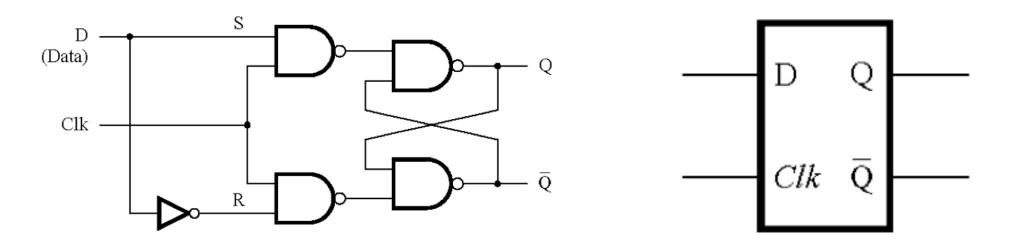

# Circuit Diagram and Graphical Symbol for the Gated D Latch

[Figure 5.7a,c from the textbook]

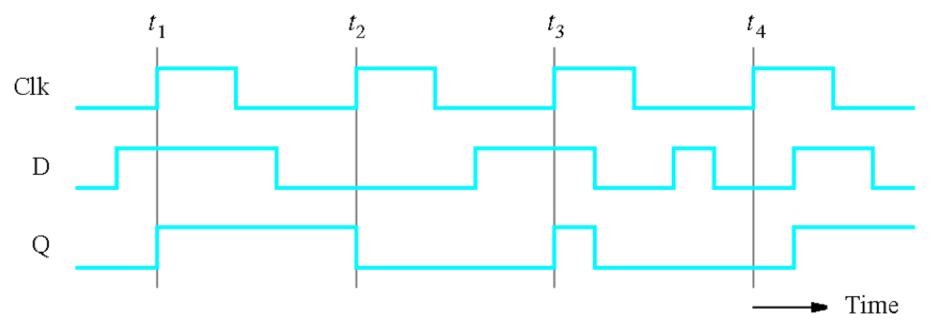

# **Timing Diagram for the Gated D Latch**

[Figure 5.7d from the textbook]

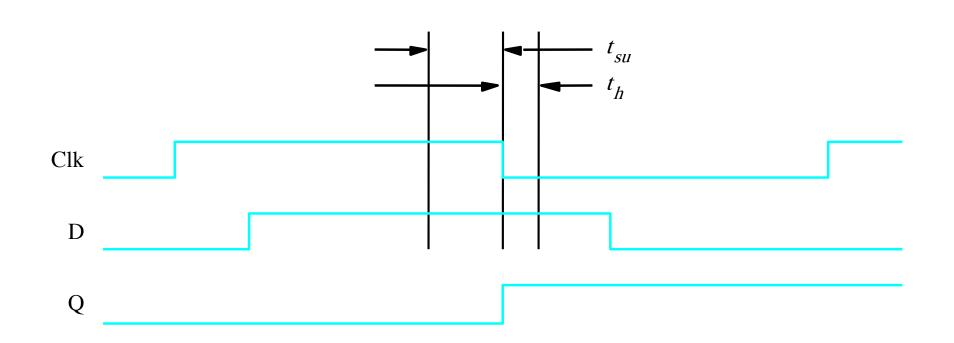

# Setup and hold times

Setup time  $(t_{su})$  – the minimum time that the D signal must be stable prior to the negative edge of the Clock signal.

Hold time  $(t_h)$  – the minimum time that the D signal must remain stable after the negative edge of the Clock signal.

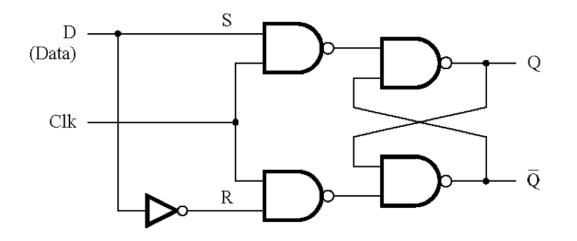

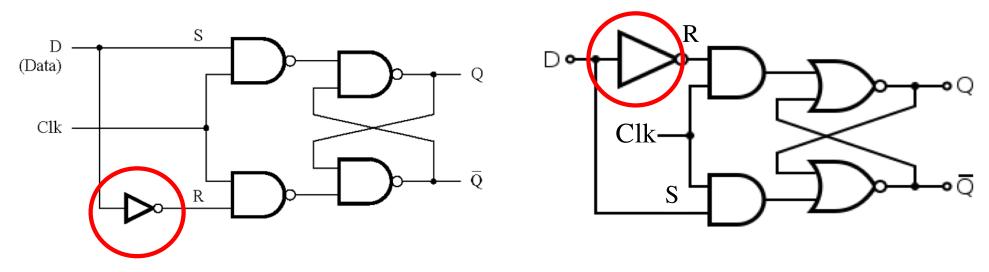

# Circuit Diagram for the Gated D Latch (with the latch implemented using NORs)

[https://en.wikibooks.org/wiki/Digital\_Circuits/Latches]

# Circuit Diagram for the Gated D Latch (with the latch implemented using NORs)

[https://en.wikibooks.org/wiki/Digital\_Circuits/Latches]

# Circuit Diagram for the Gated D Latch (with the latch implemented using NORs)

The NOT gate is now in a different place. Also, S and R are swapped.

[https://en.wikibooks.org/wiki/Digital\_Circuits/Latches]

# **Some Practical Examples**

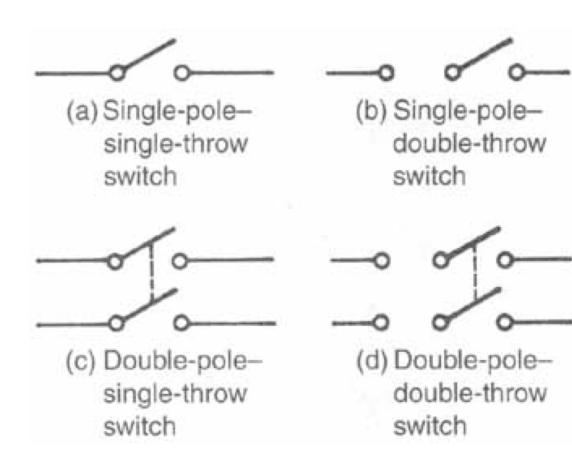

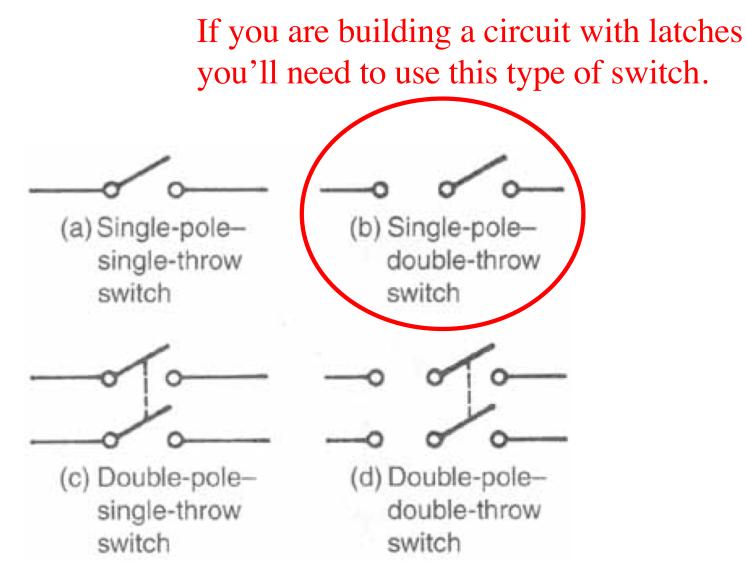

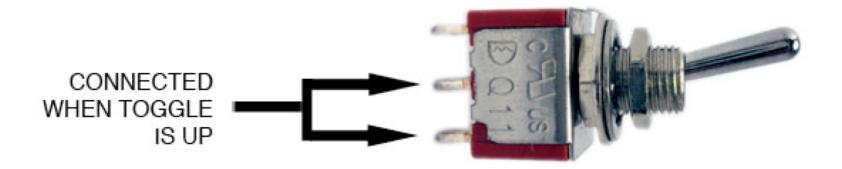

### **Different Types of Switches**

# **Different Types of Switches**

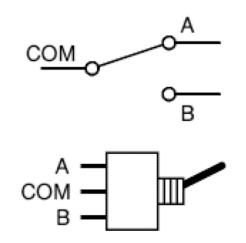

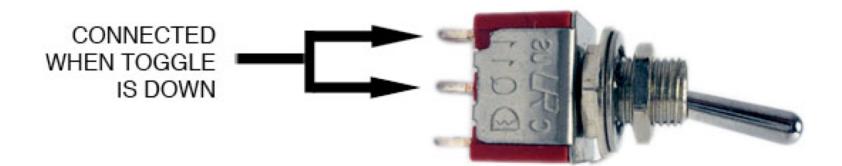

### Single Pole, Double Throw = SPDT

### Single Pole, Double Throw = SPDT

[http://www.cubisteffects.com/images/MIY/Pt3\_Throw.jpg]

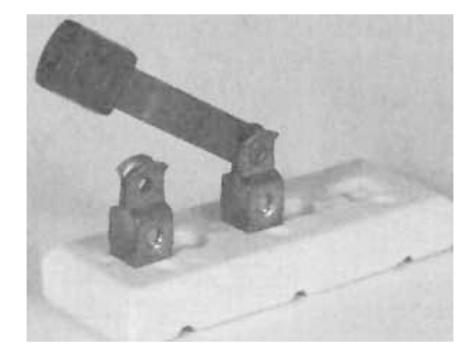

# Single-pole—single-throw manual switch

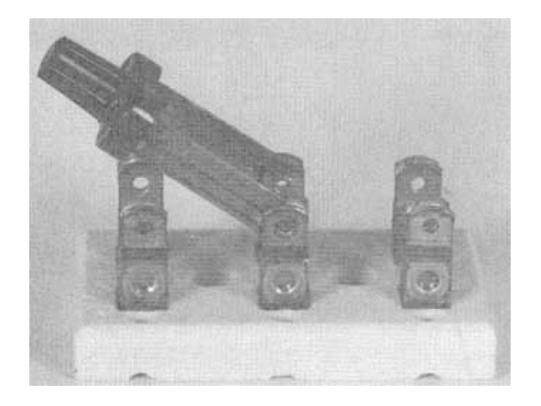

### **Double-pole—double-throw manual switch**

http://www.industrial-electronics.com/Electricity-Refrigeration-Heating-Air-Conditioning\_5b.html

#### The following examples came from this book

# Click to LOOK INSIDE!

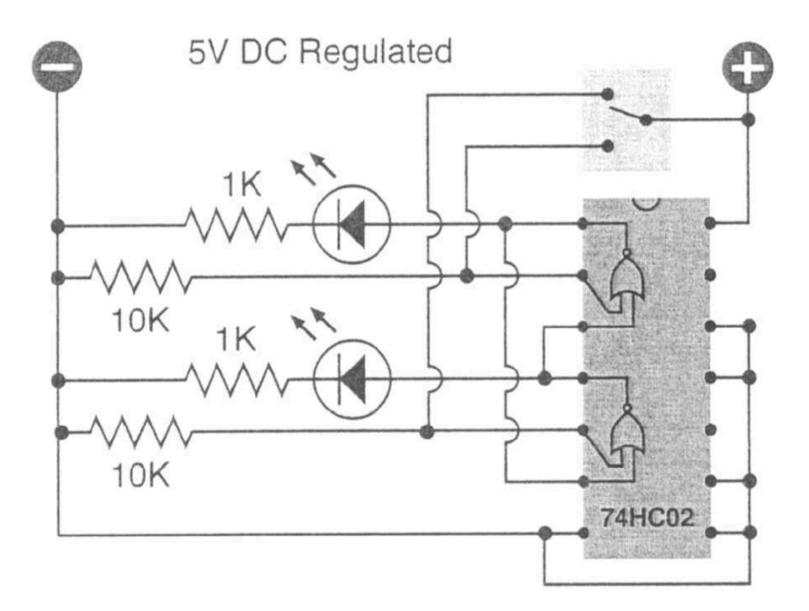

# **A Simple Circuit**

[ Platt 2009 ]

#### Let's Take a Closer Look at This

[ Platt 2009 ]

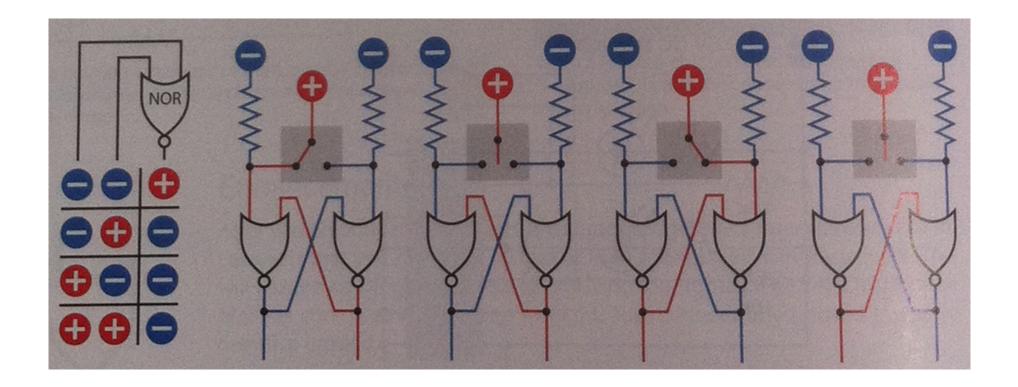

#### A Similar Example with NAND Gates

[ Platt 2009 ]

# **Questions?**

# THE END