**P1. (10 points)** Write the following expressions as Verilog behavioral assign statements without simplifying:

E.g.,  $F = \overline{A}$  as a Verilog assign statement would be "assign F =  $\sim A$ "

A.

$$F = ((A + B) \cdot \overline{B}) + (\overline{A + B} \cdot B)$$

B.  $F = \overline{(A + B) \cdot C} + A + (\overline{C} \cdot B)$

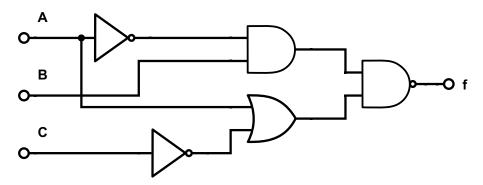

**P2. (10 points)** Give the structural Verilog code for the circuit shown below. The Verilog module name should be "P2".

P3. (10 points) Consider the following Verilog code.

```

module P3(f, a, b, s)

output f;

input a, b, c;

not(n_s, s );

and(s_a, a, n_s);

and(s_b, b, s );

or (f, s_a, s_b);

end module

```

- A. Fix all syntax errors in the Verilog code.

- B. Convert the Verilog code into a Boolean algebra expression in the form  $f(a, b, s) = \cdots$

P4. (20 points) Consider the Boolean algebra expression

$f(A, B, C) = \left(\overline{A} \cdot B \cdot C\right) + B + \left(A\overline{C}B\right).$

- A. Draw a truth table for this expression.

- B. Represent the function as both a minterm and maxterm expression.

- C. From the minterm expression derive a SOP expression.

- D. From the maxterm expression derive a POS expression.

## **P5. (10 points)** Consider the following function:

$$f(A,B,C) = \prod M(0,4,5)$$

- A. Find the simplest POS expression.

- B. Draw an unsimplified circuit diagram for the POS expression.

P6. (20 points) Consider a three-input logic circuit represented by the truth table below.

| A | В | С | f |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

|   |   |   |   |

- A. (5 points) Derive the simplified SOP expression.

- B. **(5 points)** Derive the simplified POS expression.

- C. **(10 points)** Implement one of your expressions using **either** NAND or NOR gates while also keeping the gate cost no greater than 7. Your answer must only contain one type of gate. You may use the 3 and 4 input variants of NAND and NOR gates.

**P7. (20 points):** Consider the 3 input logic circuit with truth table:

| А | В | С | f |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

- A. (5 points) Find the minterm summation expression for the truth table.

- B. **(5 points)** Write the unsimplified SOP equation corresponding to the minterm expression.

- C. (10 points) Using boolean algebra, simplify your SOP equation.