# CprE 281: Digital Logic

#### **Instructor: Alexander Stoytchev**

http://www.ece.iastate.edu/~alexs/classes/

# Intro to Verilog

CprE 281: Digital Logic Iowa State University, Ames, IA Copyright © Alexander Stoytchev

### **Administrative Stuff**

• HW3 is due on Monday Sep 16 @ 10pm

### **Quick Review**

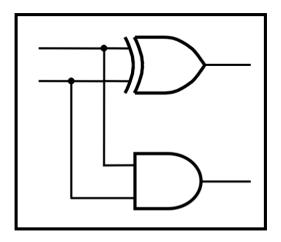

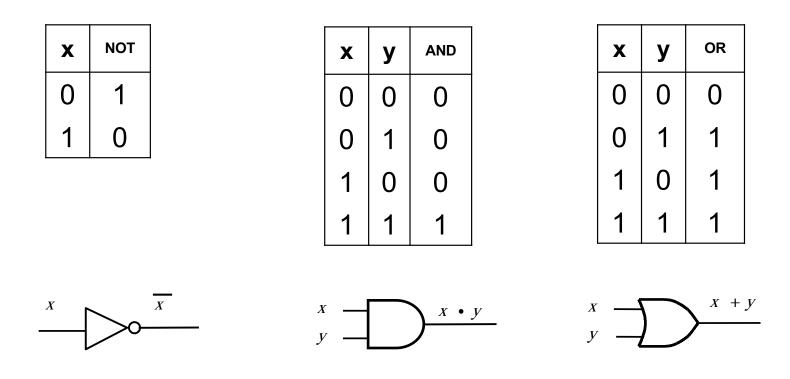

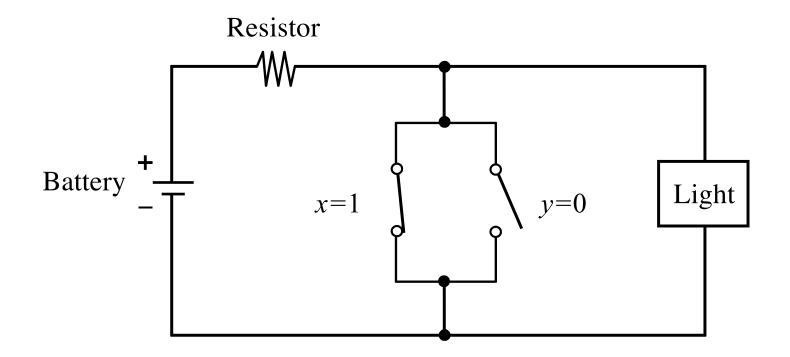

#### **The Three Basic Logic Gates**

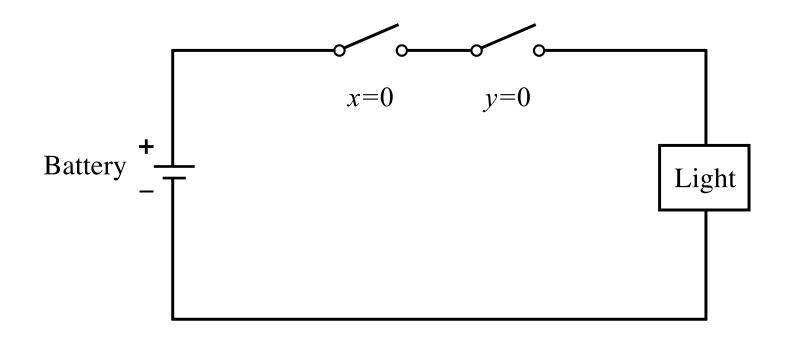

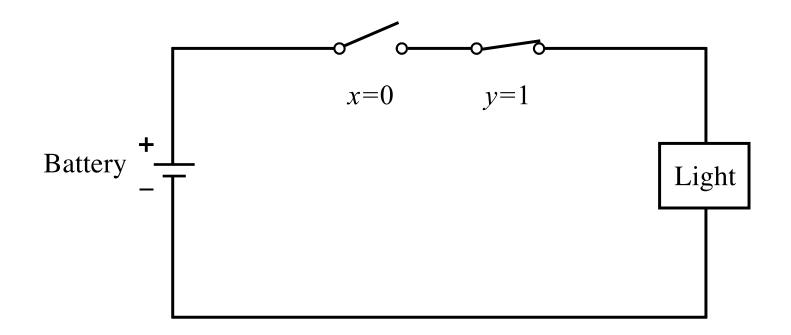

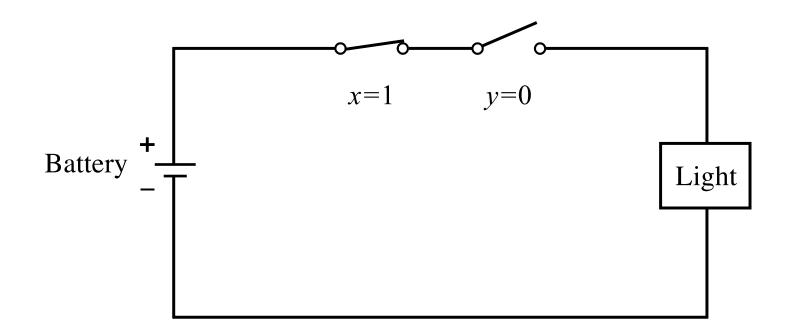

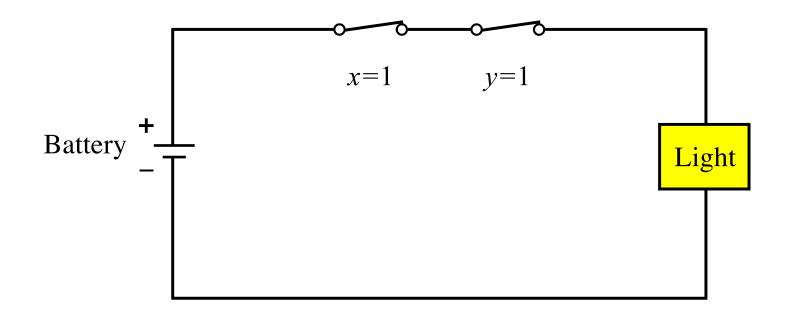

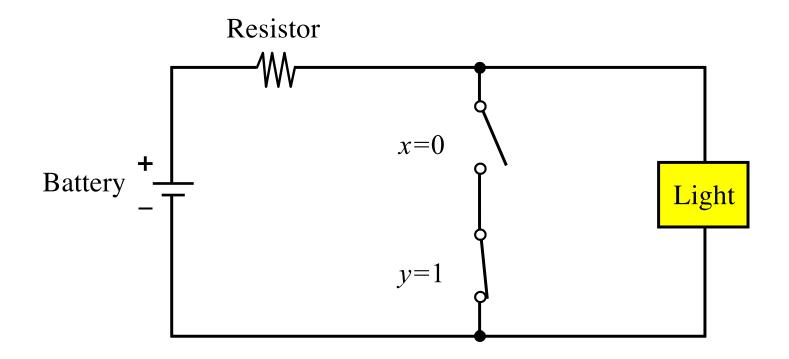

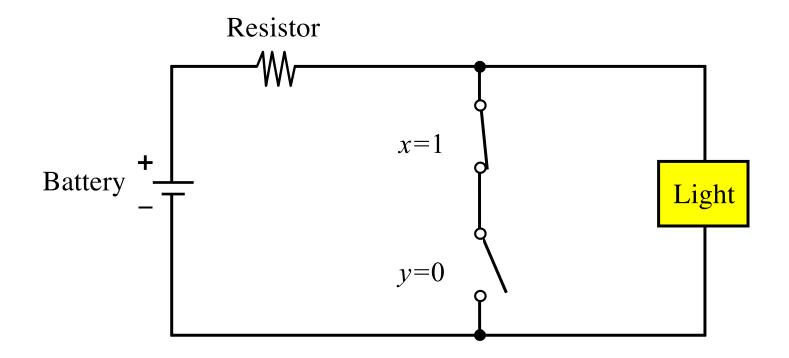

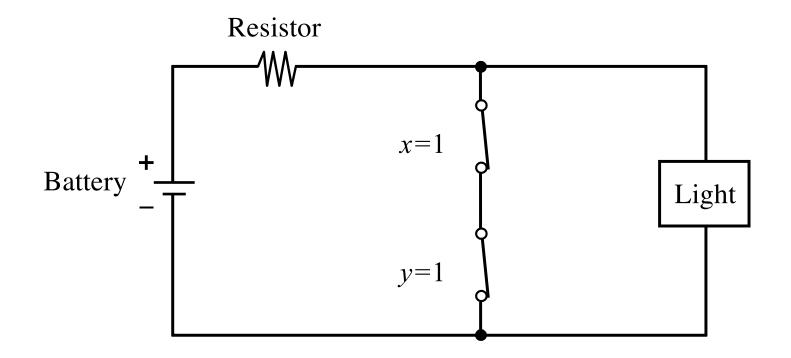

# **AND with Switches**

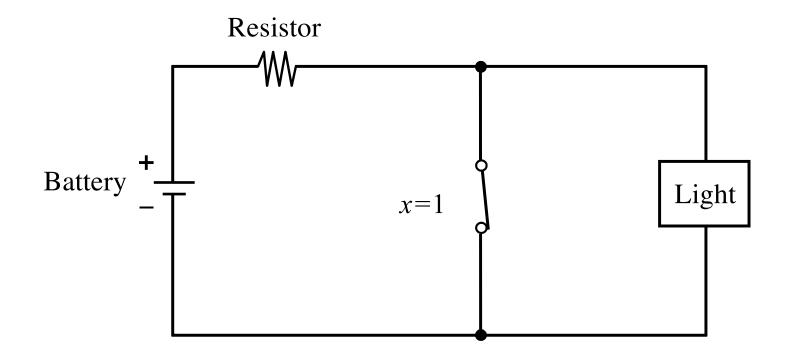

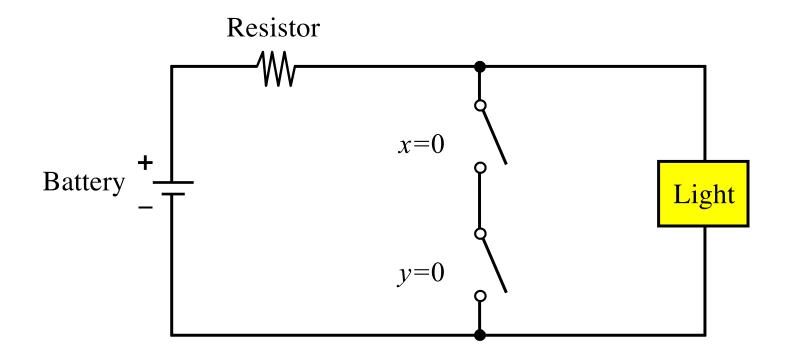

# **NOT with Switches**

# **NAND** with Switches

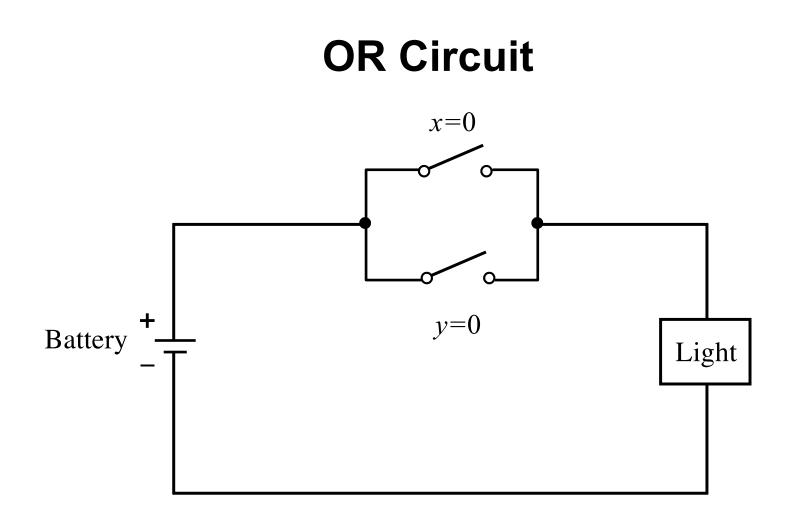

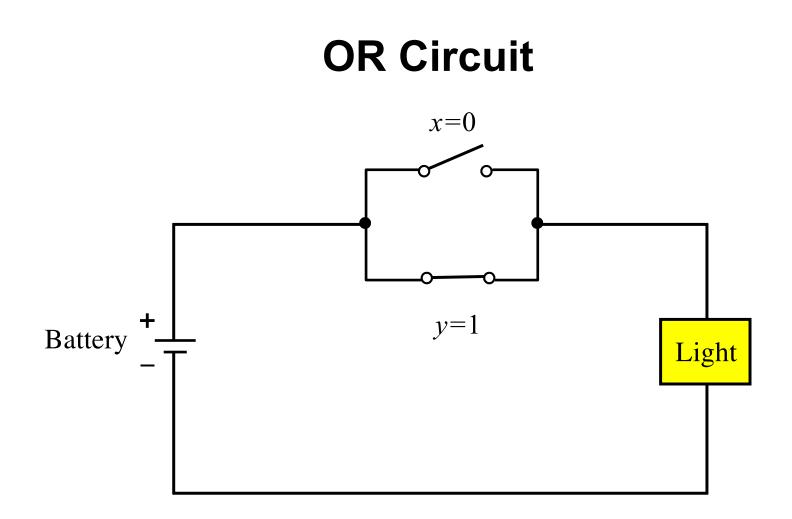

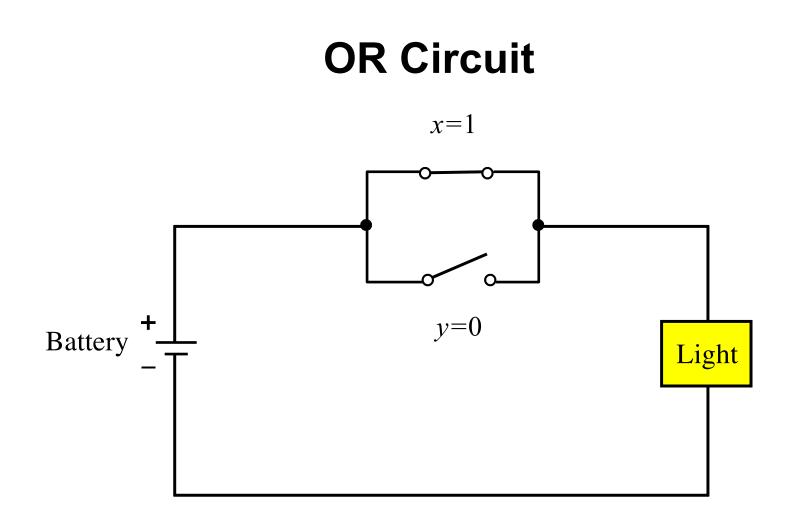

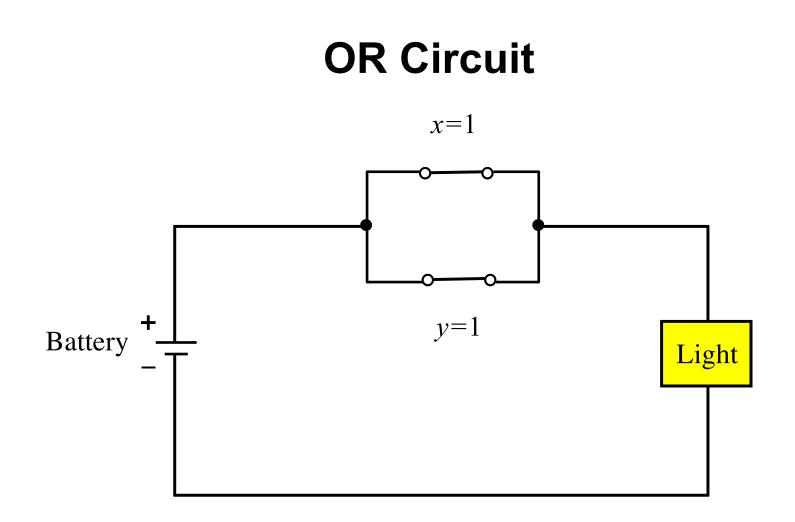

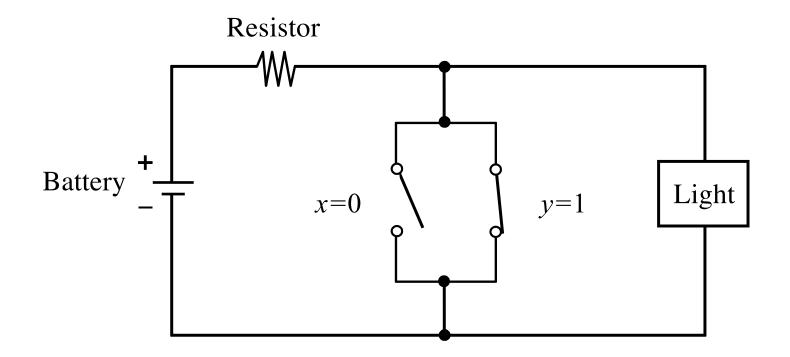

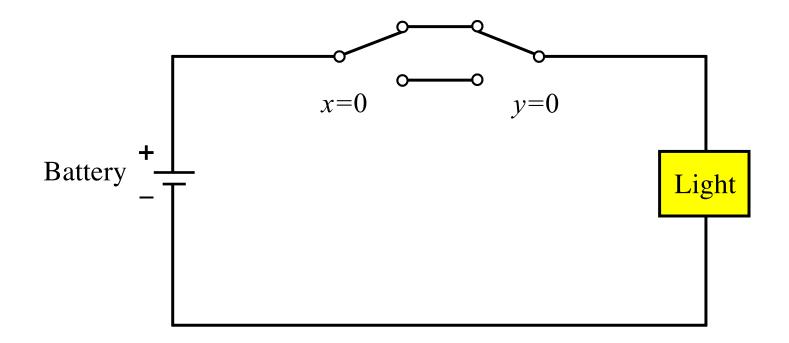

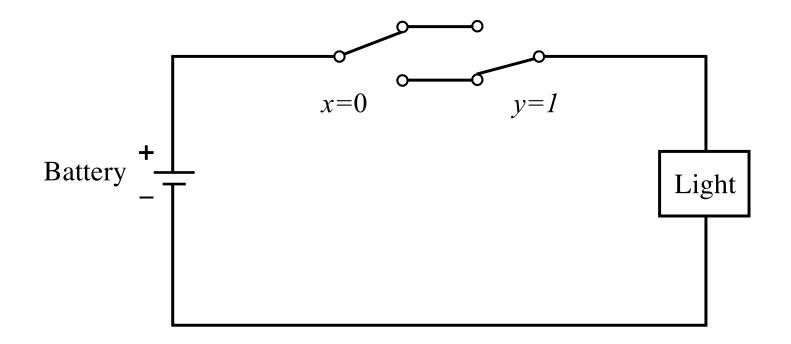

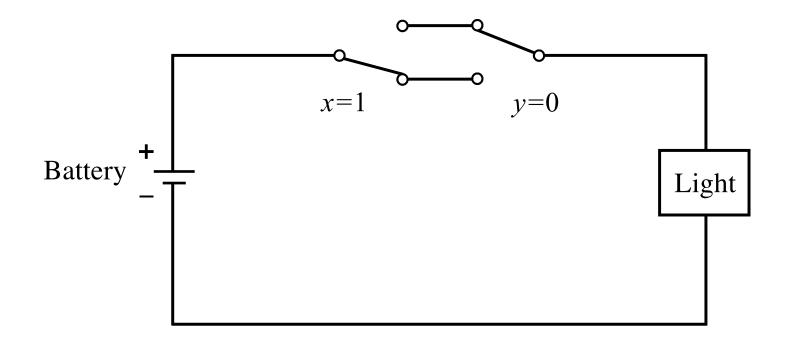

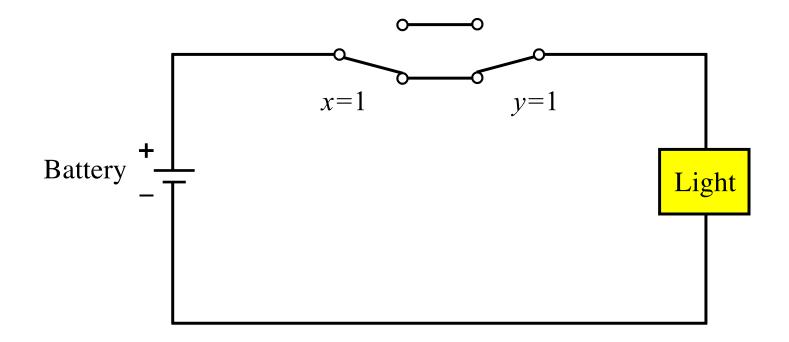

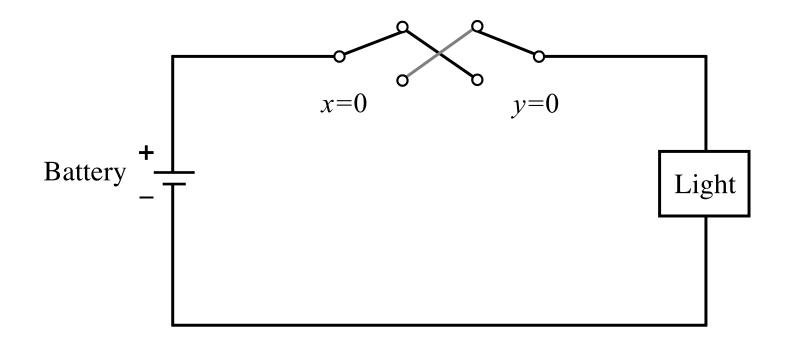

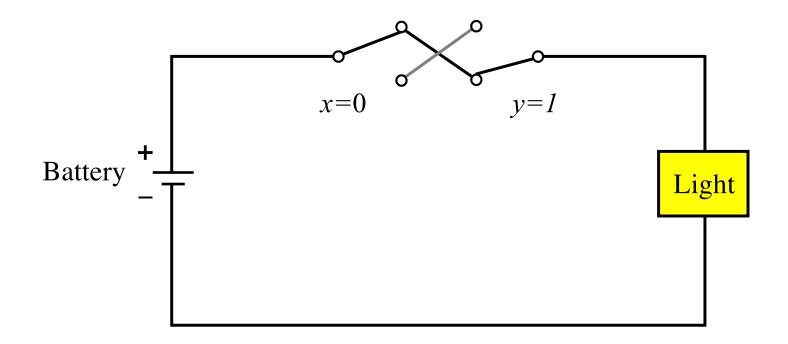

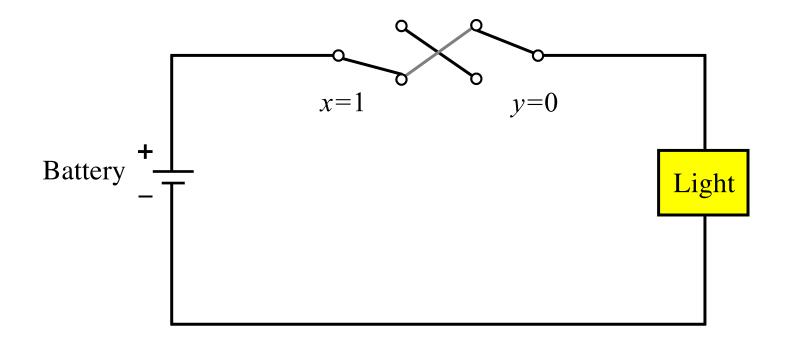

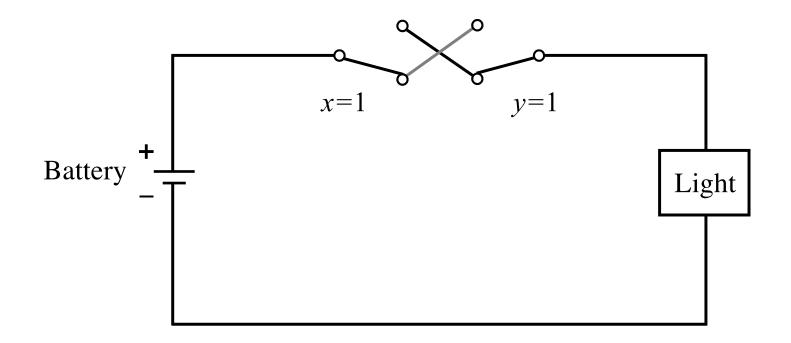

# **OR with Switches**

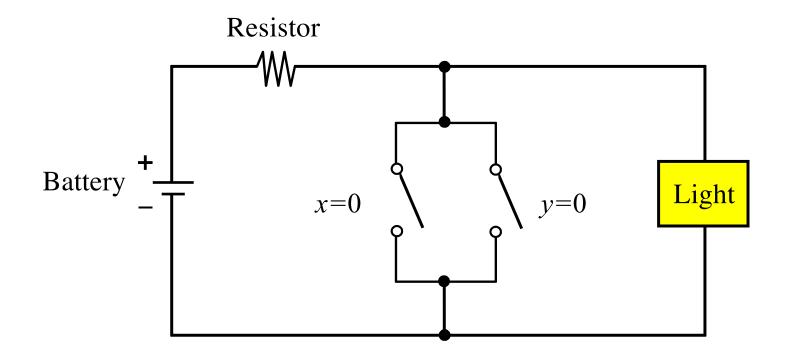

# **NOR with Switches**

#### **The Three Basic Logic Gates**

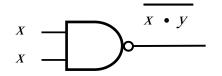

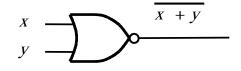

#### NAND and NOR

| X | у | NAND |

|---|---|------|

| 0 | 0 | 1    |

| 0 | 1 | 1    |

| 1 | 0 | 1    |

| 1 | 1 | 0    |

| x | у | NOR |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 0   |

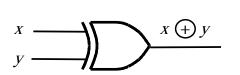

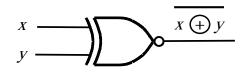

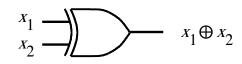

#### **XOR** and **XNOR**

| X | у | XOR |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

| x | у | XNOR |

|---|---|------|

| 0 | 0 | 1    |

| 0 | 1 | 0    |

| 1 | 0 | 0    |

| 1 | 1 | 1    |

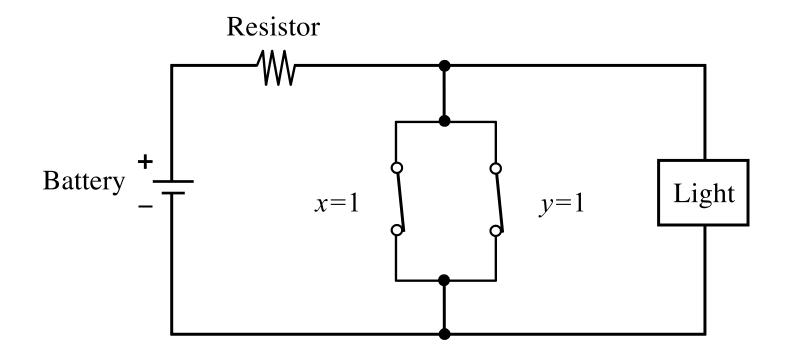

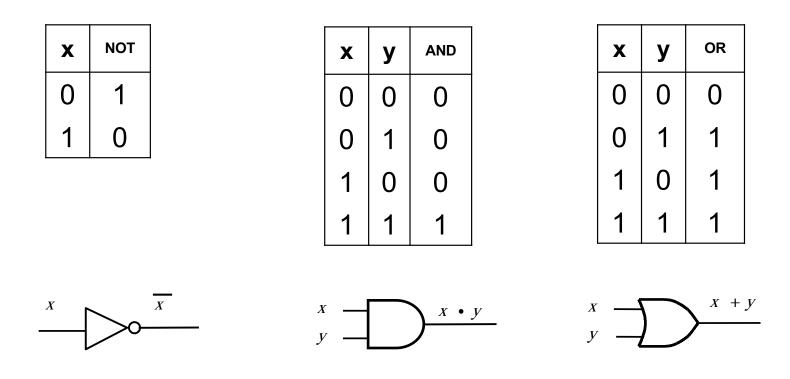

# **XNOR with Switches**

# **XOR with Switches**

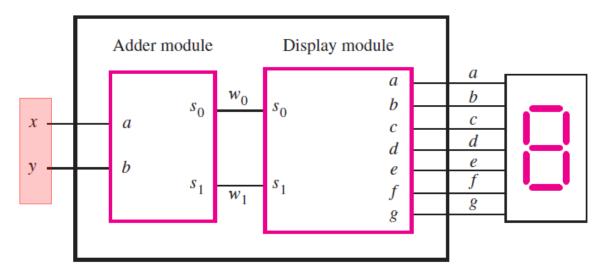

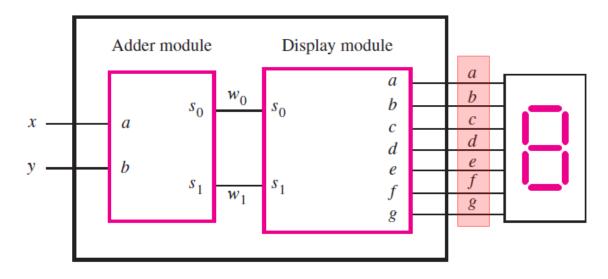

# **7-Segment Display Example**

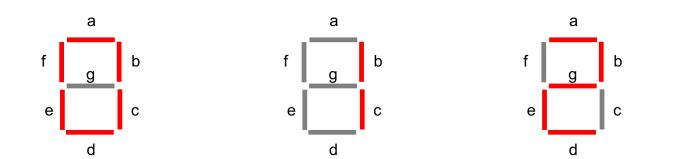

# **7-Segment Display**

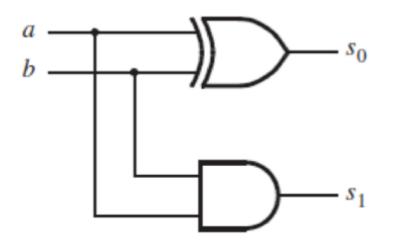

## **Displaying Some Numbers**

#### **Displaying Some Hexadecimal Numbers**

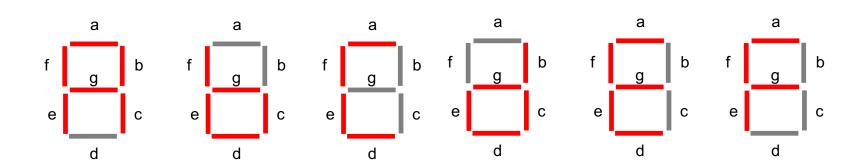

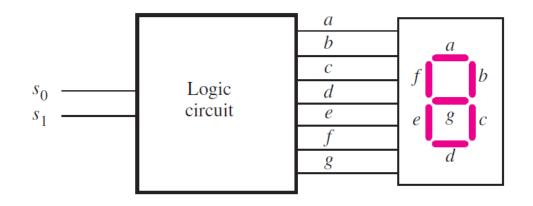

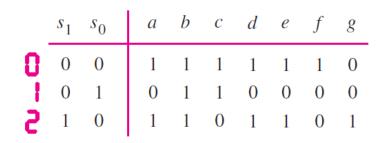

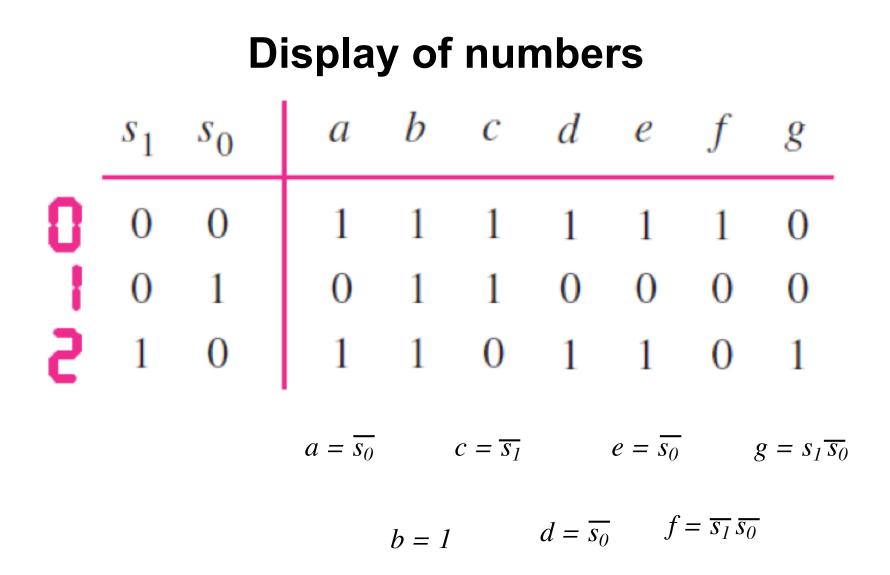

## **Display of numbers**

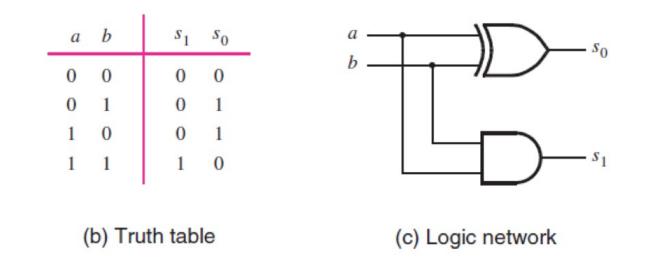

(a) Logic circuit and 7-segment display

(b) Truth table

| Display of numbers |       |                       |   |   |   |   |   |   |          |   |

|--------------------|-------|-----------------------|---|---|---|---|---|---|----------|---|

|                    | $s_1$ | <i>s</i> <sub>0</sub> | а | b | С | d | е | f | <u>g</u> |   |

| 0                  | 0     | 0<br>1<br>0           | 1 | 1 | 1 | 1 | 1 | 1 | 0        | ' |

|                    | 0     | 1                     | 0 | 1 | 1 | 0 | 0 | 0 | 0        |   |

| 2                  | 1     | 0                     | 1 | 1 | 0 | 1 | 1 | 0 | 1        |   |

# Intro to Verilog

# History

- Created in 1983/1984

- Verilog-95 (IEEE standard 1364-1995)

- Verilog 2001 (IEEE Standard 1364-2001)

- Verilog 2005 (IEEE Standard 1364-2005)

- SystemVerilog

- SystemVerilog 2009 (IEEE Standard 1800-2009).

# HDL

- Hardware Description Language

- Verilog HDL

- VHDL

## Verilog HDL != VHDL

- These are two different Languages!

- Verilog is closer to C

- VHDL is closer to Ada

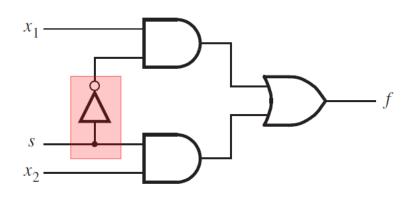

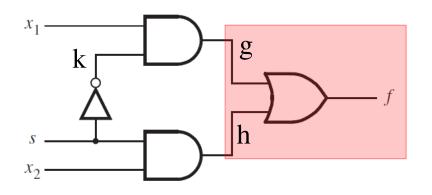

#### Sample Verilog Program

module example1 (x1, x2, s, f);

input x1, x2, s;

output f;

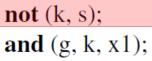

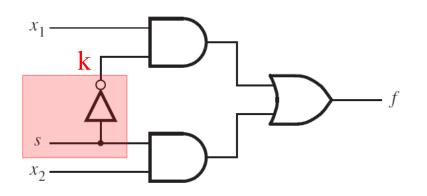

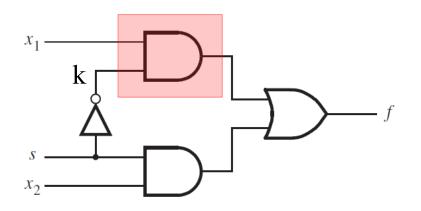

**not** (k, s); **and** (g, k, x1); **and** (h, s, x2); **or** (f, g, h);

endmodule

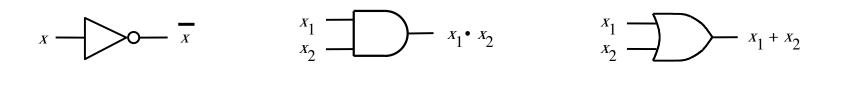

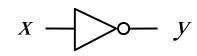

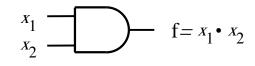

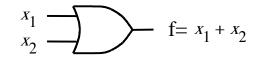

#### **The Three Basic Logic Gates**

NOT gate

AND gate

OR gate

#### You can build any circuit using only these three gates

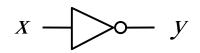

## How to specify a NOT gate in Verilog

NOT gate

## How to specify a NOT gate in Verilog

we'll use the letter y for the output

NOT gate

## How to specify a NOT gate in Verilog

not (y, x);

NOT gate

Verilog code

## How to specify an AND gate in Verilog

and (f, x1, x2);

AND gate

Verilog code

## How to specify an OR gate in Verilog

or (f, x1, x2);

OR gate

Verilog code

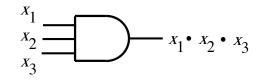

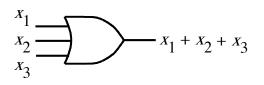

## **3-input Logic Gates**

3-input AND gate

3-input OR gate

and (f, x1, x2, x3);

or (f, x1, x2, x3);

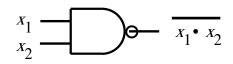

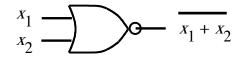

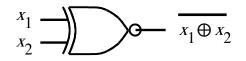

## **Other Logic Gates**

NAND gate

NOR gate

XOR gate

XNOR gate

#### **Other Logic Gates**

# **Structural Verilog**

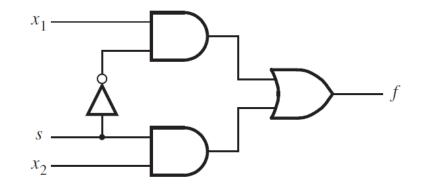

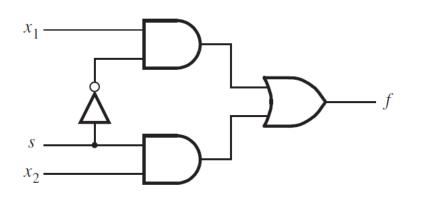

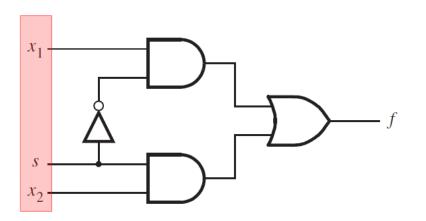

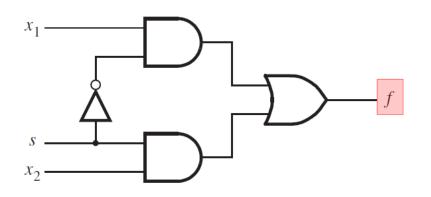

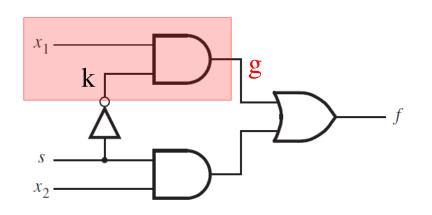

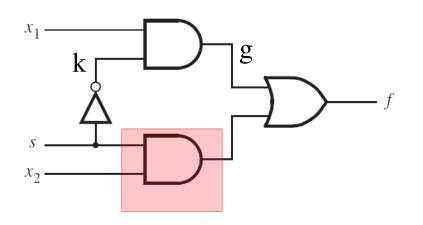

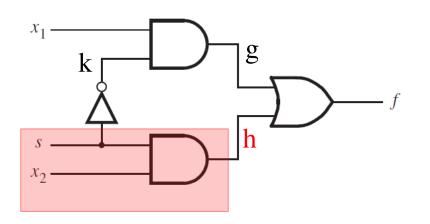

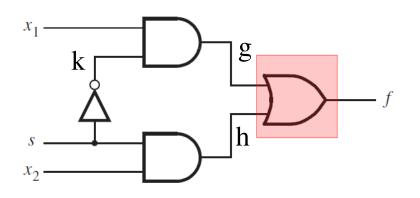

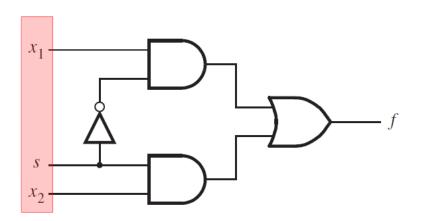

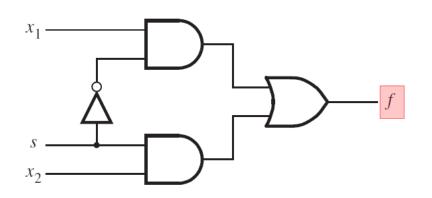

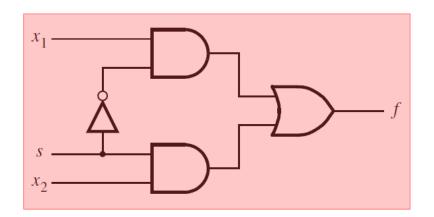

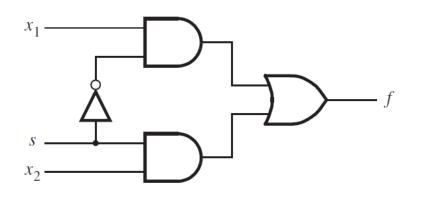

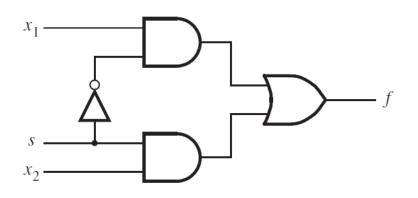

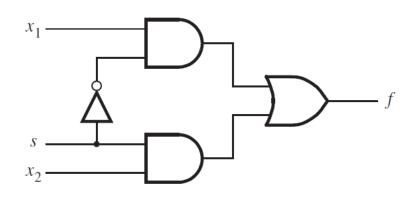

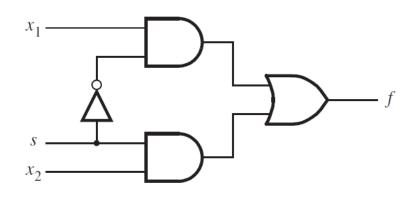

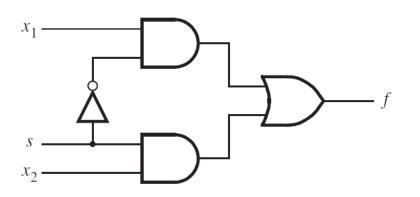

# 2-to-1 Multiplexer in Verilog (structural syntax)

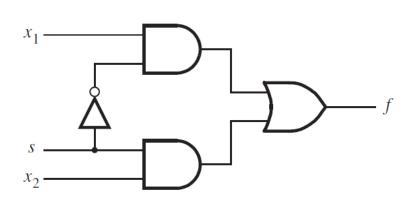

# **2-1 Multiplexer**

module example1 (x1, x2, s, f);

input x1, x2, s;

output f;

**not** (k, s); **and** (g, k, x1); **and** (h, s, x2); **or** (f, g, h);

endmodule

module example1 (x1, x2, s, f);

input x1, x2, s;

output f;

**not** (k, s); **and** (g, k, x1); **and** (h, s, x2); **or** (f, g, h);

endmodule

module example1 (x1, x2, s, f);

input x1, x2, s;

output f;

**not** (k, s); **and** (g, k, x1); **and** (h, s, x2); **or** (f, g, h);

endmodule

module example1 (x1, x2, s, f);

input x1, x2, s;

output f;

and (h, s, x2); or (f, g, h);

endmodule

module example1 (x1, x2, s, f);

input x1, x2, s;

output f;

#### **not** (k, s); **and** (g, k, x1);

**and** (h, s, x2); **or** (f, g, h);

endmodule

module example1 (x1, x2, s, f);

input x1, x2, s;

output f;

**not** (k, s); **and** (g, k, x1); **and** (h, s, x2); **or** (f, g, h);

endmodule

module example1 (x1, x2, s, f);

input x1, x2, s;

output f;

**not** (k, s); **and** (g, k, x1); **and** (h, s, x2); **or** (f, g, h);

endmodule

module example1 (x1, x2, s, f);

input x1, x2, s;

output f;

not (k, s); and (g, k, x1); and (h, s, x2); or (f, g, h);

module example1 (x1, x2, s, f);

input x1, x2, s;

output f;

not (k, s); and (g, k, x1); and (h, s, x2); or (f, g, h);

endmodule

module example1 (x1, x2, s, f);

input x1, x2, s;

output f;

**not** (k, s); **and** (g, k, x1); **and** (h, s, x2); **or** (f, g, h);

endmodule

module example1 (x1, x2, s, f);

input x1, x2, s;

output f;

**not** (k, s); **and** (g, k, x1); **and** (h, s, x2); **or** (f, g, h);

endmodule

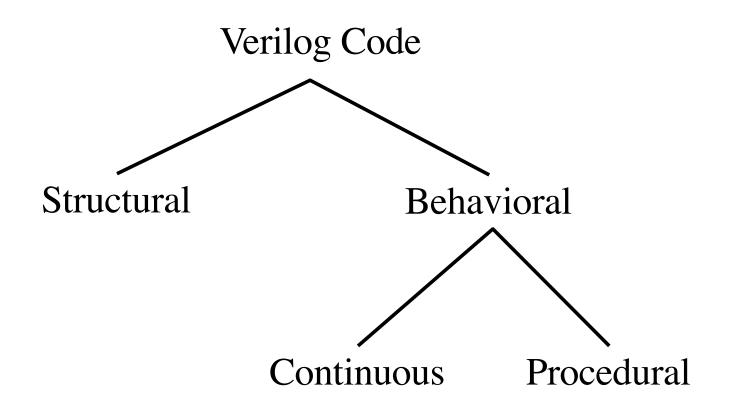

# **Behavioral Verilog**

# 2-to-1 Multiplexer in Verilog (behavioral-continuous syntax)

// Behavioral-Continuous specification

module example3 (x1, x2, s, f);

input x1, x2, s;

output f;

**assign**

$$f = (\sim s \& x1) | (s \& x2);$$

endmodule

// Behavioral-Continuous specification

module example3 (x1, x2, s, f);

input x1, x2, s;

output f;

**assign**

$$f = (\sim s \& x1) | (s \& x2);$$

endmodule

[Figure 2.36 from the textbook]

// Behavioral-Continuous specification

module example3 (x1, x2, s, f);

input x1, x2, s;

output f;

**assign**

$$f = (\sim s \& x1) | (s \& x2);$$

// Behavioral-Continuous specification

module example3 (x1, x2, s, f);

input x1, x2, s;

output f;

**assign**

$$f = (\sim s \& x1) | (s \& x2);$$

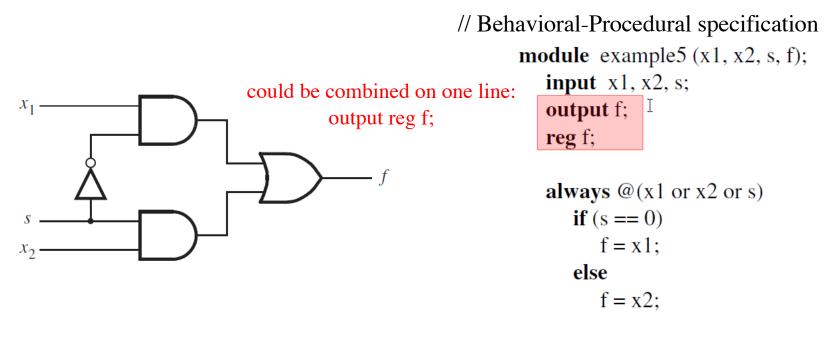

# 2-to-1 Multiplexor in Verilog (behavioral-procedural specification)

// Behavioral-Procedural specification

module example5 (x1, x2, s, f);

input x1, x2, s;

output f; I

reg f;

endmodule

// Behavioral-Procedural specification

module example5 (x1, x2, s, f);

input x1, x2, s;

output f; I

reg f;

procedural statement

always

$$@(x1 \text{ or } x2 \text{ or } s)$$

if  $(s == 0)$

$f = x1;$

else

$f = x2;$

The always block is executed only when one of the signals in the sensitivity list has changed its value.

// Behavioral-Procedural specification module example5 (x1, x2, s, f); input x1, x2, s; output f; I reg f; always @(x1 or x2 or s) if (s == 0) f = x1; else f = x2;

reg: does not need to be computed all the time. It stores a value until you write to it a new value. // Behavioral-Procedural specification

module example5 (x1, x2, s, f);

input x1, x2, s;

output f; I of type register

reg f; (can store a value)

Because the signal f is updated inside a procedural statement (i.e., inside an always block) it must be declared of type reg. This is required so it can hold its value until the next time the always block is executed, which will happen only when one of the signals on the sensitivity list has changed its value.

[Figure 2.36 from the textbook]

// Behavioral-Procedural specification

module example5 (x1, x2, s, f);

input x1, x2, s;

output f; I of type register

reg f; (can store a value)

endmodule

endmodule

- one output f

- two inputs:  $x_1$  and  $x_2$

- It also has another input line s

- If s=0, then the output is equal to x<sub>1</sub>

- If s=1, then the output is equal to x<sub>2</sub>

// Behavioral-Procedural specification

module example5 (x1, x2, s, f);

input x1, x2, s;

output f; I

reg f;

always @(x1 or x2 or s)

if (s == 0)

f = x1;

else

f = x2;

A 2-to-1 Multiplexer has:

- one output f

- two inputs:  $x_1$  and  $x_2$

- It also has another input line s

- If s=0, then the output is equal to x<sub>1</sub>

- If s=1, then the output is equal to x<sub>2</sub>

// Behavioral-Procedural specification

module example5 (x1, x2, s, f);

input x1, x2, s;

output f; I

reg f;

```

always @(x1 or x2 or s)

if (s == 0)

f = x1;

else

f = x2;

```

# always@ syntax

always @(x,y)

always @(x or y)

always @(\*)

always @\*

# always@ syntax

always @(x,y)

always @(x or y)

always @(\*)

always @\*

Leave it to the Verilog compiler to figure out which signals appear in the always block and add them to the sensitivity list.

// Behavioral-Procedural specification

module example5 (input x1, x2, s, output reg f);

```

always @(x1, x2, s)

if (s == 0)

f = x1;

else

f = x2;

```

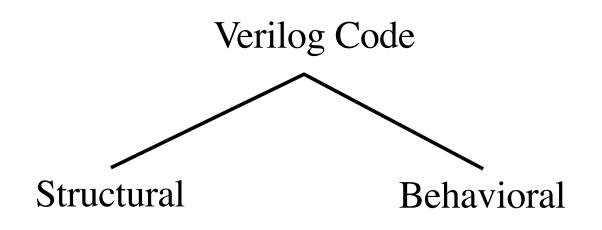

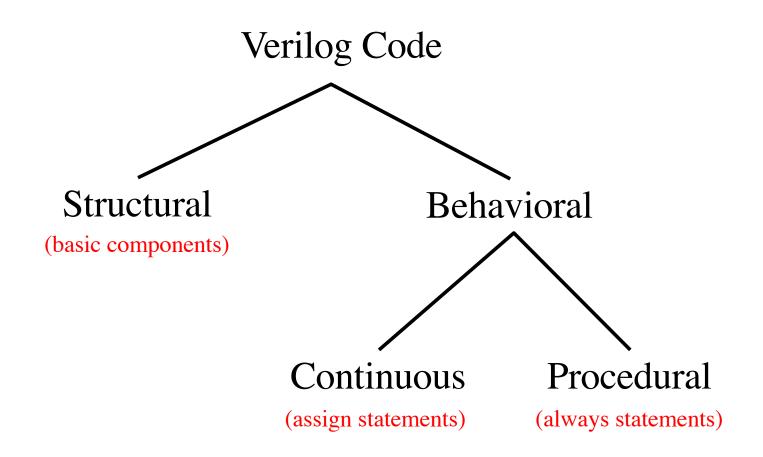

# **Structural v.s. Behavioral**

# Verilog Code: Structural v.s. Behavioral

// Structural specification

module example1 (x1, x2, s, f);

input x1, x2, s;

output f;

endmodule

// Behavioral-Continuous specification

module example3 (x1, x2, s, f);

input x1, x2, s;

output f;

**assign**  $f = (\sim s \& x1) | (s \& x2);$

endmodule

[Figure 2.40 from the textbook]

# Verilog Code: Structural v.s. Behavioral

// Structural specification

module example1 (x1, x2, s, f);

input x1, x2, s;

output f;

#### endmodule

// Behavioral-Procedural specification

module example5 (x1, x2, s, f);

input x1, x2, s;

output f; I

reg f;

```

always @(x1 or x2 or s)

if (s == 0)

f = x1;

else

f = x2;

```

endmodule

# Behavioral Verilog: Continuous v.s. Procedural

// Behavioral-Continuous specification

module example3 (x1, x2, s, f);

input x1, x2, s;

output f;

**assign**  $f = (\sim s \& x1) | (s \& x2);$

endmodule

// Behavioral-Procedural specification

module example5 (x1, x2, s, f);

input x1, x2, s;

output f; I

reg f;

```

always @(x1 or x2 or s)

if (s == 0)

f = x1;

else

f = x2;

```

endmodule

[Figure 2.40 from the textbook]

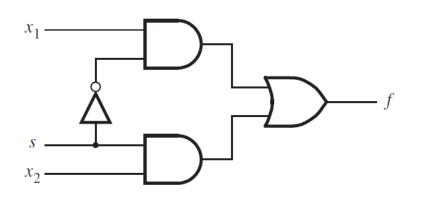

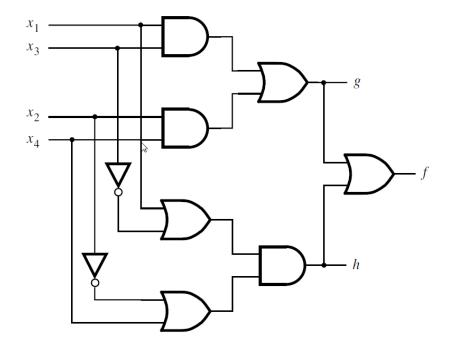

# **Another Example**

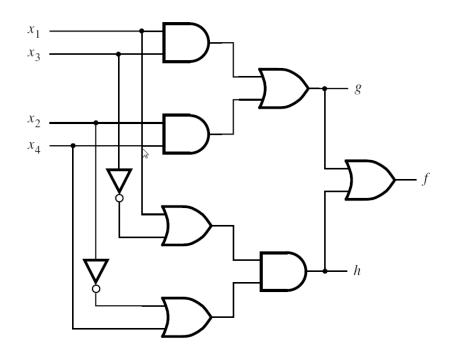

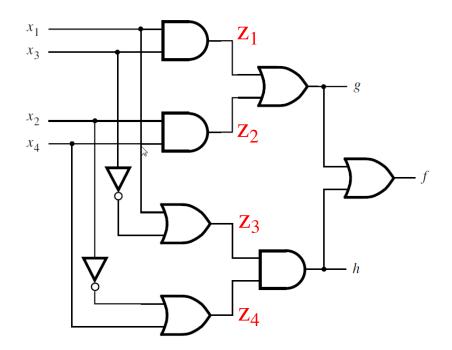

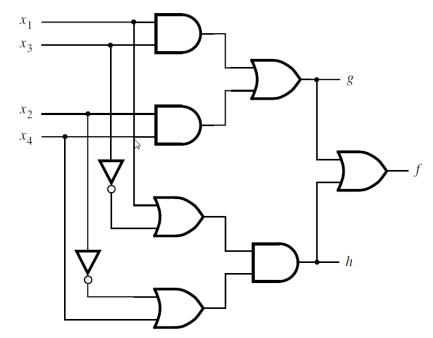

# Let's Write the Code for This Circuit

<sup>[</sup>Figure 2.39 from the textbook]

# **Structural Verilog**

module example2 (x1, x2, x3, x4, f, g, h);

input x1, x2, x3, x4;

output f, g, h;

and (z1, x1, x3); and (z2, x2, x4); or (g, z1, z2); or (z3, x1, ~x3); or (z4, ~x2, x4); and (h, z3, z4); or (f, g, h);

# **Structural Verilog**

module example2 (x1, x2, x3, x4, f, g, h);

input x1, x2, x3, x4;

output f, g, h;

```

and (z1, x1, x3);

and (z2, x2, x4);

or (g, z1, z2);

or (z3, x1, ~x3);

or (z4, ~x2, x4);

and (h, z3, z4);

or (f, g, h);

```

# **Behavioral Verilog**

module example4 (x1, x2, x3, x4, f, g, h);

input x1, x2, x3, x4;

output f, g, h;

**assign** g = (x1 & x3) | (x2 & x4); **assign**  $h = (x1 | \sim x3) \& (\sim x2 | x4);$ **assign** f = g | h;

#### Structural v.s. Behavioral

```

module example2 (x1, x2, x3, x4, f, g, h);

input x1, x2, x3, x4;

output f, g, h;

module example4 (x1, x2, x3, x4, f, g, h);

input x1, x2, x3, x4;

and (z1, x1, x3);

output f, g, h;

and (z2, x2, x4);

or (g, z1, z2);

assign g = (x1 \& x3) | (x2 \& x4);

or (z3, x1, ~x3);

assign h = (x1 | \sim x3) \& (\sim x2 | x4);

or (z4, ~x2, x4);

assign f = g | h;

and (h, z3, z4);

or (f, g, h);

endmodule

endmodule

// behavioral-continuous

// structural

```

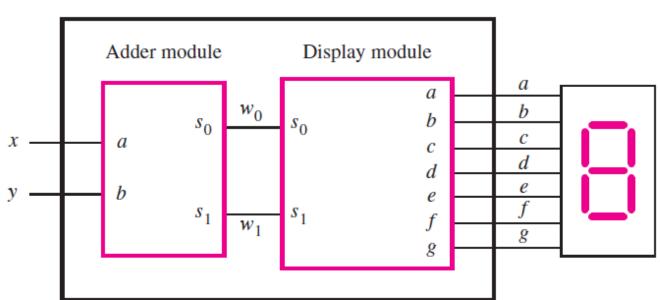

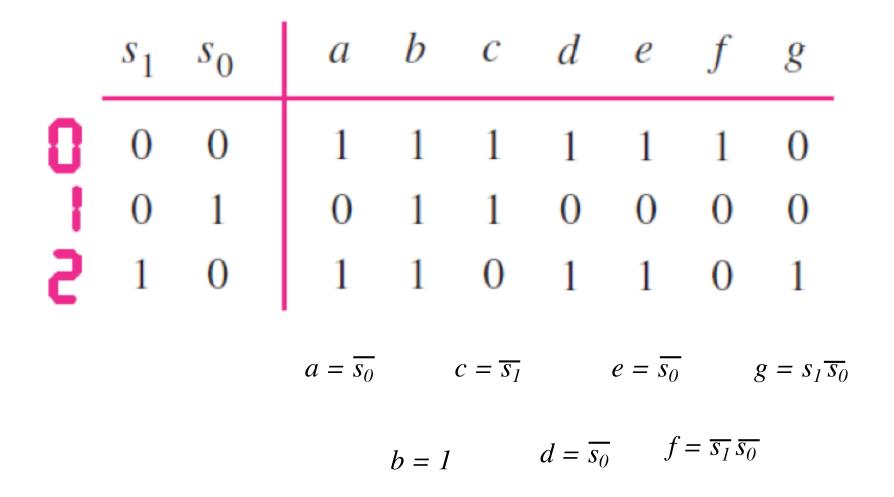

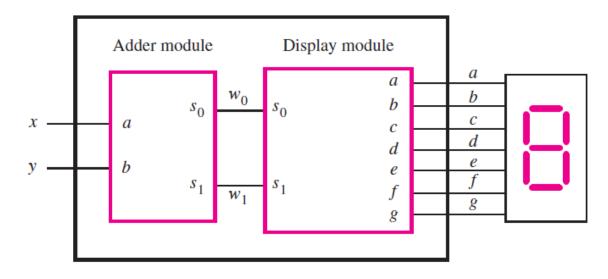

## Yet Another Example

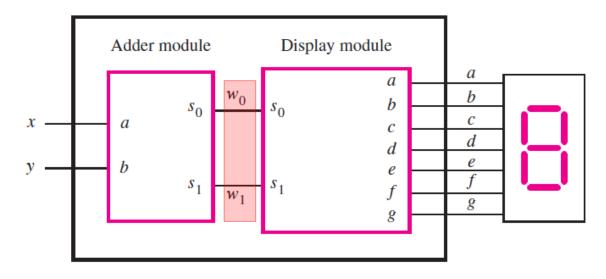

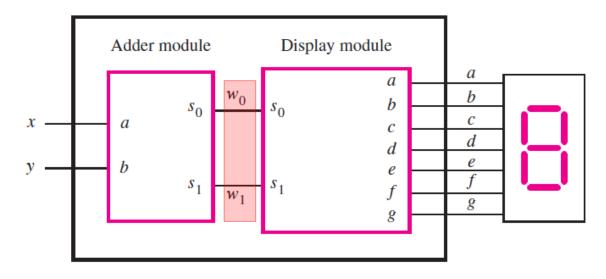

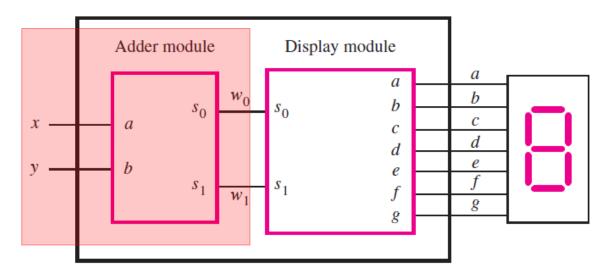

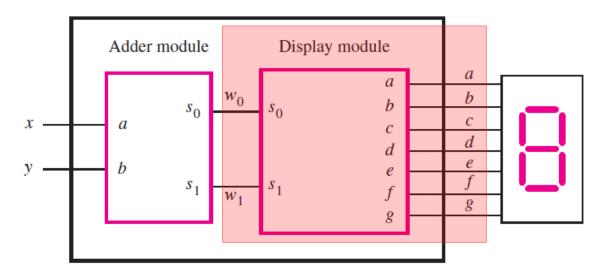

#### A logic circuit with two modules

Top-level module

[Figure 2.44 from the textbook]

#### The adder module

| a          | 0   | 0   | 1   | 1   |

|------------|-----|-----|-----|-----|

| + <i>b</i> | + 0 | +1  | + 0 | + 1 |

| $s_1 s_0$  | 0 0 | 0 1 | 0 1 | 10  |

(a) Evaluation of S = a + b

[Figure 2.12 from the textbook]

#### The adder module

// An adder module

module adder (a, b, s1, s0);

input a, b;

output s1, s0;

**assign** s1 = a & b; **assign** s0 = a ^ b;

endmodule

[Figure 2.45 from the textbook]

#### The display module

#### The display module

| $a = \overline{s_0}$                 | <pre>// A module for driving a 7-segment display<br/>module display (s1, s0, a, b, c, d, e, f, g);</pre> |

|--------------------------------------|----------------------------------------------------------------------------------------------------------|

| b = 1                                | input s1, s0;                                                                                            |

|                                      | <b>output</b> a, b, c, d, e, f, g;                                                                       |

| $c = \overline{s_I}$                 | accian a - accor                                                                                         |

|                                      | assign $a = \sim s0;$                                                                                    |

| $d = \overline{s_0}$                 | assign $b = 1$ ;<br>assign $c = \sim s1$ ;                                                               |

|                                      | assign $d = \sim s0;$                                                                                    |

| $e = \overline{s_0}$                 | assign $e = \sim s0;$                                                                                    |

|                                      | assign f = $\sim$ s1 & $\sim$ s0;                                                                        |

| $f = \overline{s_1}  \overline{s_0}$ | assign $g = s1 \& \sim s0;$                                                                              |

|                                      |                                                                                                          |

| $g = s_1 \overline{s_0}$             | endmodule                                                                                                |

[Figure 2.46 from the textbook]

Top-level module

| // An adder module<br><b>module</b> adder (a, b, s1, s0)                        | <pre>// A module for driving a 7-segmen<br/>module display (s1, s0, a, b, c, d, e<br/>input s1, s0;</pre> |                                                                                 |

|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| <b>input</b> a, b;                                                              | <b>output</b> a, b, c, d, e, f, g;                                                                        | <b>module</b> adder_display (x, y, a, b, c, d, e, f,                            |

| <b>output</b> s1, s0;<br><b>assign</b> s1 = a & b;<br><b>assign</b> s0 = a ^ b; | assign $a = \sim s0;$<br>assign $b = 1;$<br>assign $c = \sim s1;$<br>assign $d = \sim s0;$                | <b>input</b> x, y;<br><b>output</b> a, b, c, d, e, f, g;<br><b>wire</b> w1, w0; |

| endmodule                                                                       | assign $e = \sim s0;$<br>assign $f = \sim s1 \& \sim s0;$<br>assign $g = s1 \& \sim s0;$                  | adder U1 (x, y, w1, w0);<br>display U2 (w1, w0, a, b, c, d, e, f, g);           |

|                                                                                 | endmodule                                                                                                 | endmodule                                                                       |

g);

Top-level module

| <pre>// An adder module module adder (a, b, s1, s0) input a, b;</pre>           | <pre>// A module for driving a 7-segment display<br/>module display (s1, s0, a, b, c, d, e, f, g);<br/>input s1, s0;<br/>output a, b, c, d, e, f, g;</pre> | y<br><b>nodule</b> adder_                  |

|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| <b>output</b> s1, s0;<br><b>assign</b> s1 = a & b;<br><b>assign</b> s0 = a ^ b; | assign $a = \sim s0$ ;<br>assign $b = 1$ ;<br>assign $c = \sim s1$ ;<br>assign $d = \sim s0$ ;                                                             | input x, y;<br>output a, b,<br>wire w1, w( |

| endmodule                                                                       | assign $e = -s0$ ;<br>assign $f = -s1 \& -s0$ ;<br>assign $g = s1 \& -s0$ ;                                                                                | adder U1 (x<br>display U2 (                |

endmodule

**module** adder\_display (x, y, a, b, c, d, e, f, g);

**input** x, y; **output** a, b, c, d, e, f, g; **wire** w1, w0;

adder U1 (x, y, w1, w0); display U2 (w1, w0, a, b, c, d, e, f, g);

Top-level module

| // An adder module                                                | // A module for driving a 7-segment                                                                         | display                 |

|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------|

| <b>module</b> adder (a, b, s1, s0)<br><b>input</b> a, b;          | <b>module</b> display (s1, s0, a, b, c, d, e,<br><b>input</b> s1, s0;<br><b>output</b> a, b, c, d, e, f, g; | f, g);<br><b>modu</b> l |

| output s1, s0;                                                    | <b>assign</b> $a = \sim s0;$                                                                                | inp                     |

| <b>assign</b> $s1 = a \& b$ ;<br><b>assign</b> $s0 = a \land b$ ; | assign $b = 1$ ;<br>assign $c = \sim s1$ ;<br>assign $d = \sim s0$ ;                                        | out<br>wir              |

|                                                                   | assign $e = -s0;$<br>assign $f = -s1 \& -s0;$                                                               | add                     |

| endmodule                                                         | assign $g = s1 \& \sim s0;$                                                                                 | disp                    |

**module** adder\_display (x, y, a, b, c, d, e, f, g);

**input** x, y; **output** a, b, c, d, e, f, g; **wire** w1, w0;

adder U1 (x, y, w1, w0); display U2 (w1, w0, a, b, c, d, e, f, g);

endmodule

Top-level module

```

// An adder module

// A module for driving a 7-segment display

module display (s1, s0, a, b, c, d, e, f, g);

module adder (a, b, s1, s0)

input s1, s0;

input a, b;

output a, b, c, d, e, f, g;

module adder_display (x, y, a, b, c, d, e, f, g);

output s1, s0;

input x, y;

assign a = \sim s0;

output a, b, c, d, e, f, g;

assign b = 1;

variables of type wire

assign s1 = a \& b;

wire w1, w0;

assign c = \sim s1;

(neither input nor output)

assign s0 = a^{h} b;

assign d = \sim s0;

adder U1 (x, y, w1, w0);

assign e = \sim s0;

assign f = \sim s1 \& \sim s0;

display U2 (w1, w0, a, b, c, d, e, f, g);

endmodule

assign g = s1 \& \sim s0;

endmodule

```

Top-level module

```

// An adder module

// A module for driving a 7-segment display

module display (s1, s0, a, b, c, d, e, f, g);

module adder (a, b, s1, s0)

input s1, s0;

input a, b;

output a, b, c, d, e, f, g;

module adder_display (x, y, a, b, c, d, e, f, g);

output s1, s0;

input x, y;

assign a = \sim s0;

output a, b, c, d, e, f, g;

assign b = 1;

must be computed

assign s1 = a \& b;

wire w1, w0;

assign c = \sim s1;

all the time, unlike reg

assign s0 = a^{h} b;

assign d = \sim s0;

adder U1 (x, y, w1, w0);

assign e = \sim s0;

assign f = \sim s1 \& \sim s0;

display U2 (w1, w0, a, b, c, d, e, f, g);

endmodule

assign g = s1 \& \sim s0;

endmodule

```

Top-level module

```

// An adder module

// A module for driving a 7-segment display

module display (s1, s0, a, b, c, d, e, f, g);

module adder (a, b, s1, s0)

input s1, s0;

input a, b;

output a, b, c, d, e, f, g;

module adder_display (x, y, a, b, c, d, e, f, g);

output s1, s0;

input x, y;

assign a = \sim s0;

output a, b, c, d, e, f, g;

assign b = 1;

assign s1 = a \& b;

wire w1, w0;

assign c = \sim s1;

assign s0 = a^{h} b;

assign d = \sim s0;

adder U1 (x, y, w1, w0);

assign e = \sim s0;

assign f = \sim s1 \& \sim s0;

display U2 (w1, w0, a, b, c, d, e, f, g);

endmodule

assign g = s1 \& \sim s0;

endmodule

```

Top-level module

| // An adder module                                                              | // A module for driving a 7-segme                                                              | nt display                                                                      |

|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| <b>module</b> adder (a, b, s1, s0)                                              | <b>module</b> display (s1, s0, a, b, c, d, <b>input</b> s1, s0;                                | e, f, g);                                                                       |

| input a, b;                                                                     | <b>output</b> a, b, c, d, e, f, g;                                                             | <b>module</b> adder_display (x, y, a, b, c, d, e, f, g);                        |

| <b>output</b> s1, s0;<br><b>assign</b> s1 = a & b;<br><b>assign</b> s0 = a ^ b; | assign $a = \sim s0$ ;<br>assign $b = 1$ ;<br>assign $c = \sim s1$ ;<br>assign $d = \sim s0$ ; | <b>input</b> x, y;<br><b>output</b> a, b, c, d, e, f, g;<br><b>wire</b> w1, w0; |

| endmodule                                                                       | assign $e = \sim s0$ ;<br>assign $f = \sim s1 \& \sim s0$ ;<br>assign $g = s1 \& \sim s0$ ;    | adder U1 (x, y, w1, w0);<br>display U2 (w1, w0, a, b, c, d, e, f, g);           |

|                                                                                 | endmodule                                                                                      | endmodule                                                                       |

## **Questions?**

## THE END