# CprE / ComS 583 Reconfigurable Computing

Prof. Joseph Zambreno Department of Electrical and Computer Engineering Iowa State University

Lecture #3 - FPGA Basics

#### Recap

- FPGAs spatial computation

- · CPU temporal computation

- · FPGAs are by their nature more computationally "dense" than CPU

- In terms of number of computations / time / area

- · Can be quantitatively measured and compared

- · Capacity, cost, ease of programming still important issues

- · Numerous challenges to reconfiguration

# Outline

- Recap

- FPGA Taxonomy

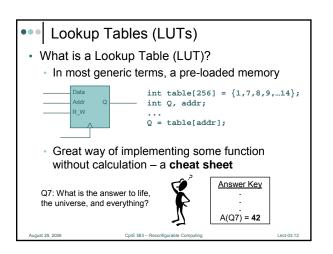

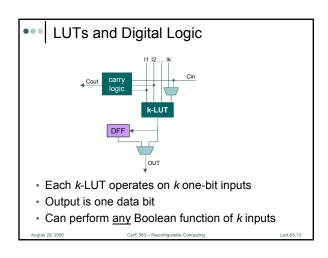

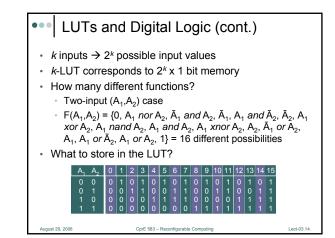

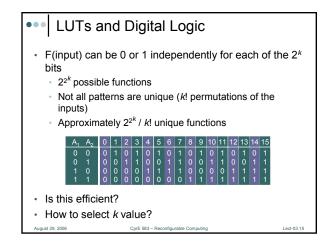

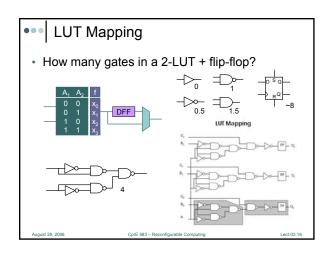

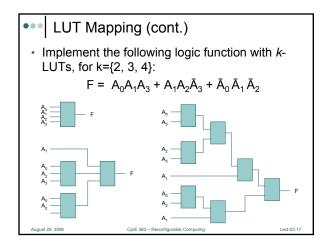

- · Lookup Tables and Digital Logic

- · Interconnect / Routing Structures

- FPGA Architectural Issues

#### **FPGA Taxonomy**

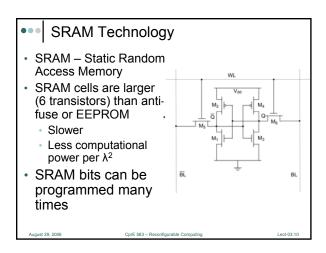

- Programming technology how is the FPGA programmed? Where does it store configuration bits?

SRAM

- Anti-fuse

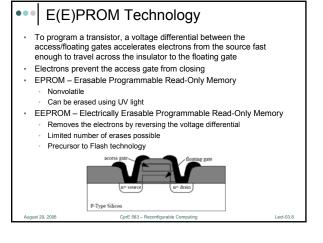

- **EPROM**

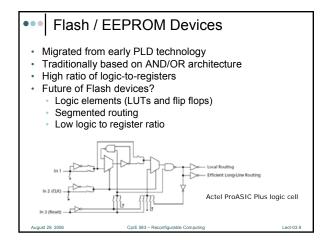

- Flash memory (EEPROM)

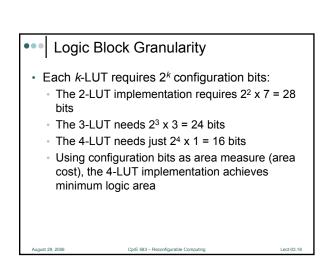

- Logic cell architecture what is the granularity of configurable component? Tradeoff between complexity and versitility

- Transistors

- Gates

- PAL/PLAs LUTs

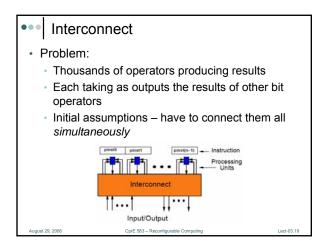

- Interconnect architecture how do the logic cells communicate?

- Tiled

- Hierarchical

- Local

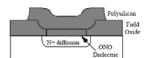

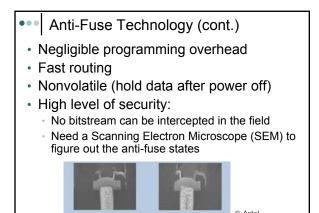

# Anti-Fuse Technology

- · Dielectric that prevents current flow

- · Applying a voltage melts the dielectric

• One time programmable – not really reconfigurable computing

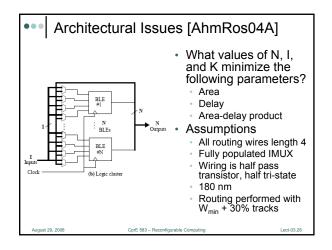

- Flexibility route anything (within reason?)

- Bisection bandwidth

- · Simultaneous routes

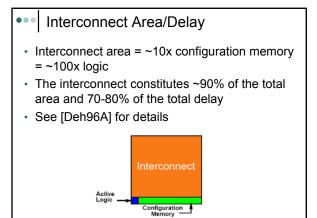

- Area

- · Bisection bandwidth

- Switches

- Delay (and Power)

- Switches in path

- · Wire length

- · Routability difficulty of finding a route

unuet 20, 2006

CprE 583 - Reconfigurable Computing

Lect-03 20

# ••• General Routing Architecture

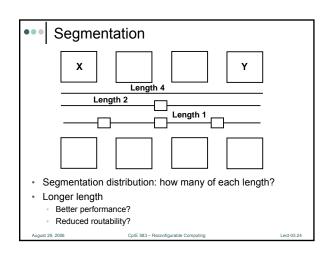

- A wire segment is a wire unbroken by programmable switches

- Typically one switch is attached to each end of a wire segment

- A track is a sequence of one or more wire segments in a line

- · A routing channel is a group of parallel tracks

- A connection block provides connectivity from the inputs and outputs of a logic block to the wire segments in the channels

August 29, 200

CprE 583 – Reconfigurable Computing

Lect-03.2

# ••• Attempt 1 – Crossbar

- Any operator may want to take as input the output of any other operator

- Let n be the number of LUTs, and / the length of wire

- Delay:

- Parasitic loads = kn Switches/path = I Wire length = O(kn) Delay = O(kn)

- Area:

- Bisection BW = n Switches = kn<sup>2</sup> Area = O(n<sup>2</sup>)

CprE 583 – Reconfigurable Computing

Lect-03.22

# Attempt 2 – Mesh Put connected components together Transitive fan-in grows faster than the close sites: Let w be the channel width Delay: Switches/path = I Wire length = O(I) Best Delay = O(w) Worst Delay = O(m<sup>2</sup>w) Area: Bisection BW = wn<sup>1/2</sup> Switches = O(nw<sup>2</sup>) Area = O(nw<sup>2</sup>) Area = O(nw<sup>2</sup>) Area = O(nw<sup>2</sup>) Area = O(mw<sup>2</sup>) Area

# ••• Summary

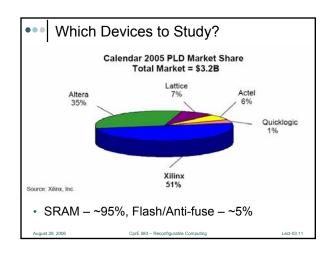

- · Three basic types of FPGA devices

- Antifuse

- EEPROM

- SRAM

- Key issues for SRAM FPGA are logic cluster, connection box, and switch box.

- Most tasks have structure, which can be exploited by LUT arrays with programmable interconnect (FPGAs)

- Cannot afford full interconnect, or make all interconnects local

August 29, 2006

CprE 583 – Reconfigurable Computing

Lect-03.2