### Outline

- Recap

- · Placement and Routing Metrics

- FPGA Placement Techniques

- Iterative partitioning

- Simulated annealing

- FPGA Routing Techniques

October 5, 200

CprE 583 – Reconfigurable Computing

. . . . . . .

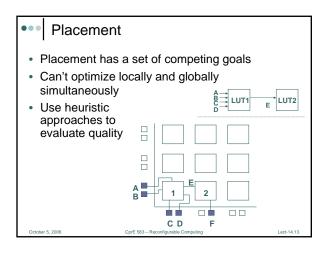

### ••• Placement and Routing

- · Two critical phases of layout design:

- · Placement of components on the chip

- Routing of wires between components

- Placement and routing interact, but separating layout design into phases helps us understand the problem and find good solutions

October 5, 2006

CprE 583 - Reconfigurable Con

### Placement Metrics

- · Quality metrics for layout:

- Area

- Delay

- Power

- · Area and delay determined partly by wiring

- How do we judge a placement without wiring?

- Estimate wire length without actually performing routing

- · Design time may be important for FPGAs

October 5, 20

CprE 583 – Reconfigurable Computing

.ect-14.9

### FPGA Issues

- · Often want a fast answer

- May be willing to accept lower quality result for less place/route time

- May be interested in knowing wirability without needing the final configuration

- Fast placement: constructive placement, iterative improvement through simulated annealing

October 5, 2

CprE 583 – Reconfigurable Computing

Lect-14.10

# Wire Length as a Quality Metric Bad Placement Good Placement Cotober 5, 2008 CprE 583 - Reconfigurable Computing Lect-14.11

### Wire Length Measures Estimate wire length by distance between components Possible distance measures: Euclidean distance (sqrt(x² + y²)) Manhattan distance (x + y) Multi-point nets must be broken up into trees for good estimates

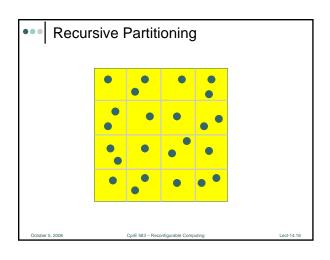

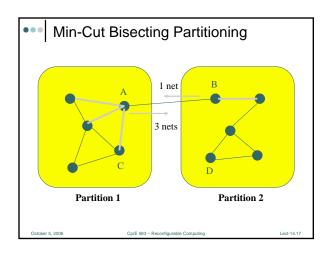

# Placement by Partitioning Works well for components of fairly uniform size Partition netlist to minimize total wire length using min-cut criterion Partitioning may be interpreted as 1-D or 2-D layout

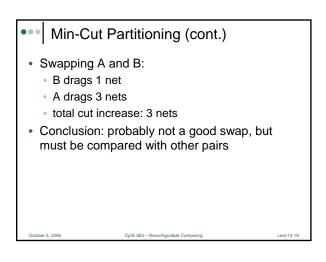

### Kernighan-Lin Algorithm

- · Compute min cut criterion:

- Count total net cut change

- Algorithm exchanges sets of nodes to perform hill-climbing—finding improvements where no single swap will improve the cut

- Recursively subdivide to determine placement detail

### Kernighan-Lin Algorithm (cont.)

- Make an initial guess partition into two subsets of equal sizes, and unlock all the vertices in the graph

- Associate a cost D with every vertex i, where D(i) = E(i) - I(i)

- I(i) is the number of edges that do not cross the bisection boundary

- E(i) is the number of edges that cross the boundary

- 3. Calculate the gain G for all possible swaps between unlocked vertices a and b

- $G(a_i,b_i) = D(a_i) + D(b_i) 2C(a_i, b_i)$

- C(a<sub>i</sub>, b<sub>i</sub>) is the weight of the edge between (a<sub>i</sub>,b<sub>i</sub>)

- Make the swap for the max G, and lock the nodes

- Iterate until no more swaps can be made

CprE 583 - Reconfigu

### In-Class Exercise

· Step through Kernighan-Lin on the following circuit:

### Simulated Annealing

- Powerful but CPU-intensive optimization technique

- Analogy to annealing of metals:

- · Temperature determines probability of a component jumping position

- Probabilistically accept moves

- · Start at high temperature, cool to lower temperature to try to reach good placement

### Physical Annealing Analogy

- Take a metal and heat to high temperature

- · Allow it to cool slowly; metal is annealed to a low temperature

- · Atoms in the metal are at lower energy states after annealing

- · Higher the temperature initially and slower the cooling, the tougher the metal becomes

- Atoms transition to high energy states and then move to low energy

### Simulated Annealing (cont.)

- Generate random moves

- Initially, accept moves that decrease and increase cost

- Local minimum versus global minimum

- · As temperature decreases, the probability of accepting bad moves decreases

- Eventually, default to greedy algorithm

### Annealing Wrap-up

- · Big-hammer for hard optimization problems

- · General cost model accommodates most any constraints

- · If cool slowly enough, will get good results

- Finesse in working out parameters

- · Cost should be cheap to update

- · Annealing schedule can be tricky to optimize (balance speed versus quality)

- · ...generally takes a long time... (...why PPR is slow)

### Imagine ... (Routing)

- · You have to plan transportation (i.e. roads and highways) for a new city the size of Chicago

- Many dwellings need direct roads that can't be used by anyone else

- · You can affect the layout of houses and neighborhoods but the architects and planners will complain

- And ... you're told that the time along any path can't be longer than a fixed amount

- What are some of your considerations?

### Some Considerations

- How many levels do the roads need to go?

- · Remember: higher is more expensive

- · How to avoid congestion?

- · What basic structure do I want for my roads?

- Manhattan?

- · Chicago?

- Boston?

- · Automated routing tools have to solve problems of comparable complexity on every leading-edge chip

### Routing Sub-Problems

- Shortest Path (two-pin nets O(N<sub>3</sub>))

- Steiner Tree (easy for *n*-pin where  $n \le 5$ : NPcomplete in general)

- Compatibility (NP-complete)

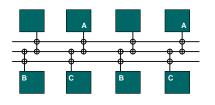

### Routing Compatibility

- · Example: satisfy three simultaneous net connections (A-A, B-B, C-C)

- A-A cannot use middle track

- · Greedy approach will not be sufficient

Standard Approach

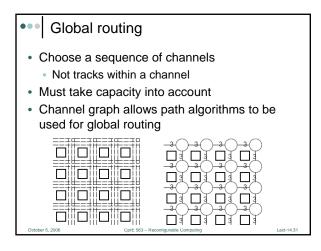

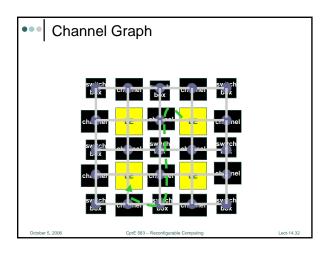

- Major phases in routing:

- Global routing assigns nets to routing areas

- Detailed routing designs the routing areas

- One phase routers channel assignment and wire selection happens in one routing pass

- Two phase routers were initially popular

- Simpler to write and faster to execute

- More closely models ASIC routing techniques

- One phase routers shown to give MUCH better performance

- Net ordering is a major problem

- Order in which nets are routed determines quality of

- Net ordering is a heuristic

### ••• Summary

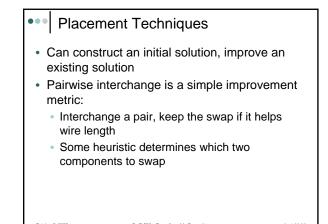

- Placement

- Placement and clustering of modules critically important for subsequent routing step

- Often initial placement performed and then iteratively improved

- Mincut partitioning approaches sometimes used for initial placement

- Can benefit from simulated annealing approaches, given an accurate cost function

- Routing

- Routing a difficult problem based on device size, complexity

- · Hard part of routing is the compatibility problem

- Can be attacked using iterative or simulated annealing approaches

October 5, 2006

CprE 583 – Reconfigurable Computing

Lect-14.35