## CprE / ComS 583 Reconfigurable Computing

Prof. Joseph Zambreno Department of Electrical and Computer Engineering Iowa State University

Lecture #18 -VHDL for Synthesis I

```

Recap - 4:1 Multiplexer

LIBRARY ieee:

USE ieee.std_logic_1164.all;

ENTITY mux4to1 IS

PORT (w0, w1, w2, w3: IN

STD_LOGIC;

STD_LOGIC_VECTOR(1 DOWNTO 0)

:OUT STD_LOGIC);

END mux4to1:

ARCHITECTURE dataflow OF mux4to1 IS

BEGIN

WITH s SELECT

f <= w0 WHEN "00",

w1 WHEN "01",

w2 WHEN "10"

w3 WHEN OTHERS;

END dataflow;

```

```

PROCESS (Resetn, Clock )

BEGIN

PROCESS (Resetn, Clock )

BEGIN

IF Resetn = '0' THEN

Q <= (OTHERS ⇒> '0');

END PROCESS;

END PROCESS PROCESS;

END PROCESS PROC

```

```

Recap – 4-bit Up-Counter with Reset

ARCHITECTURE Behavior OF upcount IS

SIGNAL Count: STD_LOGIC_VECTOR (3 DOWNTO 0);

PROCESS (Clock, Resetn)

BEGIN

IF Resetn = '0' THEN

Count <= "0000" ;

ELSIF (Clock'EVENT AND Clock = '1') THEN

IF Enable = '1' THEN

Count <= Count + 1;

END IF

Enable

END PROCESS;

Q <= Count;

Clock

END Behavior;

Resetn

```

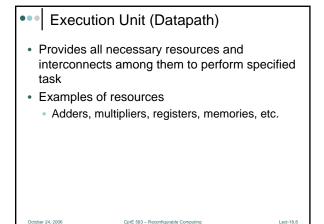

#### Design Exercise

- Design a simple 32-bit CPU

- Requirements

- Three instruction types: load/store, register ALU, branch-if-equal

- 8 32-bit registers

- ALU operations: ADD, SUB, OR, XOR, AND, CMP

- Memory operations: load word, store word

- Components

- · Instruction memory / decode

- Register file

- ALŪ

- Data memory

- Other control

October 24, 2006 CprE 583 – Reconfigurable Computing Lect-

#### ••• Outline

- Recap

- Finite State Machines

- Moore Machines

- Mealy Machines

- FSMs in VHDL

- State Encoding

- Example Systems

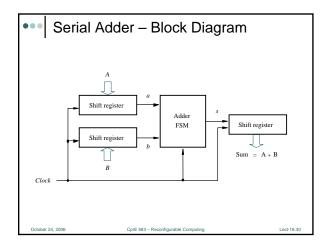

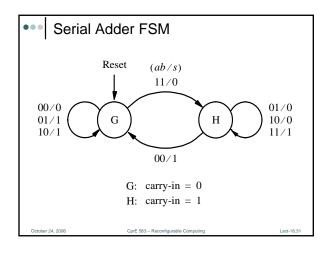

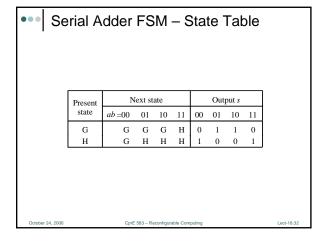

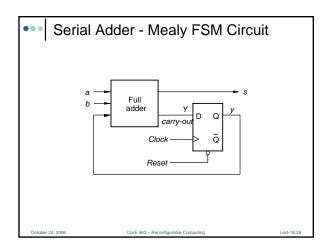

- Serial Adder

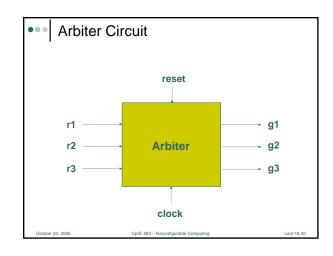

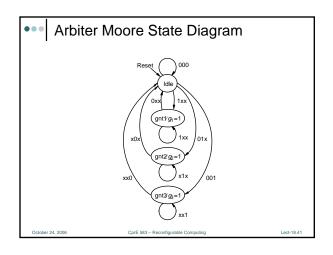

- Arbiter Circuit

Incher 24, 2006 CorF 583 – Reconfigurable Computing Lect-18.6

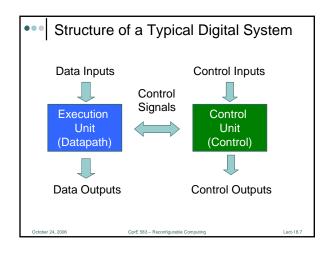

#### Control Unit (Control)

- Controls data movements in operational circuit by switching multiplexers and enabling or disabling resources

- · Follows some 'program' or schedule

- Often implemented as Finite State Machine or collection of Finite State Machines

October 24, 2006

orE 583 – Reconfigurable Computing

••• Finite State Machines (FSMs)

- Any circuit with memory Is a Finite State Machine

- Even computers can be viewed as huge FSMs

- Design of FSMs involves

- Defining states

- Defining transitions between states

- Optimization / minimization

- Above approach is practical for small FSMs only

October 24, 20

CprE 583 – Reconfigurable Computing

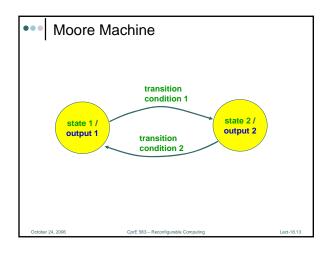

• Output is a function of present state only

Inputs

Next State

function

Next State

function

Present State

Register

Output

Gutput

Gutputs

Function

Outputs

Outputs

Outputs

Lect-18.11

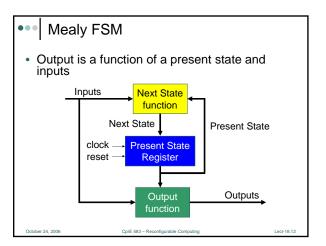

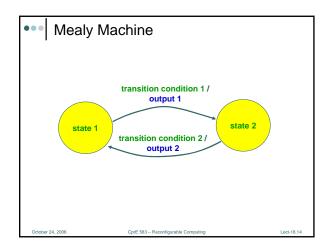

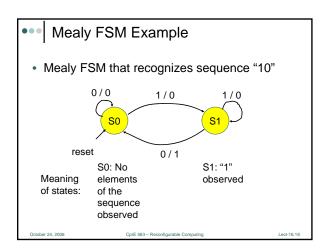

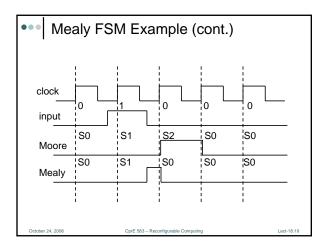

#### Moore vs. Mealy FSM

- Moore and Mealy FSMs can be functionally equivalent

- Equivalent Mealy FSM can be derived from Moore FSM and vice versa

- Mealy FSM has richer description and usually requires smaller number of states

- Smaller circuit area

ober 24, 2006 CprE 583 – Reconfigur

Lect-18.15

#### ••• Moore vs. Mealy FSM (cont.)

- Mealy FSM computes outputs as soon as inputs change

- Mealy FSM responds one clock cycle sooner than equivalent Moore FSM

- Moore FSM has no combinational path between inputs and outputs

- Moore FSM is more likely to have a shorter critical path

er 24, 2006 CprE 583 – Reconfigurable Computing

#### ••• FSMs in VHDL

- Finite State Machines can be easily described with processes

- Synthesis tools understand FSM description if certain rules are followed

- State transitions should be described in a process sensitive to clock and asynchronous reset signals only

- Outputs described as concurrent statements outside the process

```

Moore FSM Example – VHDL

TYPE state IS (S0, S1, S2);

SIGNAL Moore_state: state;

U_Moore: PROCESS (clock, reset)

BEGIN

IF(reset = '1') THEN

Moore_state <= S0;

ELSIF (clock = '1' AND clock'event) THEN

CASE Moore_state IS

WHEN S0 =>

IF input = '1' THEN

Moore_state <= S1;

ELSE

Moore_state <= S0;

END IF;

October 24, 2006

CptE 583 – Reconfigurable Computing

```

```

Moore FSM Example — VHDL (cont.)

WHEN S1 =>

IF input = '0' THEN

Moore_state <= S2;

ELSE

Moore_state <= S1;

END IF;

WHEN S2 =>

IF input = '0' THEN

Moore_state <= S0;

ELSE

Moore_state <= S0;

ELSE

Moore_state <= S1;

END IF;

END CASE;

END IF;

END CASE;

END IF;

END PROCESS;

Output <= '1' WHEN Moore_state = S2 ELSE '0';

```

```

Mealy FSM Example — VHDL (cont.)

WHEN S1 =>

IF input = '0' THEN

Mealy_state <= $0;

ELSE

Mealy_state <= $1;

END IF;

END CASE;

END IF;

END PROCESS;

Output <= '1' WHEN (Mealy_state = $1 AND input = '0') ELSE '0';

```

#### State Encoding Problem

- State encoding can have a big influence on optimality of the FSM implementation

- No methods other than checking all possible encodings are known to produce optimal circuit

- · Feasible for small circuits only

- Using enumerated types for states in VHDL leaves encoding problem for synthesis tool

October 24, 2006

CprE 583 - Reconfigurable Computing

#### Types of State Encodings

- Binary (Sequential) States encoded as consecutive binary numbers

- Small number of used flip-flops

- Potentially complex transition functions leading to slow implementations

- One-Hot only one bit Is active

- Number of used flip-flops as big as number of states

- Simple and fast transition functions

- · Preferable coding technique in FPGAs

October 24, 2006

OprE 583 - Reconfigurable Computing

### ••• Types of State Encodings (cont.)

| State | Binary Code | One-Hot Code |

|-------|-------------|--------------|

| S0    | 000         | 10000000     |

| S1    | 001         | 01000000     |

| S2    | 010         | 00100000     |

| S3    | 011         | 00010000     |

| S4    | 100         | 00001000     |

| S5    | 101         | 00000100     |

| S6    | 110         | 0000010      |

| S7    | 111         | 0000001      |

October 24, 2006

orE 583 – Reconfigurable Computing

```

Manual State Assignment

(ENTITY declaration not shown)

ARCHITECTURE Behavior OF simple IS

TYPE State_type IS (A, B, C);

ATTRIBUTE ENUM_ENCODING

ATTRIBUTE ENUM_ENCODING OF State_type

SIGNAL y_present, y_next: State_type;

BEGIN

cont ...

October 24, 2006

CprE 583 – Reconfigurable Computing

Lect-18.28

```

# ARCHITECTURE Behavior OF simple IS SUBTYPE ABC\_STATE is STD\_LOGIC\_VECTOR(1 DOWNTO 0); CONSTANT A: ABC\_STATE := "00":

Manual State Assignment (cont.)

```

CONSTANT A : ABC_STATE := "00" ;

CONSTANT B : ABC_STATE := "01" ;

CONSTANT C : ABC_STATE := "11" ;

SIGNAL y_present, y_next : ABC_STATE;

BEGIN

PROCESS (w, y_present)

BEGIN

CASE y_present IS

WHEN A =>

IF w = '0' THEN y_next <= A ;

ELSE y_next <= B ;

END IF ;

... cont

```

```

Serial Adder - Entity Declaration

1 LIBRARY ieee;

2 USE ieee.std_logic_1164.all;

3 ENTITY serial IS

4 GENERIC (length: INTEGER:= 8);

5 PORT ( Clock : IN STD_LOGIC;

6 Reset : IN STD_LOGIC;

7 A, B : IN STD_LOGIC;

9 END serial;

October 24, 2006 CprE 583 - Reconfigurable Computing Lect-18.33

```

```

Serial Adder — Architecture (2)

10 ARCHITECTURE Behavior OF serial IS

11 COMPONENT shiftrne

12 GENERIC (N: INTEGER: = 4);

13 PORT (R: IN STD_LOGIC_VECTOR(N-1 DOWNTO 0);

14 L.E, W: IN STD_LOGIC;

15 Clock: IN STD_LOGIC;

16 Q: BUFFER STD_LOGIC_VECTOR(N-1 DOWNTO 0));

17 END COMPONENT;

18 SIGNAL QA, QB, Null_in: STD_LOGIC_VECTOR(length-1 DOWNTO 0);

19 SIGNAL S, Low, High, Run: STD_LOGIC;

20 SIGNAL Count: INTEGER RANGE 0 TO length;

21 TYPE State_type IS (G, H);

22 SIGNAL y: State_type;

```

```

Serial Adder — Architecture (3)

23 BEGIN

24 Low <= '0'; High <= '1';

25 ShiftA: shiftme GENERIC MAP (N => length)

26 PORT MAP (A, Reset, High, Low, Clock, QA);

27 ShiftB: shiftme GENERIC MAP (N => length)

28 PORT MAP (B, Reset, High, Low, Clock, QB);

Cotober 24, 2006 CprE 583 – Reconfigurable Computing Lect-18.35

```

```

Serial Adder — Architecture (5)

52 Stop: PROCESS

53 BEGIN

54 WAIT UNTIL (Clock'EVENT AND Clock = '1');

55 IF Reset = '1' THEN

56 Count <= length;

57 ELSIF Run = '1' THEN

58 Count <= Count -1;

59 END IF;

60 END PROCESS;

61 Run <= '0' WHEN Count = 0 ELSE '1'; -- stops counter and ShiftSum

62 END Behavior;

October 24, 2006 CprE 583 – Reconfigurable Computing

```

```

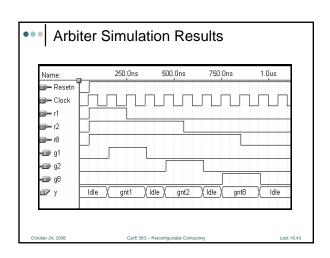

Grant Signals — VHDL Code

...

PROCESS( y )

BEGIN

g(1) <= '0';

g(2) <= '0';

g(3) <= '0';

IF y = gnt1 THEN g(1) <= '1';

ELSIF y = gnt2 THEN g(2) <= '1';

ELSIF y = gnt3 THEN g(3) <= '1';

END IF;

END IF;

END PROCESS;

END Behavior;

Coccober 24, 2006

CptE 583 - Reconfigurable Computing

Lect-18.42

```